# Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-22-2018

# Energy Demand Response for High-Performance Computing Systems

Kishwar Ahmed Florida International University, kahme006@fiu.edu

**DOI:** 10.25148/etd.FIDC006527

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Contracts Commons, <u>Digital Communications and Networking Commons</u>, and the <u>Power and Energy Commons</u>

#### Recommended Citation

Ahmed, Kishwar, "Energy Demand Response for High-Performance Computing Systems" (2018). FIU Electronic Theses and Dissertations. 3569.

https://digitalcommons.fiu.edu/etd/3569

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

## FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# ENERGY DEMAND RESPONSE FOR HIGH-PERFORMANCE COMPUTING SYSTEMS

A dissertation submitted in partial fulfillment of the requirements for the degree of  ${\color{blue} {\rm DOCTOR~OF~PHILOSOPHY}}$

in

COMPUTER SCIENCE

by

Kishwar Ahmed

To: Dean John L. Volakis

College of Engineering and Computing

This dissertation, written by Kishwar Ahmed, and entitled Energy Demand Response for High-Performance Computing Systems, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

| S. S. Iyengar                                                                                      |

|----------------------------------------------------------------------------------------------------|

| Deng Pan                                                                                           |

|                                                                                                    |

| Leonardo Bobadilla                                                                                 |

| Wujie Wen                                                                                          |

| Jason Liu, Major Professor                                                                         |

| Date of Defense: March 22, 2018                                                                    |

| The dissertation of Kishwar Ahmed is approved.                                                     |

|                                                                                                    |

| Dean John L. Volakis College of Engineering and Computing                                          |

|                                                                                                    |

| Andres G. Gil                                                                                      |

| Vice President for Research and Economic Development and<br>Dean of the University Graduate School |

Florida International University, 2018

© Copyright 2018 by Kishwar Ahmed All rights reserved.

# DEDICATION

To my parents and my wife.

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the guidance and help of my advisor, Dr. Jason Liu. In spite of his very busy schedule, he made every effort to guide me throughout the entire process. I am really grateful to him for his tremendous support, and no word of gratitude is sufficient to convey it.

I am also thankful to my committee members, Dr. S. S. Iyengar, Dr. Deng Pan, Dr. Leonardo Bobadilla, and Dr. Wujie Wen for their valuable suggestions regarding my dissertation. I am grateful to Dr. Stephan Eidenbenz and Dr. Nandakishore Santhi from Los Alamos National Laboratory, Dr. Xingfu Wu from Argonne National Laboratory, and Dr. Jesse Bull from Florida International University for their constructive suggestions and contributions on my dissertation. I also want to thank Kazutomo Yoshii, Dr. Rob Ross, and Dr. Misbah Mubarak for the opportunity to work with them at Argonne National Laboratory as an intern. Their valuable guidance and help have benefited me a lot in my doctoral study. I would like to thank Mohammad Atiqul Islam, with whom I collaborated during first few years of my doctoral study.

My utmost gratitude goes to my parents Erfanuddin Ahmed and Shaheda Begum. With their encouragement and valuable suggestions, I have been able to reach this far. My wife, Samia Tasnim, has accompanied throughout my doctoral journey. Her love, care and support have propelled me through the difficult times of doctoral study. I owe her everything. I am grateful to my brother, Shaer Ahmed, who gave inspiration at various times. I would also like to thank my friends Mohammad Chowdhury, Mohammad Obaida, Naeemul Hassan, Tanay Kumar Saha, Jesun Feroz for giving me much-needed breaks during exhausting research times.

#### ABSTRACT OF THE DISSERTATION

# ENERGY DEMAND RESPONSE FOR HIGH-PERFORMANCE COMPUTING SYSTEMS

by

#### Kishwar Ahmed

Florida International University, 2018

Miami, Florida

Professor Jason Liu, Major Professor

The growing computational demand of scientific applications has greatly motivated the development of large-scale high-performance computing (HPC) systems in the past decade. To accommodate the increasing demand of applications, HPC systems have been going through dramatic architectural changes (e.g., introduction of many-core and multi-core systems, rapid growth of complex interconnection network for efficient communication between thousands of nodes), as well as significant increase in size (e.g., modern supercomputers consist of hundreds of thousands of nodes). With such changes in architecture and size, the energy consumption by these systems has increased significantly. With the advent of exascale supercomputers in the next few years, power consumption of the HPC systems will surely increase; some systems may even consume hundreds of megawatts of electricity. Demand response programs are designed to help the energy service providers to stabilize the power system by reducing the energy consumption of participating systems during the time periods of high demand power usage or temporary shortage in power supply.

This dissertation focuses on developing energy-efficient demand-response models and algorithms to enable HPC system's demand response participation. In the first part, we present interconnection network models for performance prediction of large-scale HPC applications. They are based on interconnected topologies widely used in HPC systems: dragonfly, torus, and fat-tree. Our interconnect models are fully integrated with an implementation of message-passing interface (MPI) that can mimic most of its functions with packet-level accuracy. Extensive experiments show that our integrated models provide good accuracy for predicting the network behavior, while at the same time allowing for good parallel scaling performance. In the second part, we present an energy-efficient demand-response model to reduce HPC systems' energy consumption during demand response periods. We propose HPC job scheduling and resource provisioning schemes to enable HPC system's emergency demand response participation. In the final part, we propose an economic demand-response model to allow both HPC operator and HPC users to jointly reduce HPC system's energy cost. Our proposed model allows the participation of HPC systems in economic demand-response programs through a contract-based rewarding scheme that can incentivize HPC users to participate in demand response.

# TABLE OF CONTENTS

| CHAPTER                                                           | PAGE |

|-------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                   | 1    |

| 1.1 Motivation                                                    | 1    |

| 1.2 Problem Definition and Contributions                          |      |

| 1.2.1 Rapid Performance Modeling for HPC Systems                  | 3    |

| 1.2.2 Emergency Demand Response for HPC Systems                   |      |

| 1.2.3 Economic Demand Response for HPC Systems                    |      |

| 1.3 Related Publications                                          |      |

| 1.4 Outline of the Dissertation                                   |      |

| 2. BACKGROUND                                                     | 13   |

| 2.1 Performance Prediction Models                                 | 13   |

| 2.1.1 Interconnection Network                                     |      |

| 2.1.2 Memory System                                               | 18   |

| 2.1.3 Processor System                                            |      |

| 2.1.4 HPC Applications                                            | 23   |

| 2.2 HPC Power Models                                              | 25   |

| 3. RAPID PERFORMANCE MODELING FOR HPC SYSTEMS                     | 28   |

| 3.1 Background                                                    |      |

| 3.2 Related Work                                                  |      |

| 3.3 Model                                                         | 34   |

| 3.3.1 MPI Model                                                   | 36   |

| 3.3.2 Interconnection Network Models                              | 41   |

| 3.3.3 Interconnect Model Validations                              | 49   |

| 3.4 Experiments                                                   | 59   |

| 3.4.1 Trace-Driven MPI Simulation                                 | 59   |

| 3.4.2 SNAP Performance Study                                      |      |

| 3.4.3 Parallel Performance                                        | 67   |

| 3.5 Summary                                                       | 69   |

| 4. EMERGENCY DEMAND RESPONSE FOR HPC SYSTEMS                      | 70   |

| 4.1 Background                                                    | 70   |

| 4.2 Related Work                                                  | 72   |

| 4.3 Demand-Response Model Based on Frequency Scaling              | 76   |

| 4.3.1 Power and Performance Prediction Models                     | 76   |

| 4.3.2 Job Scheduling and Resource Provisioning                    | 79   |

| 4.3.3 Determining Optimal Frequency                               | 86   |

| 4.3.4 Job Eviction                                                |      |

| 4.3.5 Performance Evaluation                                      |      |

| 4.4 Demand-Response Model Based on Power Capping and Node Scaling | 95   |

| 4.4.1 Exploiting Power-Capping Property                        |

|----------------------------------------------------------------|

| 4.4.2 Exploiting Power-Capping and Node-Scaling Properties 102 |

| 4.4.3 Performance Evaluation                                   |

| 4.5 Summary                                                    |

| 5. ECONOMIC DEMAND RESPONSE FOR HPC SYSTEMS                    |

| 5.1 Background                                                 |

| 5.2 Related Work                                               |

| 5.2.1 Reducing Energy Cost                                     |

| 5.2.2 Demand Response                                          |

| 5.2.3 Contract Theory and Applications                         |

| 5.3 Model                                                      |

| 5.3.1 An Example                                               |

| 5.3.2 HPC System Model                                         |

| 5.4 Formulation and Algorithm                                  |

| 5.4.1 Feasibility and Optimality of Solutions                  |

| 5.4.2 Contract Design with Continuum Type                      |

| 5.5 Experiments                                                |

| 5.5.1 Data Set                                                 |

| 5.5.2 Energy Reduction and Utility                             |

| 5.5.3 Benchmark Comparison                                     |

| 5.6 Summary                                                    |

| C. CONCLUCIONO                                                 |

| 6. CONCLUSIONS                                                 |

| 6.1 Summary                                                    |

| 6.2 Future Directions                                          |

| BIBLIOGRAPHY                                                   |

| VITA 168                                                       |

# LIST OF FIGURES

| FIGU | JRE PA                                                                                                                                           | AGE |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

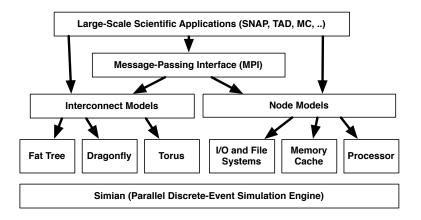

| 3.1  | An architectural design of PPT                                                                                                                   | 35  |

| 3.2  | An example showing running 16 MPI processes on Hopper                                                                                            | 39  |

| 3.3  | Simulating Cannon's matrix multiplication                                                                                                        | 40  |

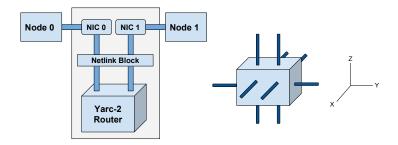

| 3.4  | Cray Gemini ASIC block diagram                                                                                                                   | 42  |

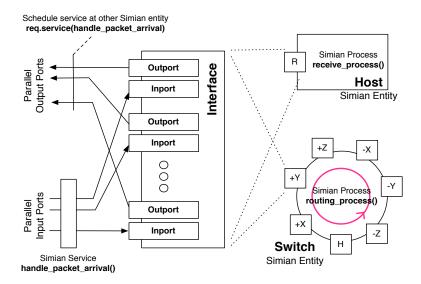

| 3.5  | Interconnect model using Simian entities, processes, and services                                                                                | 43  |

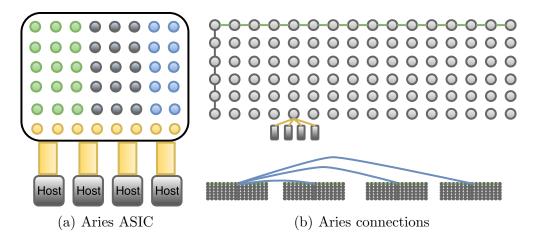

| 3.6  | Cray Aries block diagram                                                                                                                         | 47  |

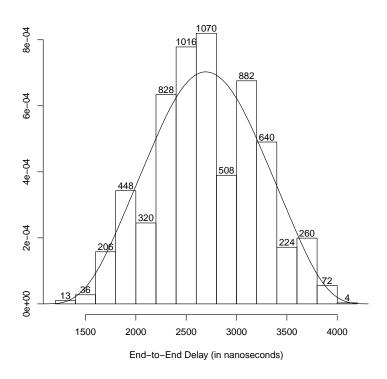

| 3.7  | A histogram of end-to-end delay between compute nodes of the simulated HPC cluster                                                               | 52  |

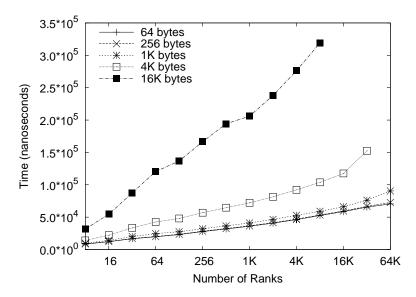

| 3.8  | Duration of the MPI_Allreduce call for different number of ranks and data size on the simulated HPC cluster                                      | 53  |

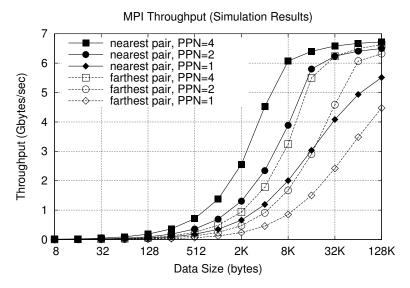

| 3.9  | MPI throughput from simulation as a function of message size for 1, 2 and 4 MPI processes per node                                               | 54  |

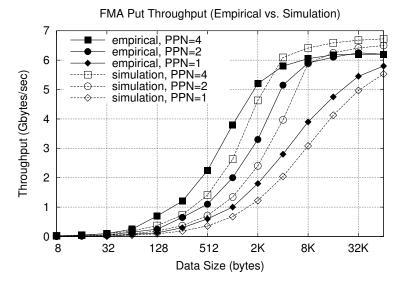

| 3.10 | Gemini FMA put throughput (as reported in [ARK10]) versus simulated throughput as a function of transfer size for 1, 2, and 4 processes per node | 55  |

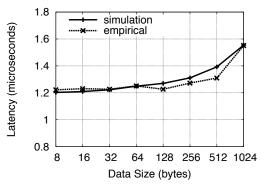

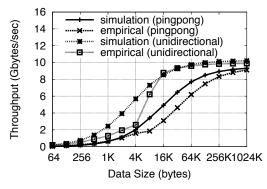

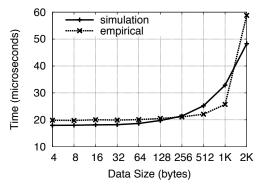

| 3.11 | Aries validation                                                                                                                                 | 56  |

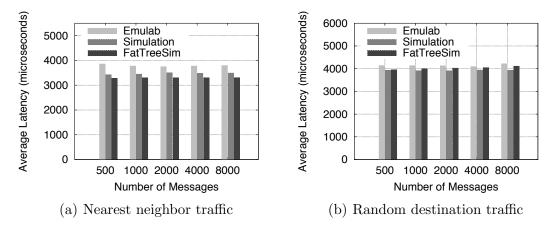

| 3.12 | Comparison with FatTreeSim and Emulab                                                                                                            | 58  |

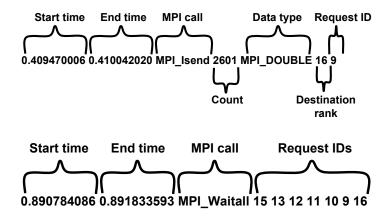

| 3.13 | Format of MPI calls in the processed trace file (there is one trace file for each MPI rank)                                                      | 60  |

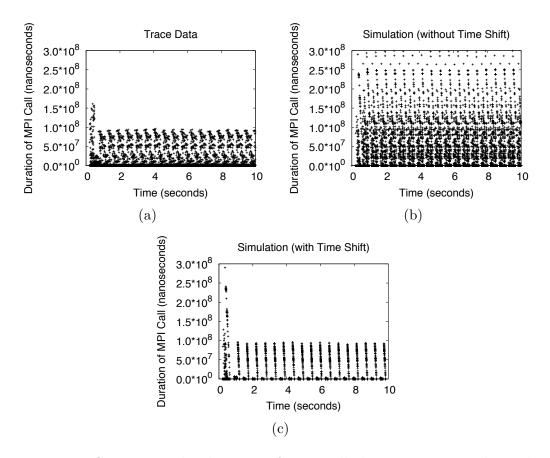

| 3.14 | Comparing the duration of MPI calls between trace and simulation with and without time shift                                                     | 62  |

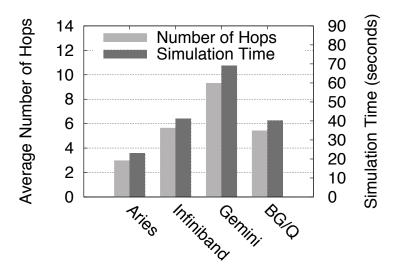

| 3.15 | Comparison of different architectures for trace-based run                                                                                        | 64  |

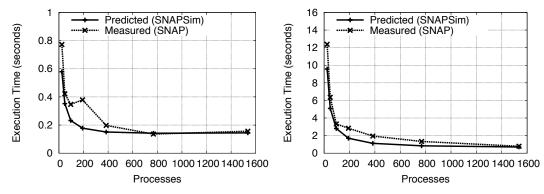

| 3.16 | SNAPSim vs. SNAP Edison strong scaling                                                                                                           | 66  |

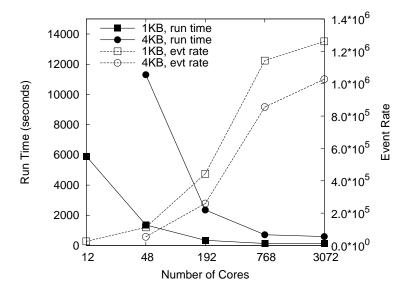

| 3.17 | Observed run time and event rate for running Simian with an 156K-rank MPI model on a parallel compute cluster                                    | 68  |

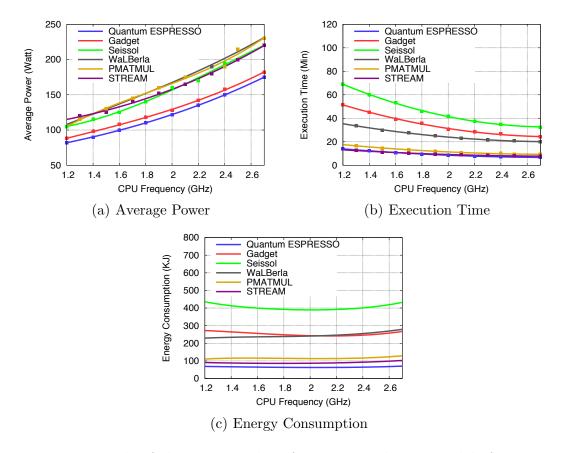

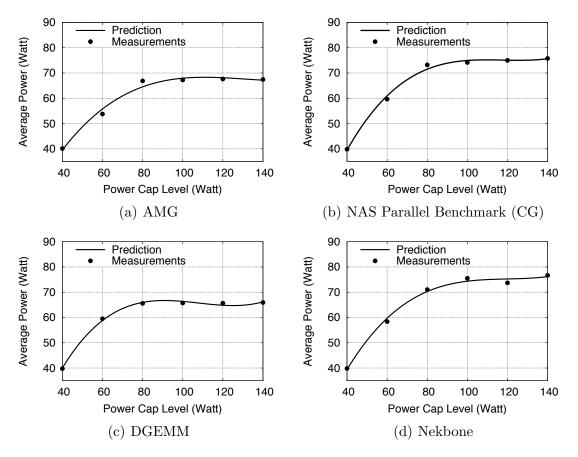

| 4.1  | Result of the power and performance prediction models for six HPC applications                                                                   | 78  |

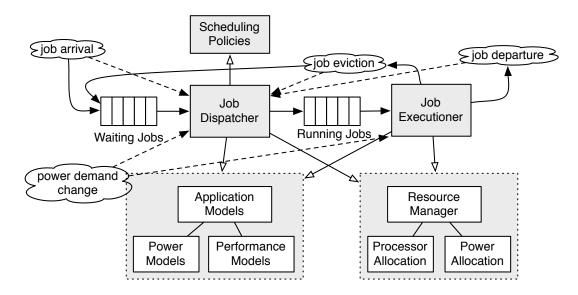

| 4.2  | The overall design of our job scheduler simulator                                                                                                | 84  |

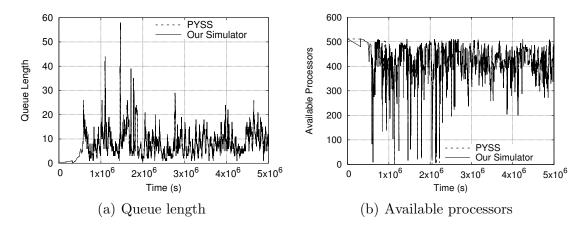

| 4.3  | Comparing results from PYSS and our simulator                                                                                                    | 86  |

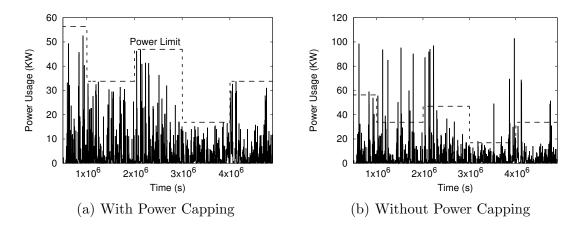

| 4.4  | Power usage over time with and without power capping 90                                             |

|------|-----------------------------------------------------------------------------------------------------|

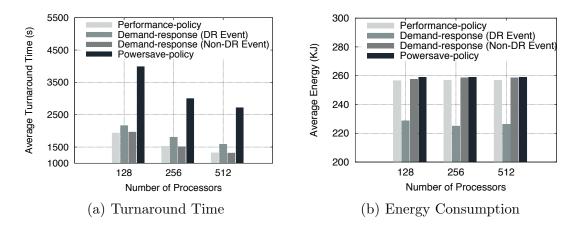

| 4.5  | Comparing performance and energy for different scheduling policies and with different system size   |

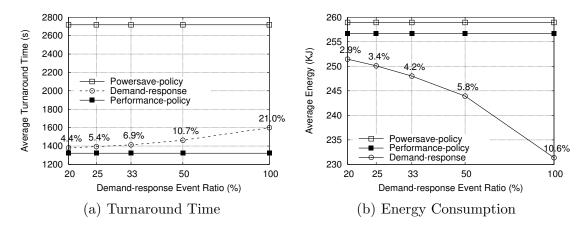

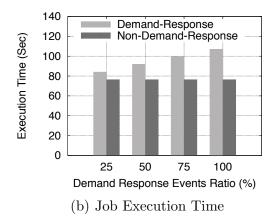

| 4.6  | Impact on the demand response event ratio                                                           |

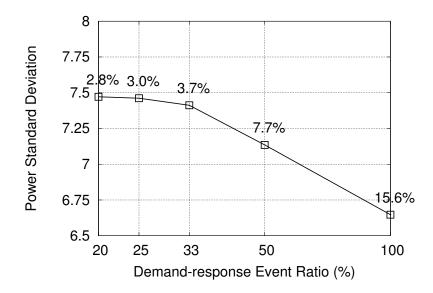

| 4.7  | Power stability during the demand response periods                                                  |

| 4.8  | Impact of power capping on application characteristics 96                                           |

| 4.9  | Power regression model for different applications                                                   |

| 4.10 | Runtime regression model for different applications                                                 |

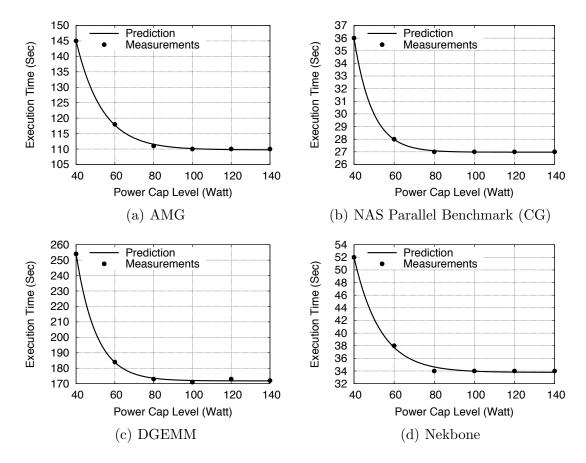

| 4.11 | Node scaling model for different applications                                                       |

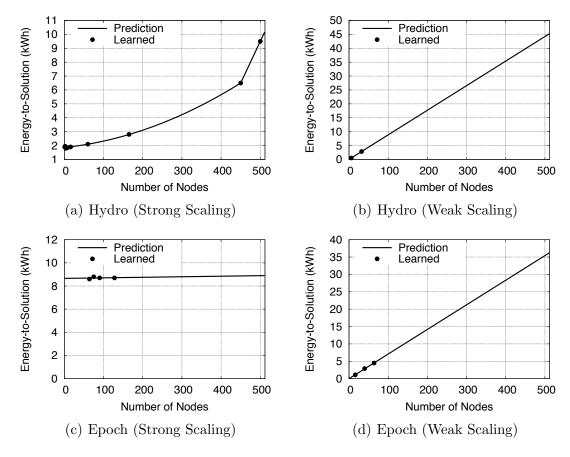

| 4.12 | Benchmark comparison with power capping                                                             |

| 4.13 | Benchmark comparison with power capping and node scaling 107                                        |

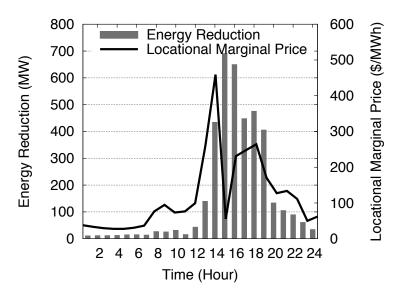

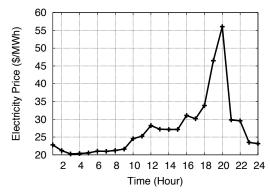

| 5.1  | Energy reduction and electricity pricing from PJM economic demand response on July 18, 2013 [PJM17] |

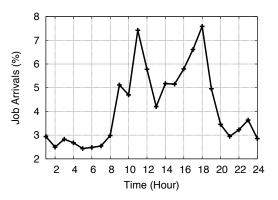

| 5.2  | Job arrivals and electricity price data                                                             |

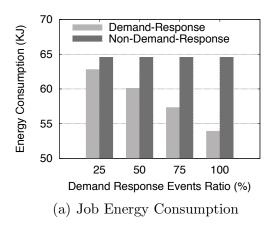

| 5.3  | Energy reduction and utility                                                                        |

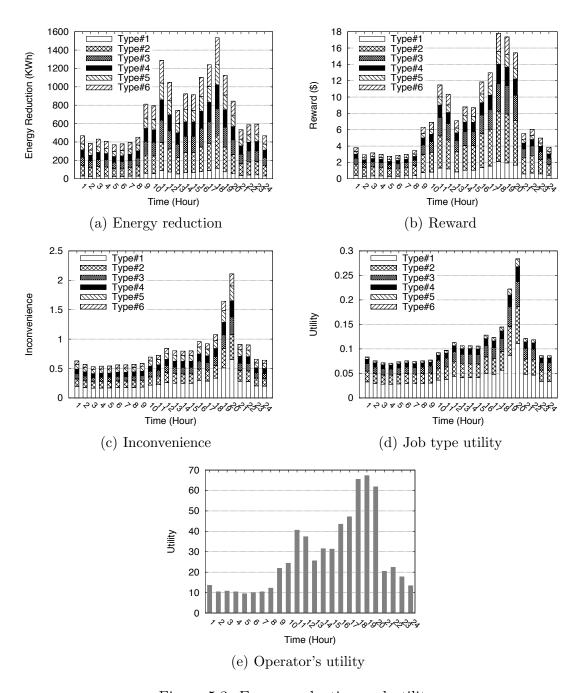

| 5.4  | Incentive compatibility constraint                                                                  |

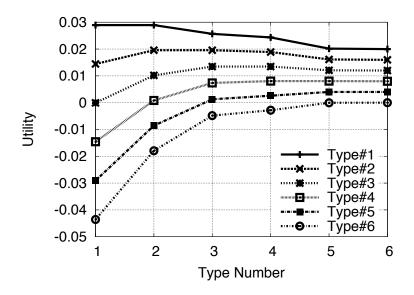

| 5.5  | Benchmark comparison                                                                                |

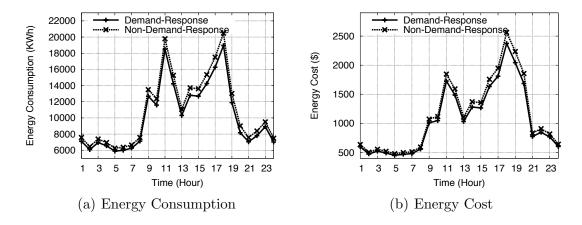

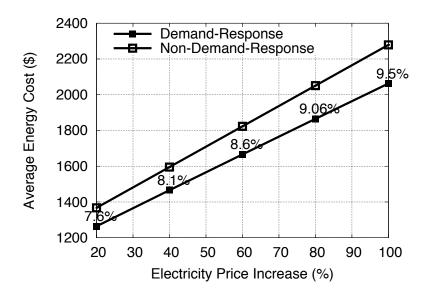

| 5.6  | Change in electricity price                                                                         |

#### CHAPTER 1

#### INTRODUCTION

### 1.1 Motivation

High-performance computing (HPC) systems, such as petaflops supercomputers, can consume a tremendous amount of power. For example, as of November 2016, China's 34-petaflops Tianhe-2 supercomputer, which currently consumes the most power in the list of top 500 supercomputers [TOP16], has been reported to consume almost 18 MWs of power, sufficient to power a small town of 20,000 residences. With the advent of exascale supercomputers in the next few years, power consumption of the HPC systems will surely increase: a recent projection indicates that an exascale system would reach 60-130 MWs of power [YZW+13]. The massive power consumption of these HPC systems can expound significant stress for the power grid. HPC has also shown significant fluctuations in the power consumption due to the varying job execution profiles and also sporadic maintenance schedules. Effective power saving and power stabilizing methods must be seriously considered when building future HPC systems.

Demand response programs are designed to help the energy service providers to stabilize the power system by reducing the energy consumption of participating systems when the power grid becomes unstable due to a sudden rise in power demand or other emergency incidents. Demand response can be broadly categorized into two types: economic demand response and emergency demand response. In economic demand response, participants voluntarily enroll in the programs (without the need of prior commitment) and willingly reduce the load based on economic incentives offered by the supplier. Emergency demand response requires prior commitment from the participants; once enrolled, it is mandatory for the participants to reduce the

energy consumption to requested levels when supply shortage situations or emergency conditions occur. The U.S. Department of Energy (DoE) and the National Institute of Standards and Technology (NIST) have identified demand response as one of the important policy goals to achieve power grid efficiency [HBH14, Fed16]. In addition to monetary benefits, demand response can also provide the associated environmental benefits, such as reducing carbon emission [PJM14]. We have observed a recent increase in the participation of the demand response programs in various sectors [The13, McA17]. Recent projection also shows that there will be substantial growth in the coming years—an anticipated doubling of the overall participation in the demand response programs in 2020 has been projected [ME13]. Motivated by an increase in popularity of demand response program participation and massive energy consumption of HPC systems, this dissertation aims to explore the opportunity of HPC systems' energy consumption reduction through emergency and economic demand response participation.

To enable HPC systems' demand response participation, we need to analyze the power-performance tradeoff of HPC applications, and develop detailed performance prediction models for HPC systems containing thousands of nodes. The rapid advancement towards exascale computing has led to the emergence of novel hardware architecture designs in HPC systems that include accelerator technologies (such as GPUs), high core-count compute nodes with shared memory, deep instruction pipelines, deep memory hierarchies with aggressive memory prefetching strategies, and sophisticated branch prediction for speculative execution. These new architectural features enable massive parallelism and latency hiding that in principle allow software and codes to scale to next-generation HPC systems. For example, Intel's Knight's Corner node features 61 cores with shared main memory (albeit at a non-uniform access speed) that enables thread-level parallelism.

In contrast, NVIDIA's Tesla GPU accelerators have up to 3,000 CUDA Cores per CPU enabling vector parallelism. Different parallelization strategies were adopted in these cases. CPU-based nodes use a significant fraction of their chip real estate to implement pipelining logic (to enable instruction-level parallelism) and memory prefetching logic at different cache levels (to enable latency hiding), whereas GPU designs tend to maximize core counts with arithmetic logic units (ALUs) for enabling vector parallelism. These novel hardware technologies have turned out to be disruptive to existing software portfolios in many industries and government branches because simple re-compilation does not exploit these features very well. This in turn has led to massive code re-factoring in many sectors, including—and perhaps most pronounced—among users of high-performance computational physics code. Performance prediction on how fast and how energy-efficient a code will run on a platform is at the heart of computational co-design.

# 1.2 Problem Definition and Contributions

The primary goal of this dissertation is to identify the key challenges and explore the power and performance modeling to enable HPC system's demand response participation.

### 1.2.1 Rapid Performance Modeling for HPC Systems

With frequent changes in HPC systems, it is imperative that performance prediction of future HPC systems is properly realized. Of particular importance is the model for the interconnection networks as it is critical to the understanding of the communication cost and thus the performance limitations of large-scale applications on high-performance computing infrastructures. Such large-scale interconnection

network models allow performance prediction of HPC applications on many nodes, and therefore enable analysis of power-performance tradeoff of HPC applications. There has been significant research effort on performance prediction and modeling of extreme-scale interconnection networks (e.g., [LHSJ15, LC11, Per10, PP14]). However, few of these research efforts consider the effect of complex, dynamic application behaviors, such as computational physics code, on the underlying large-scale interconnection network.

The Performance Prediction Toolkit (PPT) is a DOE co-design project that aims at developing a comprehensive prediction capability for computational physics code, algorithms and methods that perform on novel hardware architectures, thus enabling fast adoption of new code by quickly identifying and ruling out unsuccessful refactoring schemes. PPT models both hardware and software at levels of abstraction that are appropriate to the concrete question at hand, by applying a mix of discrete-event simulation, stochastic and analytical models at various layers on the software and hardware stack. PPT relies on Simian [SEL15], a parallel discrete-event simulation engine, and essentially consists of libraries of hardware models, application models, and middleware models. PPT, along with Simian, is designed to be lean, written in Python (or alternatively Lua) with minimal reliance on third-party libraries in an effort to keep the code simple, understandable, and yet offer high performance.

**Contributions.** Our contributions to performance modeling of large-scale HPC system are summarized below:

1. We present PPT's interconnection network models to model communication among many nodes in HPC systems and predict performance of HPC applications. Our interconnection network models include widely-used interconnect topologies with emphasis on production networks (both existing and planned

interconnection networks). In today's top-ranked HPC systems, we see three common network types: torus (e.g., Cray's Gemini, IBM's Blue Gene/Q), dragonfly (e.g., Cray's Aries), and fat-tree (e.g., Infiniband). They constitute a majority of the production network topologies. Our survey on the latest supercomputers (http://www.top500.org, June 2016) shows that the three topologies account for 54% of the 500 fastest supercomputers in the world (44% for fast ethernet and 2% proprietary). Among the top 100 supercomputers, the three topologies grow up to 82%. 14 of the top 15 ranked supercomputers are interconnected by the three types. In PPT, separate interconnection network models have been developed and carefully parameterized in PPT to capture various production interconnection networks. We present sufficiently detailed interconnection models for Cray's Gemini 3-D torus, IBM's Blue Gene/Q 5-D torus, Cray's Aries dragonfly, and Infiniband's fat-tree network.

2. PPT's interconnection network models are packet-level models, where network transactions (e.g., for MPI send/receive and for collective operations) are modeled as discrete events representing individual packets (typically, around 64 bytes in size) being transferred by the network switches and compute nodes. This is a conscious design decision. Our hypothesis is that in most scenarios, packet-level simulation should be sufficient to capture major network behaviors (throughput, delay, loss, and network congestion) with sufficient accuracy, and as such, should be able to identify potential performance bottlenecks at the interconnection networks while running large-scale scientific applications. Compared to more detailed models, such as those implemented at the phit level (virtual channels), packet-level simulation can easily outperform detailed models by several orders of magnitude. We present extensive validation studies of our MPI and interconnect models, including a trace-based study using

- data obtained from executing real-life computational physics code on an existing high-performance computing platform. Our experiments suggest that our packet-level models can provide sufficient accuracy.

- 3. PPT's interconnection network models can be easily incorporated with the application models. Our interconnection network models interface with the message-passing interface (MPI) model. MPI is the most commonly used parallel programming tools for scientific applications on modern HPC platforms. Our MPI model provides convenient methods for deploying the parallel applications and performing communications on the target parallel platform. We have implemented all common MPI functions, including point-to-point communications (both blocking and asynchronous methods) and collective operations (such as gather/scatter, barriers, broadcast, reduce, and all-to-all). In addition, we implemented MPI groups and communicators so that collective communications can take place among an arbitrary subset of processes. As a result, most scientific applications can be simulated directly using the communication functions provided by the MPI model.

- 4. We conduct extensive validation study of our interconnect models, including a trace-driven simulation of real-life scientific application communication patterns. We also perform performance study of a computational physics-based parallel application using our interconnect model. All the results show that our interconnect models provide reasonably good accuracy. Moreover, we study the parallel performance of our integrated models on large-scale HPC platforms and show good parallel scaling performance.

## 1.2.2 Emergency Demand Response for HPC Systems

Being a massive energy consumer of the power grid, the HPC sector can contribute toward ensuring grid stability and energy reduction through its participation in the demand response programs. Recent research has studied the feasibility and identified the associated challenges in the HPC demand response [BGA<sup>+</sup>15, PBG<sup>+</sup>16]. Patki et al. [PBG<sup>+</sup>16] suggested that supercomputing systems in the U.S. may be willing to participate in the demand response programs if tighter and more frequent communications can be established between the supercomputing centers and their energy service providers. Patki's study is based on a qualitative analysis of cooperative demand-management strategies. We note, however, that there is no related work on the job scheduling and resource provisioning strategies at HPC centers that can operate with demand response. Various energy-efficient HPC job scheduling algorithms (e.g., [SLGK14, PLS+15, ECLV12]) and resource provisioning methods (e.g., [GFFC07, LM06, BHC<sup>+</sup>16]) have been proposed in the literature. These studies aim at reducing the overall energy consumption of the HPC systems, but do not consider demand response. In this dissertation, we explore the opportunities of the HPC centers participating in the demand response programs through a study of detailed job scheduling and resource provisioning strategies.

Contributions. Our contributions to power modeling in terms of emergency demand response participation from HPC systems are summarized below:

1. We propose an HPC job scheduling and resource provisioning algorithm for demand response. For job scheduling, we assume first-come-first-serve (FCFS) with possible job eviction and restart in response to the reduced power level during the demand response periods. For resource provisioning, we dynamically scale the frequency of the processors in order to achieve optimal en-

ergy conservation and power stability during the demand response periods. During normal periods, the processors in HPC systems operate at maximum frequency for best performance. Also, we develop a simulator for job scheduling and resource provisioning to study the effect of demand response. The simulator is built upon a parallel discrete-event simulation engine capable for handling large-scale models. The simulator has been validated using real-life HPC workload traces.

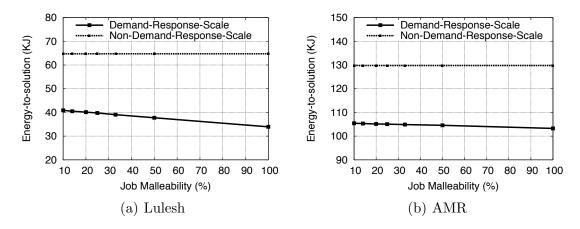

- 2. We exploit the power-capping capability in the modern processors to enable HPC system emergency demand response participation. We present prediction models for power and performance prediction with respect to different power-capping values. We propose a demand response participation model for HPC systems based on the prediction models with power capping. We extend the HPC system demand response model by exploiting job malleability. We incorporate an energy-to-solution prediction model to the demand response model in order to determine the optimal job size and power-capping values.

- 3. We conduct extensive trace-based simulation studies to show the effectiveness of the proposed job scheduling and resource provisioning algorithm for demand response. The results demonstrate that our proposed approach is a viable solution for attracting supercomputing centers to participate in the demand response programs as it can improve power stability and energy reduction with only moderate increase in execution time for the jobs. Moreover, we perform experiments using real-life scientific applications on an existing cluster to measure application performance and power usage under different power-capping values. Using these measurements, we use trace-based simulation to show the effectiveness of our proposed demand-response model and compare it with power-capping policies implemented in processors.

#### 1.2.3 Economic Demand Response for HPC Systems

Demand response program anticipates customers to reduce energy consumption upon requests from the power utility companies during the time periods of high demand power usage or temporary shortage in power supply. Customers are willing to participate in demand response programs in expectation to receive financial or operational benefits from the utility companies. Overall, demand response has become increasingly popular among power utility companies. Revenue earnings from demand response has increased significantly in recent years. For example, a report from PJM Interconnection (a large utility company servicing many states in the U.S.) shows that it has achieved an earning of \$650 million from various demand response participation in 2016, a significant increase from only about \$50 million in 2006 [PJM17]. Much of this growth can be attributed to the economic demand response programs using incentives provided via fluctuations in electricity pricing, through which the power utility companies can signal the consumers to adapt their behaviors at various time granularities (such as hourly). In the final part of this dissertation, we address how to reduce energy cost in HPC systems through a contract-based economic demand response participation.

#### **Contributions.** Our contributions are summarized below:

- 1. We propose an economic demand response participation model for HPC systems for energy reduction. We propose a rewarding scheme to be offered by the HPC operator to the HPC users based on contract design to encourage the willing participation of the users in demand response.

- 2. Our analyses demonstrate that the proposed contract-based demand response mechanism preserves important properties of the contract theory, including individual rationality (IR), incentive compatibility (IC), and monotonicity.

3. Through trace-based simulation, we provide the empirical evidence of our proposed approach and further demonstrate the effectiveness of our proposed mechanism compared to other existing approaches. The simulation experiments also support our analytical claims in practice.

#### 1.3 Related Publications

This dissertation is drawn from the following publications:

- Kishwar Ahmed, Jason Liu, and Kazutomo Yoshii. Enabling Demand Response for HPC Systems Through Power Capping and Node Scaling. Submitted to IEEE International Conference on High Performance Computing and Communications (HPCC), 2018.

- Kishwar Ahmed, Jesse Bull, and Jason Liu. Contract-Based Demand Response Model for HPC Systems. Submitted to International Conference on Parallel Processing (ICPP), 2018.

- Kishwar Ahmed, Jason Liu, Abdel-Hameed Badawy, and Stephan Eidenbenz.

A Brief History of HPC Simulation and Future Challenges. In 2017 Winter Simulation Conference (WSC), pages 419-430. IEEE, 2017.

- Kishwar Ahmed, Jason Liu, and Xingfu Wu. An Energy Efficient Demand-Response Model for High Performance Computing Systems. In 2017 IEEE 25th International Symposium on Modeling, Analysis, and Simulation of Computer and Telecommunication Systems (MASCOTS), pages 175-186. IEEE, 2017.

- Kishwar Ahmed, Jason Liu, Stephan Eidenbenz, and Joe Zerr. Scalable interconnection network models for rapid performance prediction of HPC applica-

- tions. In High Performance Computing and Communications (HPCC), 2016 IEEE 18th International Conference on, pages 1069-1078. IEEE, 2016.

- Kishwar Ahmed, Mohammad Obaida, Jason Liu, Stephan Eidenbenz, Nandakishore Santhi, and Guillaume Chapuis. An integrated interconnection network

model for large-scale performance prediction. In Proceedings of the 2016 ACM

SIGSIM Conference on Principles of Advanced Discrete Simulation (PADS),

pages 177-187. ACM, 2016.

## 1.4 Outline of the Dissertation

We discuss the background and related work in Chapter 2. We first provide a snapshot of the existing performance prediction models and simulators in Section 2.1. We consider models for different sub-systems, including processors, memory, and interconnection networks. We also discuss application models that can capture the runtime behavior of the large-scale scientific applications. We discuss analytical models and tools for energy and power prediction of the HPC systems in Section 2.2.

We present how to model HPC applications' performance on underlying architecture, and present our rapid performance prediction models for large-scale interconnection network in Chapter 3. Section 3.1 discusses background information and challenges. Section 3.2 describes related works and compares our approach with the existing methods. Section 3.3 provides an overview of our design. In the same section, we also provide the MPI model and the details of our torus, dragonfly, and fat-tree interconnection network models (along with validations). In Section 3.4, we present trace-driven simulation of real-life scientific application communication patterns, as well as performance study of a computational physics-based parallel application using one of our interconnect models.

Chapter 4 describes our approach to address HPC system's massive power consumption and presents our energy-efficient emergency demand-response models for HPC systems. We present background information and contributions in Section 4.1. In Section 4.2, we describe related work and compare the existing approaches with our proposed method. In Section 4.3, we explore the opportunities of the HPC systems participating in the emergency demand programs through a study of detailed job scheduling and resource provisioning strategies. In Section 4.4, we exploit the power-capping property in the modern processors and node scaling of HPC applications to enable HPC system emergency demand response participation.

Chapter 5 presents our economic demand-response model for HPC systems. Section 5.1 discusses background information and challenges. Section 5.2 describes related works and compares our approach with the existing methods. Section 5.3 describes the contract-based HPC economic demand response participation model. In Section 5.4, we present the problem formulation and corresponding algorithm. We also describe the necessary conditions for contract design mechanisms in the same section. In Section 5.5, we use real-life data to show effectiveness of our proposed solution. Finally, we present our concluding remarks and provide direction for future work in Chapter 6.

#### CHAPTER 2

#### BACKGROUND

#### 2.1 Performance Prediction Models

HPC systems today consist of hundreds of thousands of compute nodes, and can perform tens or hundreds of quadrillion floating point operations per second [Tsa13, Cou16]). HPC architectures have gone through rapid changes to facilitate the increasing computational demand of scientific applications in many areas, such as astrophysics, particle physics, earth and climate science, computational chemistry, computational biology, and so on. Novel technologies, for example, many-core processors, GPUs, persistent memory, and complex interconnection networks, have been introduced constantly to fulfill the increasing scale and performance of such systems. With the changing hardware architectures also comes the changing software design and implementation of scientific applications in order to take best advantage of the new computing resources.

Modeling and simulation plays an important role for performance prediction and analysis of current and future HPC systems. It can be particularly useful for evaluating the whole-system impact when new components are introduced, for comparing the performance of different system design alternatives, and for locating performance issues of computational code on novel HPC platforms even before their realization. It is thus not surprising to see many HPC models and simulation tools created in the past for exactly the same purposes. They model the HPC systems at different granularity: some are created to study specific components of the HPC systems (processors, memory, interconnect, storage, and so on), and others are meant for studying the overall system performance in aggregate. The important difference lies

in the accuracy-performance trade-off that has been applied to effectively capture the salient features of the target system.

#### 2.1.1 Interconnection Network

HPC interconnection network offers a systematic way to connect compute nodes, processors, memory, and storage units. Important aspects of an interconnection network model include accurate representation of the network topology, routing, resource scheduling (such as flow control), and network queuing. Different interconnection network topologies exist in current HPC systems, including fat-tree (e.g., IBM's Infiniband), torus (e.g., IBM's Blue Gene/Q, Cray's Gemini), and dragonfly (e.g., Cray's Aries). An accurate model of these interconnection networks is important for us to understand the communication cost as one of the most important constraints on the performance of scientific applications running on HPC systems.

BigSim [ZKK04] is an early effort for performance prediction of large-scale parallel machines (e.g., Blue Gene/L machines), based on the model of parallel applications on the target architecture (such as using MPI). The interconnection network models developed in BigSim are relatively simple as they do not consider network congestion [CGL<sup>+</sup>14]. BigSim is implemented using Charm++, an object-based and message-driven parallel programming system [KK93]. The simulator adopts optimistic parallel simulation for scalability, using inherent determinacy of the target parallel applications to reduce the synchronization overhead. Experiments show that BigSim is capable of scaling up to 64K simulated processors.

Structural Simulation Toolkit (SST) is an all-inclusive simulation framework for modeling large-scale HPC systems, including processors, memory, interconnection networks, and I/O systems [RHB+11]. SST consists of models of various hardware components with different levels of accuracy and granularity, and attempts to achieve

scalability by using conservative parallel simulation based on the "distance" between the system components. SST supports generic router models which can be used to build different network topologies, such as binary tree, fat-tree, hypercube, flattened 2-D butterfly, 2-D and 3-D mesh, and fully-connected graph. The interconnection network models in SST, however, do not support flow control between routers and the links between routers are assumed to have infinite capacity. SST is an ongoing project and is able to include active contributions of many advanced component models as part of a scalable and open-source simulation framework.

Extreme-scale Simulator (xSim) is a performance-prediction toolkit for future HPC architectures [EL10, BE11]. xSim applies parallel discrete-event simulation using lightweight threads and has achieved good scalability with millions of MPI ranks running a simple MPI program. [JE11] extended xSim to incorporate a network model with different topologies (star, ring, mesh, torus, and tree), and different hierarchical network combinations (such as network-on-chip and network-on-node). However, the xSim models do not consider traffic congestion or any detailed blocking behavior which can be important to applications on real interconnection networks.

$\mu\pi$  [Per10] is an MPI simulator built upon an efficient conservatively-synchronized parallel simulator that presents a feature-oriented world-view.  $\mu\pi$  supports simulation of large-scale MPI applications. Experiments show that it can run up to 27 million virtual MPI ranks on as many as 216,000 cores of a Cray XT5. More recently, Perumalla et. al. [PP14] proposed to extend  $\mu\pi$  and include direct execution to run even larger number of tasks. The simulator focus on MPI communication of applications, but does not contain any detailed interconnection network models.

Co-Design of Exascale Storage System (CODES) simulator is another comprehensive simulation platform to model various large-scale systems, including storage systems, interconnection networks, HPC and data center applications [CLL+11].

CODES provides detailed interconnect models for various interconnect topologies, including torus [LC11], dragonfly [MCRC14], and fat-tree [LHSJ15]. The simulator is built on Rensselaer Optimistic Simulation System (ROSS), a parallel discrete-event simulation engine using reverse computation [CBP02], and is capable of simulating very large interconnect configurations (with millions of nodes). Trace-driven capabilities have also been added to CODES to replay large execution traces for studying network performance [AJB<sup>+</sup>15].

Garnet [AKPJ09] is an on-chip interconnection network simulator, which builds upon the lacking of GEMS [MSB<sup>+</sup>05] and performs "detailed" interconnect communication between on-chip routers. Through modeling detailed router microarchitecture, Garnet is able to capture various details such as virtual channel arbitration and realistic link contention. Garnet has provision for easy-configuration of various parameters (e.g., different network topologies, interconnect bandwidth configuration through flit size, router parameters such as arbitrary number of input and output ports, various routing algorithms). TOPAZ [APM+12] is yet another open-source NoC simulator with broader analysis spectrum (e.g., tradeoffs between accuracy, simulation speed for various interconnection network). It has an easy incorporation capability with other simulation tools (e.g., GEMS and gem5) in runtime. TOPAZ is multithreaded, therefore providing more accurate prediction capability without compromising simulation execution time. In addition to being capable of simulating NoCs in multicore processors, TOPAZ also supports simulation of large-scale interconnection networks and is able to simulate networks consisting of millions of routers.

#### 2.1.1.1 A Parallel Discrete-Event Simulation Engine

All our initerconnection network models are developed based on Simian, which is an open-source, process-oriented parallel discrete-event simulation (PDES) engine [SEL15]. Simian has two independent implementations written in two interpreted languages, Python and Lua, respectively. Simian uses a conservative barrier-based synchronization algorithm [Nic93] for parallel execution.

Simian has several distinct features. First, Simian adopts a minimalistic design. For example, the Python implementation of Simian consists of only around 500 lines of code. As a result, it requires low effort to understand the code and it is thus easy for model development and debugging. Second, Simian features a very simplistic application programming interface (API). To maximize portability, Simian requires minimal dependency on third-party libraries. Third, Simian takes advantage of just-in-time (JIT) compilation for interpreted languages. For certain models, Simian has demonstrated capable of outperforming the C/C++ based simulation engine.

To develop models on Simian, it is necessary to understand the Simian API, which contains only three main modules: the simulation engine, entities, and processes. A simulation engine is a logical process responsible for synchronizing with other logical processes (using a simple window-based conservative synchronization mechanism). Entities are containers for state (such as a network switch or a compute node). The entities also contain event handlers (called services in Simian). An entity can communicate with others by scheduling services at the other entities. Processes are independent threads of execution on the entities. Simian uses lightweight threads to implement the processes—greenlets in Python and coroutines in Lua.

#### 2.1.2 Memory System

The processor memory has also gone through rapid changes in architectural design for increased capacity and performance. [DBM+11] projected that the memory capacity would reach as much as 128 peta bytes, mixing different technologies from DRAM to non-volatile memory with varying performance aspects (in terms of throughput, access latency, etc.) There exist a number of simulators in the literature for modeling the memory system.

Among the early efforts for simulation of memory system, CACTI [WJ96] is perhaps the most versatile tool with capability to model memory hierarchy at various levels: registers, buffers, caches, main memory. Another well-established memory simulator is DRAMsim [WGT+05]. It is an open-source cycle-accurate DRAM simulator, which supports various DRAM types, including SDRAM, DDR, DDR II Memory. The simulator considers various components of DRAM (e.g., DRAM memory controllers, DRAM modules for bits/data storage, and buses through which the DRAM modules communicates), and model them at great detail. It can also model the power consumption of DRAMs. DRAMsim2 [RCBJ11] is an extension of DRAMsim where it can simulate DDR II and III memory systems. It is important to note that both DRAMsim and DRAMsim2 are publicly available, and they can be incorporated with other simulators (e.g., gem5 as noted in Subsection 2.1.3) as part of a large system simulation framework.

There are also many recently-proposed memory simulators to support simulation of DRAM memory system. For example, USIMM [CBS+12] is a DRAM main memory system simulator with support for power model based on the Micron power calculator [Jan10]. The USIMM simulator is capable of working with multiple workload traces, where each trace represent a different program being executed on a dif-

ferent processor. USIMM provides interfaces to trace-based processor model. The simulator supports a number of memory scheduling algorithms proposed in the literature, including FCFS, credit-fair, power-down, close-page, first-ready-round-robin, and MLP-aware. The trace based nature of the simulator is both an advantage and disadvantage at the same time. DrSim [JYE12] is another open-source cycle-based DRAM memory system simulator. A main feature of this simulator is its focus on achieving flexibility, which makes it easy to incorporate a variety of DRAM system topologies. Ramulator [KYM15] is a recent open-source simulator for current and future DRAM systems. Ramulator aims to be fast, efficient and easily extensible. Currently, it provides cycle-accurate performance models for a variety of DRAM standards (such as DDR III/IV, LPDDR3/4, GDDR5, SALP, AL-DRAM, etc.) Ramulator's memory model has been validated against an actual implementation of DDR3 memory (with Micron's DDR3 Verilog model). Compared to the other simulators thus far, Ramulator can be shown to have achieved the best simulation performance.

### 2.1.3 Processor System

The processor architecture in HPC system has gone through perhaps the most rapid changes in recent years. Introduction of multicore and manycore architectures, support for various instruction sets, and the arrival of accelerator technologies (such as GPUs) are some examples of recent changes. Many simulators exist; a few have been proposed recently to incorporate new processor architectures with modified capabilities. They differ mostly in terms of how many instructions can be executed per second, how many cores they can support, and how accurately they can replicate the instruction execution behavior. In this subsection, we present some of the well-known processor models.

Processor simulators have gone from a single processor (core) trace-based, functional, atomic, in-order, and in-order with Cycles Per Instruction (CPI) of one, to out-of-order cycle-accurate multicore simulators. The most famous and most widely used single processor/core simulator is SimpleScalar [ALE02]. It simulated almost all of the complex interactions a "modern" superscalar processor (at the time) would have from reorder buffer, multiple issue, register renaming, complex branch prediction schemes, caches, and Simultaneous multithreading [TEL95] (SMT, now known as Hyperthreading in Intel Processors). SimpleScalar implemented Alpha and PISA Instruction Set Architectures (ISAs). After Alpha died as a commercial processor, Simplescalar suffered the stigma of an outdated ISA even though RISC ISAs were still similar to what Alpha implemented. Depending on which version and which research group used it, the simulator lacked a realistic memory system that simulated contentions on buses connecting the caches to the memory system and the contention in the DRAMs themselves and by the time that was widely available, Chip Multiprocessors (CMPs) now known as multicores had taken the processor world by storm. The advent of such complex processors pushed researchers to implement multicore simulators that spanned a wider range of capabilities. RSIM [PRA97] was the only multiprocessor simulator that was publicly available but it was not maintained and thus was outdated by the time multicores were fashionable.

Some of the most known multicore processor simulators that came out publicly were: SIMICS [MCE<sup>+</sup>02], GEMS [MSB<sup>+</sup>05], M5 [BDH<sup>+</sup>06] and lately GEMS merged with M5 generating the gem5 [BBB<sup>+</sup>11]. gem5 is a simulator that tries to simulate with varying degrees of accuracy and speed for different components of a multicore system. It has the entire spectrum from atomic cores to cycleaccurate out-of-order cores. It does have a memory subsystem including caches and coherence protocols. It also can accommodate an on-chip interconnection net-

work (i.e., Network on Chip "NoC") model/simulator (e.g., Topaz [APM+12] or Garnet [AKPJ09]) both independently implemented. One can implement his own coherence protocol and plug it in seamlessly. As we pointed out in Subsection 2.1.2, DRAMSim and DRAMSim 2.0 are two examples of how flexible gem5 is. It allows hooking up a detailed cycle-accurate memory system simulator seamlessly. GPG-PUs as accelerators that have taken their fair share of publicity also has an existence in gem5 where there is an implementation of a GPGPU integrated into gem5 (called gem5GPGPU [WSS+12]).

Another aspect of gem5 is that it can perform either in System Call Emulation (SE) mode or in Full System (FS) mode. This last point pertains to the interaction of the programs running on the processor and the operating system (OS). In system call emulation mode, the simulator fakes the existence of an OS by only implementing the minimal set of services that a program needs to run (e.g., reading and writing files). Whereas, in Full System mode, the simulator really boots up an OS (e.g., Linux or Android) and the user gets a command prompt to run his or her program(s) on the simulator. There is a trade-off between these two modes, one gives a more realistic view of the interaction in a real system where the OS interacts and influences the benchmarks/applications (e.g., database applications, OLTP, Data Mining etc.), as opposed to the other applications where such interactions are not present and only the application/benchmark performance is observed (e.g., most scientific applications). Full system mode is far slower than system emulation mode and likewise an out-of-order cycle-accurate core will be far slower than an in-order CPI of one core. At the end of the day, it is a judgment call and an experimental design parameter that has to be made consciously by the research team.

The main advantages of gem5 are the facts that it is a community research project and that it is highly extensible. It does support a variety of instruction

sets spanning commercially available CPUs such as x86 and ARM as well as famous outdated essentially extinct ISAs such as SPARC and Alpha. A new branch is implementing the RISCV [WLPA11] open-source ISA. gem5 has taken the place of Simplescalar in the processor simulation world where it is the defacto processor simulator.

There are many other recent multicore and manycore simulators. For example, McSimA+ |ALSJ13| is a lightweight, flexible, open-source simulator with detailed models for the micro-architecture of uni-core, multicore and manycore processors. The overall simulator design is divided into two parts: the (front-end) functional simulation and the (back-end) timing simulation. The functional simulation is based on Pin, a dynamic binary instrumentation tool [LCM+05] for generating the instruction stream. The timing simulation is based on an event-driven engine, responsible for calculating the correct timing for different operations (such as cache access, and packet traversal). McSimA+ supports simulation of various asymmetric core structures, hierarchical cache architectures (e.g., private, shared, and non-blocking), NoCs (e.g., buses, crossbars, ring, and 2-D mesh), memory controller, and main memory. McSimA+ has been shown to achieve good accuracy by comparing with previously published results and with real machine runs. McSimA+ has demonstrated to be able to scale to a processor with thousands of cores. Like McSimA+, ZSim [SK13] is another multicore simulator that has been shown to be lightweight, accurate, fast, and scalable. The simulator is lightweight through the use of a userlevel virtualization technique. It is accurate for its instruction-driven timing models and leveraging dynamic binary translation. The simulator is fast and scalable, and runs in parallel.

Manifold [WBB+14] is another multicore simulator. It can support full system simulation, including, for example, operating system and system binaries, and

can incorporate various models for transient and steady-state simulation of power, thermal, energy and reliability. It has an open architecture with a component-based design, so that new components can be easily incorporated through community efforts. Manifold uses QSim [KRY12], which is a multicore emulator based on dynamic binary translation. The emulator communicates with the back-end timing model for transparent parallel discrete-event simulation. Experiment has not shown, however, that Manifold can scale to larger systems with more than 64 cores. Also, its performance can only achieve a few thousand instructions per second. This probably can be attributed partially to the fact that the simulator considers full system multicore architecture simulation (including processors, cache, memory). Graphite [MKK+10] is yet another multicore processor simulator that aims to scale to thousands of cores. One of its main strengths is that it is designed to run in parallel. Other processor simulators exist such as ESESC [AR13], SimFlex [WWF+06], and MARSS [PACG11].

#### 2.1.4 HPC Applications

HPC applications exhibit distinct behaviors. An accurate model for these applications is crucial for determining the impact of technological advances in novel HPC architectures. Some of the HPC applications are data-intensive (e.g., molecular dynamics simulation and computational fluid dynamics applications). Some are communication-intensive (e.g., NERSC MIMD Lattice Computation application and NAS parallel benchmark applications). And yet others are I/O-intensive. There exist many application models and analysis tools in the literature to describe the behavior of the HPC applications with various details.

Vampir [KBD<sup>+</sup>08] is a performance analysis tool for parallel MPI/OpenMPI applications. Vampir consists of two major components: a runtime instrumentation

and measurement system and a visual analysis tool. The former supports program instrumentation in different programming languages. It also supports different types of programs: sequential programs, MPI programs, OpenMP programs, and hybrid MPI and OpenMP programs. Vampir also supports various types of instrumentation, including compiler instrumentation, library instrumentation, and manual instrumentation. It provides runtime measurement capability to capture dynamic application behaviors (such as application's memory usage, I/O performance, user-defined performance counters, etc.)

Tuning and Analysis Utilities (TAU) is a well-established, flexible, portable, robust performance instrumentation, measurement, analysis and visualization framework for HPC applications [SM06]. TAU provides flexible instrumentation capability, allowing the user to select performance instrumentation at different levels of application code. The instrumentation provides various performance information, including various system events and user-defined events, which can be later used for profiling and tracing. HPCTOOLKIT [ABF+10] is another application performance measurement, analysis, and presentation toolkit for both sequential and parallel applications. Instead of using source code instrumentation, HPCTOOLKIT works directly with application binaries. HPCTOOLKIT provides effective application analysis by providing measurement ability for a number of derived performance metrics (e.g., peak and actual performance difference rather than simple raw data such as operation counts).

The above tools can be used for measuring and displaying the runtime performance of specific applications. There also exist several analytical models to capture high-level performance. Performance and Architecture Lab Modeling Tool (Palm) is an analytical performance model for parallel applications [TH14]. Palm performs static and dynamic analysis of the source code and generates a tree-like hierarchical

data structure following some well-defined rules. Palm combines top-down semantic insight and bottom-up static and dynamic analysis capability for parallel application execution. Aspen [SV12] is a domain-specific language for analytical performance modeling to enable exploration of novel algorithms and architectures. A formal definition in Aspen includes application behavior (e.g., parameters, kernels, control flow) and the abstract machine (e.g., node, interconnect, cache, memory, core).

## 2.2 HPC Power Models

HPC systems consume a massive amount of energy to support their operation. It is well understood that effective energy-saving techniques must be considered in future HPC systems. Power and performance prediction models are essential for designing and evaluating energy-saving algorithms for these HPC systems. Many power and performance modeling techniques have been proposed in the literature.

There are a number of analytical models for power and performance prediction. [SBM09] proposed an analytical model for real-time prediction of processor and system power consumption. Performance Monitoring Counters (PMCs) are used to estimate power consumption of the processors. The proposed prediction model is based on linear regression models where the power consumption is assumed to be a piece-wise linear function. Similarly, [SBK13] proposed a unified quasi-analytical performance and power model, which combines analytical modeling and empirical analysis. The proposed method combines application analysis description with different computation and communication parameters obtained through microbenchmarking to assess the impact of different applications on the performance and energy efficiency of the target HPC system.

Next, we discuss some of the existing tools for power prediction. [HRT+12] proposed a power, area and thermal modeling framework with leakage power prediction capability for large-scale HPC simulation on SST. The framework provides power and performance prediction capability of the entire HPC system (including processor, memory and network subsystems) by incorporating different power model libraries, including McPAT [LAS+09], HotSpot, IntSim, and ORION [KLPS09], to support analysis of different system components (such as core, shared cache, memory controller and network-on-chip). Multiple Metrics Modeling Infrastructures (MuMMI) environment provides a platform to facilitate analysis, modeling and prediction of power, performance, and power-performance tradeoffs of parallel applications on multicore systems [WCM+13]. For example, [WTCM16] proposed performance and power models based on hardware performance counters with CPU frequency. They used non-negative multivariate regression analysis to build models for application execution time, system power, CPU and memory power, using a small set of major performance counters and CPU frequency.

A different line of work on energy modeling and prediction focuses on data communication in scientific applications. [DGML13] proposed a power and energy prediction method for MPI communication operations. The method takes two steps: at the calibration step, the power consumption of node and switch are measured experimentally using an external power meter, considering the underlying features of the supercomputer architecture; during the estimation step, the model estimates the energy consumption of the communication operations using data obtained from the calibration step with the user-provided program and runtime parameters (such as the number of nodes, number of cores per node, etc.) The proposed method has been validated at a large-scale HPC platform (Grid5000), and has been shown to achieve accurate energy prediction for different broadcast algorithms. [GRP+13]

also proposed an energy-performance tradeoff for large-scale complete HPC system, with particular consideration of energy consumption during communication phases. The proposed analytical model uses a compiler-based architecture-independent application analysis tool (Byfl) to identify different data-centric operations, including the number of memory accesses, and the number of operations performed by the application. The model captures energy consumption both for MPI communications and shared memory communications.

#### CHAPTER 3

### RAPID PERFORMANCE MODELING FOR HPC SYSTEMS

Interconnection network is a critical component of high-performance computing architecture and application co-design. For many scientific applications, the increasing communication complexity poses a serious concern as it may hinder the scaling properties of these applications on novel architectures. It is apparent that a scalable, efficient, and accurate interconnect model would be essential for performance evaluation studies. In this part of the dissertation, we present interconnect models for predicting the performance of large-scale applications on high-performance architectures. In particular, we present sufficiently detailed interconnect models for Cray's Gemini 3-D torus, IBM's Blue Gene/Q 5-D torus, Cray's Aries dragonfly, and Infiniband's fat-tree network.

# 3.1 Background

Recent years have witnessed dramatic changes in high-performance computing to accommodate the increasing computational demand of scientific applications. New architectural changes, including the rapid growth of multi-core and many-core systems, deeper memory hierarchies, complex interconnection fabrics that facilitate more efficient data movement for massive-scale scientific applications, have complicated the design and implementation of the HPC applications. Translating architectural advances to application performance improvement may involve delicate changes to sophisticated algorithms, to include new programming structures, different data layouts, more efficient buffer management and cache-effective methods, and alternative parallel strategies, which typically require highly skilled software architects and domain scientists.

Modeling and simulation plays a significant role, in identifying performance issues, evaluating design choices, performing parameter tuning, and answering what-if questions. It is thus not surprising that there exists today a large body of literature in HPC modeling and simulation, ranging from coarse-level models of full-scale systems, to cycle-accurate simulations of individual components (such as processors, cache, memory, networks, and I/O systems), to analytical approaches. We note, however, that none of the existing methods is capable of modeling a full-scale HPC architecture running large scientific applications in detail.

To do so would be both unrealistic and unnecessary. Today's supercomputers are rapidly approaching exascale. Modeling and simulation needs to address important questions related to the performance of parallel applications on existing and future HPC systems at similar scale. Although a cycle-accurate model may render good fidelity for a specific component of the system (such as a multi-core processor) and a specific time scale (such as within a microsecond), the model cannot be naturally extended to handle arbitrarily larger systems or longer time durations. Partially this is due to the computational complexity of the models (both spatial and temporal). More importantly, no existing models are known capable of capturing the entire system's dynamics in detail. HPC applications are written in specific programming languages; they interact with other software modules, libraries and operating systems, which in turn interact with underlying resources for processing, data access, and I/O. Any uncertainties involved with the aforementioned hardware and software components (e.g., a compiler-specific library) can introduce significant modeling errors, which may undermine the fidelity achieved by the cycle-accurate models for each specific component.

George Box, a statistician, once said: "All models are wrong but some are useful."

In order to support full-system simulation, we must raise the level of modeling

abstractions. Conceptually, we can adopt an approach, called "selective refinement codesign modeling", where we begin with both architecture and application models at coarse level, gradually refine the models with potential performance bottlenecks, and eventually stop at models sufficient to answer the specific research questions. This iterative process is based on the assumption that we can identify performance issues from the models in a timely manner. To do so, we need to develop methods that facilitate rapid and yet accurate assessment and performance prediction of large-scale scientific applications on current and future HPC architectures.

Performance prediction of large-scale parallel computers consisting thousands of node and more is a challenging task. In recent years, we have witnessed the fast growth in supercomputer design that can perform operations at scale of quadrillions of calculations per second. The tremendous rise in the computational power is in part attributed to the government agencies that have been supporting (and encouraging) the growth of large-scale supercomputing infrastructures. For example, significant investment by the U.S. Department of Energy (DOE) on building state-of-the-art supercomputers through programs (such as FastForward [VSC12], and recently FastForward 2 [Dep14]) support the fact that exascale computing will continue to receive attention in years to come. Consequently, the community faces a significant challenge for complex large-scale scientific and engineering applications to keep up and take full advantage of the fast growth of supercomputing capabilities.

We design and develop a simulator, called the *Performance Prediction Toolkit* (*PPT*). Four major aspects distinguish our effort from other existing approaches. First, our simulator needs to easily integrate large-scale applications (especially, computational physics code) with full-scale architecture models (processors, memory/cache, interconnect, and so on). Second, our simulator must be able to combine selected models of various components, potentially at different levels of modeling ab-

straction, providing a trade-off between the computational demand of the simulator and the accuracy of the models. Third, the simulator needs to adopt a minimalistic approach in order to achieve a short development cycle. It is important that new models can be easily incorporated in the simulator; the simulator needs to keep up with the fast refresh rate of HPC systems. Last, the simulator must be able to achieve scalability and high performance; it needs to be capable of handling extremely large-scale models, e.g., using advanced parallel discrete-event simulation techniques.

PPT relies on the Simian [SEL15], a parallel discrete-event simulation engine, and essentially consists of libraries of hardware models, application models, and middleware models. PPT, along with Simian, is designed to be lean, written in Python (or alternatively Lua) with minimal reliance on third-party libraries in an effort to keep the code simple, understandable, and yet offer high performance. We also present scaling runs of our interconnect model, which confirm the scalability of the underlying simulation engine.

# 3.2 Related Work

Many HPC simulators exist. Here we focus on those that provide interconnection network models. Some of these simulators aim at full-system simulation, where parallel applications are simulated to their behavior on the target architecture. BigSim [ZKK04] falls into this category. BigSim is built on Charm++ for scalable performance, which is an object-based and message-driven parallel programming system [KK93]. BigSim adopts an optimistic approach using the inherent determinacy of the target parallel applications to reduce the overhead of the optimistic scheme. Experiments show that BigSim is capable of scaling up to 64K processors.

The interconnection network model implemented in BigSim, however, is relatively simple. For example, it does not consider network congestion in detail [CGL<sup>+</sup>14]. To study the performance of large-scale MPI applications,  $\mu\pi$  is an MPI simulator based on an efficient conservatively-synchronized parallel simulator that features a process-oriented world-view [Per10]. Experiments show that the simulator is capable of simulating hundreds of millions of MPI ranks running on parallel machines. However,  $\mu\pi$  does not have any reasonably detailed interconnection network model.

The Extreme-scale Simulator (xSim) is a performance-prediction toolkit for future HPC architectures [BE11]. xSim applies parallel discrete-event simulation using lightweight threads to achieve scalability up to millions of application processes [EL10, Eng14]. xSim also incorporates different network topologies, including star, ring, tree, mesh, and torus [JE11]. However, unlike our interconnect model, network congestion is omitted in xSim to gain scalability. As such, their simulator cannot accurately model the blocking behavior of the target interconnection network which may be of importance to the architecture/application co-design.

The Structural Simulation Toolkit (SST) [RHB<sup>+</sup>11] is a comprehensive simulation framework for modeling large-scale HPC systems, including processors, memory, network, and I/O systems. It attempts to achieve scalability using a conservative parallel simulation approach. SST can model hardware components with different granularity and accuracy. SST's network model in particular contains a variety of interconnect topologies: binary tree, fat-tree, hypercube, butterfly, mesh, and so on. The interconnect model, however, does not provide the necessary details for capturing important network behaviors for performance prediction. For example, it does not support network flow control and also the links are assumed to have infinite capacity. Our interconnect model, on the contrary, provides packet-level

details that can support realistic network scenarios, such as the transient network congestion occurred during the execution of large complex applications.

The CODES simulator [CLL+11] is a comprehensive simulation platform that can model various large-scale HPC systems, including storage systems, interconnection networks, HPC and data center applications. CODES is built on ROSS, a parallel discrete-event simulation engine using reverse computation [CBP02]. CODES provides detailed models for various interconnect topologies, including torus [LCC+12], dragonfly [MCRC12], and fat-tree [LHSJ15]. CODES has shown capable of simulating large-scale interconnect configurations (with millions of nodes). A recent paper has proposed a trace-driven simulator (TraceR) to replay large execution traces to predict and understand network performance and behavior [AJB+15]. TraceR is built upon ROSS-based CODES simulator and has been shown to be able to simulate a network consisting of half million nodes using traces produced by running BigSim applications.

Although CODES is complementary to our work, there are three major differences. First, the interconnection network models in CODES are phit-level models that can capture more detailed transactions related to virtual channels than the corresponding packet-level models in PPT. While conceptually, more detailed models may render higher simulation fidelity, the computational demand would be much higher (by as much as several orders of magnitude). As such, a performance study using CODES typically would only focus on simple operations (for example, a random send/receive pattern or one collective call) and at a much smaller time scale, while using PPT we can study more complex application behaviors with greater efficiency and flexibility. In terms of accuracy, our experiments show that PPT's interconnection models can reasonably produce performance results that match from other empirical studies.