## Florida International University **FIU Digital Commons**

FIU Electronic Theses and Dissertations

University Graduate School

3-31-2017

## Customized Interfaces for Modern Storage Devices

Leonardo Marmol Florida International University, lmarm001@fiu.edu

**DOI:** 10.25148/etd.FIDC001816

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Computer Sciences Commons

#### Recommended Citation

Marmol, Leonardo, "Customized Interfaces for Modern Storage Devices" (2017). FIU Electronic Theses and Dissertations. 3165. https://digitalcommons.fiu.edu/etd/3165

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## CUSTOMIZED INTERFACES FOR MODERN STORAGE DEVICES

A dissertation submitted in partial fulfillment of the

requirements for the degree of

DOCTOR OF PHILOSOPHY

in

COMPUTER SCIENCE

by

Leonardo Mármol Amador

To: Interim Dean Ranu Jung

College of Engineering and Computing

This dissertation, written by Leonardo Mármol Amador, and entitled Customized Interfaces for Modern Storage Devices, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

|                                       | Jason Liu                                     |

|---------------------------------------|-----------------------------------------------|

|                                       | Lagranda Dahadilla                            |

|                                       | Leonardo Babadilla                            |

|                                       | Ning Xie                                      |

|                                       | Cuana Ouan                                    |

|                                       | Guang Quan                                    |

|                                       | Raju Rangaswami, Major Professor              |

| Date of Defense: March 31, 2017       |                                               |

| The dissertation of Leonardo Mármol A | mador is approved.                            |

|                                       |                                               |

|                                       | Interim Dean Ranu Jung                        |

|                                       | College of Engineering and Computing          |

|                                       | Andres G. Gil                                 |

| Vice Preside                          | ent for Research and Economic Development and |

|                                       | Dean of the University Graduate School        |

Florida International University, 2017

© Copyright 2017 by Leonardo Mármol Amador All rights reserved.

## DEDICATION

To Nikki-jo, who brings light into my days.

#### **ACKNOWLEDGMENTS**

Much needed to happen for this dissertation to be completed, and it would not have been possible without the help, collaboration, and support of many.

I want to thank my friend and life-partner Nikki-jo for all her love and care throughout these years. Without you, this journey would have been much darker and lonelier.

I want to thank my family, who never understood me but accepted me all the same. It is because of you all that I am reminded of what is truly important in life.

I want to thank my advisor and friend Dr. Raju Rangaswami for giving this opportunity, for guiding me throughout this journey, and for believing in me, even in my moments of doubt.

I want to thank my many co-authors, lab-mates, and collaborators from which I learned so much.

I want to thank my dissertation committee for all their feedback that made this work objectively better.

I want to thank all the people in the Computer Science department, in particular Olga, for helping me navigate the bureaucratic jungles of FIU.

Thank you all.

# ABSTRACT OF THE DISSERTATION CUSTOMIZED INTERFACES FOR MODERN STORAGE DEVICES

by

#### Leonardo Mármol Amador

#### Florida International University, 2017

#### Miami, Florida

#### Professor Raju Rangaswami, Major Professor

In the past decade, we have seen two major evolutions on storage technologies: flash storage and non-volatile memory. These storage technologies are both vastly different in their properties and implementations than the disk-based storage devices that current software stacks and applications have been built for and optimized over several decades. The second major trend that the industry has been witnessing is new classes of applications that are moving away from the conventional ACID (SQL) database access to storage. The resulting new class of NoSQL and in-memory storage applications consume storage using entirely new application programmer interfaces than their predecessors. The most significant outcome given these trends is that there is a great mismatch in terms of both application access interfaces and implementations of storage stacks when consuming these new technologies.

In this work, we study the unique, intrinsic properties of current and next-generation storage technologies and propose new interfaces that allow application developers to get the most out of these storage technologies without having to become storage experts themselves. We first build a new type of NoSQL key-value (KV) store that is FTL-aware rather than flash optimized. Our novel FTL cooperative design for KV store proofed to simplify development and outperformed state of the art KV stores, while reducing write amplification. Next, to address the growing relevance of byte-addressable persistent memory, we build a new type of KV store that is customized and optimized for persistent memory. The

resulting KV store illustrates how to program persistent effectively while exposing a simpler interface and performing better than more general solutions. As the final component of the thesis, we build a generic, native storage solution for byte-addressable persistent memory. This new solution provides the most generic interface to applications, allowing applications to store and manipulate arbitrarily structured data with strong durability and consistency properties. With this new solution, existing applications as well as new "green field" applications will get to experience native performance and interfaces that are customized for the next storage technology evolution.

## TABLE OF CONTENTS

| CHAPTER                                  | PAGE |

|------------------------------------------|------|

| 1. INTRODUCTION                          | . 1  |

| 2. PROBLEM STATEMENT                     | . 5  |

| 2.1 Thesis Statement                     | . 5  |

| 2.2 Thesis Contributions                 | . 5  |

| 2.3 Thesis Significance                  |      |

| 2.3.1 NVMKV                              |      |

| 2.3.2 Metradb                            |      |

| 2.3.3 LibPM                              |      |

| 3. BACKGROUND                            | . 10 |

| 3.1 NAND Based Storage Systems           |      |

| 3.2 Flash Translation Layer              |      |

| 3.3 Non-Volatile Memory                  |      |

| 3.4 NVM: Is it memory or storage?        |      |

| 4. NVMKV                                 | . 12 |

| 4.1 Introduction                         |      |

| 4.1 Introduction                         |      |

|                                          | -    |

| 4.3 Building an FTL-aware KV Store       | -    |

|                                          |      |

| rr                                       |      |

| 4.3.3 NVMKV Architecture                 |      |

| 4.3.4 NVMKV Consumer API                 |      |

| 4.4 Overview and FTL Integration         |      |

| 4.4.1 Illustrative Overview              |      |

| 4.4.2 Leveraging FTL Capabilities        |      |

| 4.5 Design Description                   |      |

| 4.5.1 Mapping Keys via Hashing           |      |

| 4.5.2 Handling Hash Collisions           |      |

| 4.5.3 Caching                            |      |

| 4.5.4 KV Pair Storage and Iteration      |      |

| 4.5.5 Optimizing KV Operations           |      |

| 4.6 Multiple KV Instances Via Pools      |      |

| 4.6.1 Need for Pools                     | . 30 |

| 4.6.2 Design Overview                    | . 31 |

| 4.6.3 Operations                         | . 31 |

| 4.7 Implementation                       | . 33 |

| 4.7.1 Extending FTL Primitives           | . 33 |

| 4.7.2 Going Beyond Traditional KV Stores | . 34 |

| 4.8   | Evaluation                           | 35 |

|-------|--------------------------------------|----|

| 4.8.1 | Workloads and Testbed                | 35 |

| 4.8.2 | Micro-Benchmarks                     | 36 |

| 4.8.3 | DRAM Trade-off and Endurance         | 38 |

| 4.8.4 | Effectiveness of the Collision Cache | 40 |

| 4.9   | Discussion and Limitations           | 41 |

| 4.10  |                                      | 42 |

| 5. M  | IETRADB                              | 43 |

| 5.1   | Introduction                         | 43 |

| 5.2   | NVM: benefits and challenges         | 44 |

| 5.3   |                                      | 46 |

| 5.4   |                                      | 46 |

| 5.5   | Case study: VSAN                     | 47 |

| 5.6   | Key-value store design for VSAN      | 48 |

| 5.6.1 |                                      | 48 |

| 5.6.2 | Application interface                | 49 |

| 5.6.3 |                                      | 49 |

| 5.6.4 | Architecture                         | 50 |

| 5.6.5 | Data structure                       | 51 |

| 5.6.6 | Transactions                         | 51 |

| 5.6.7 | Memory allocation                    | 52 |

| 5.6.8 | Data layout                          | 53 |

| 5.7   | Evaluation                           | 55 |

| 5.7.1 | Methodology                          | 55 |

| 5.7.2 | Testbed                              | 56 |

| 5.7.3 | Analysis                             | 56 |

| 5.8   | Summary                              | 58 |

| 6. L  | ibPM                                 | 59 |

|       |                                      | 59 |

|       | Architecture                         | 60 |

| 6.2.1 |                                      | 61 |

| 6.2.2 | • • •                                | 63 |

| 6.2.3 |                                      | 64 |

| 6.3   |                                      | 65 |

| 6.3.1 |                                      | 65 |

| 6.3.2 | The PM Container Abstractions        | 66 |

| 6.3.3 |                                      | 68 |

| 6.3.4 |                                      | 73 |

| 6.3.5 |                                      | 74 |

| 6.4   |                                      | 77 |

| 6.5   |                                      | 77 |

| 6.5.1 | Methodology   |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 78  |

|-------|---------------|---|---|--|--|---|---|---|---|---|---|--|--|--|---|---|---|---|---|---|--|--|---|--|---|-----|

| 6.5.2 | Correctness . |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 78  |

| 6.5.3 | Ease of use . |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 79  |

| 6.5.4 | Performance   |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 83  |

| 6.6   | Summary       | • |   |  |  |   |   | • | • | • |   |  |  |  |   |   | • |   |   |   |  |  | • |  |   | 90  |

| 7. R  | ELATED WOR    | K |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 92  |

| 7.1   | NVMKVS        |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 92  |

| 7.2   | METRADB       |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 94  |

| 7.3   | LIBPM         | • |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   | • | • | • |  |  |   |  | • | 94  |

| 8. C  | Conclusions   |   | • |  |  | • | • |   |   |   | • |  |  |  | • | • |   | • | • | • |  |  |   |  |   | 96  |

| BIBL  | LIOGRAPHY .   |   |   |  |  |   |   |   |   | • |   |  |  |  |   |   |   |   |   |   |  |  |   |  | • | 98  |

| VITA  |               |   |   |  |  |   |   |   |   |   |   |  |  |  |   |   |   |   |   |   |  |  |   |  |   | 106 |

## LIST OF FIGURES

| FIGU | JRE P.                                                                                                                                                                                             | AGE |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

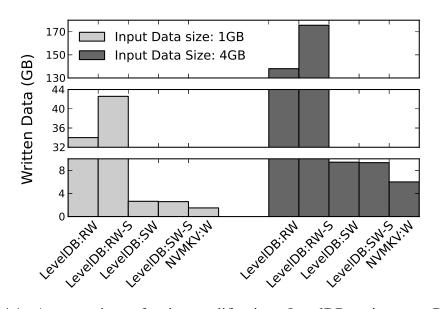

| 4.1  | A comparison of write amplification. LevelDB variants are RW: Random asynchronous writes, RW-S: random synchronous writes, SW: sequential asynchronous writes, SW-S: sequential synchronous writes | 13  |

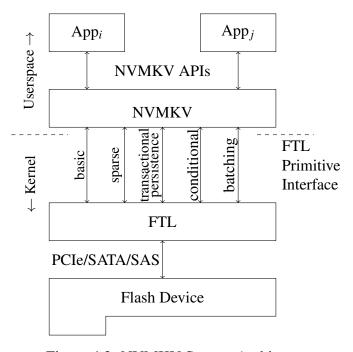

| 4.2  | NVMKV System Architecture                                                                                                                                                                          | 18  |

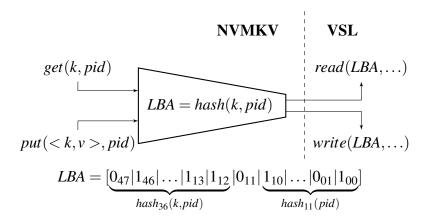

| 4.3  | Hash model used in NVMKV. The arguments to the functions represent k:key, v:value, and pid:pool_id                                                                                                 | 25  |

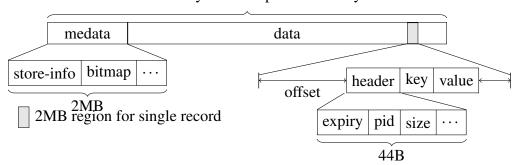

| 4.4  | NVMKV layout                                                                                                                                                                                       | 28  |

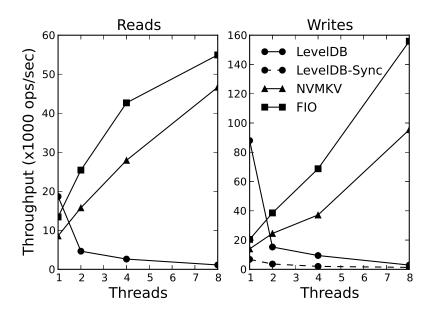

| 4.5  | Microbenchmark comparing the throughput of LevelDB, NMVKV and Raw Block Device (FIO) for small (1KB) IO operations                                                                                 | 36  |

| 4.6  | Comparing multiple identical instances of LevelDB with a single instance of NVMKV with equal number of pools                                                                                       | 37  |

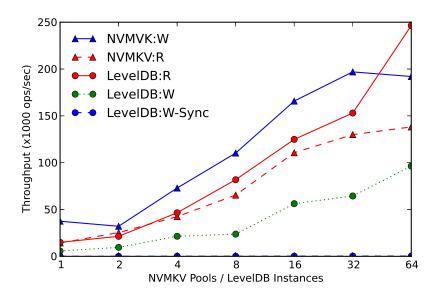

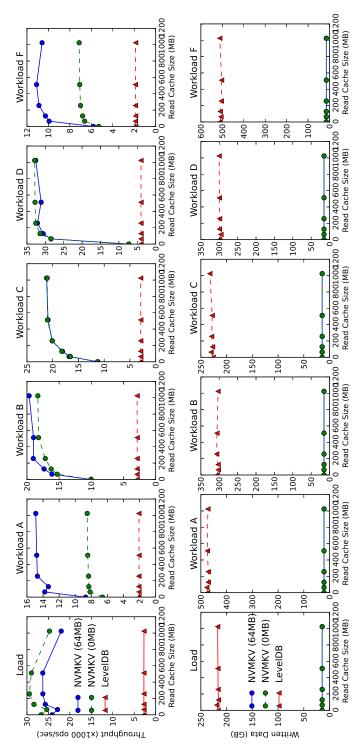

| 4.7  | Throughput comparison between NVMKV and LevelDB using YCSB workloads (above). Write Amplification Comparison between NVMKV and LevelDB using YCSB workloads (below)                                | 39  |

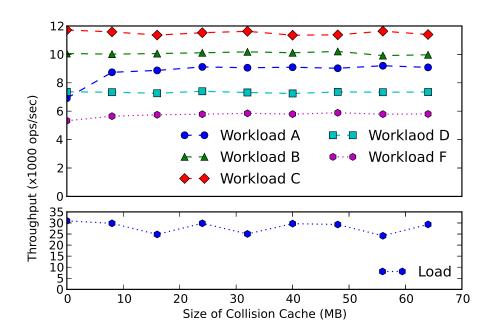

| 4.8  | Collision cache impact on YCSB workloads                                                                                                                                                           | 41  |

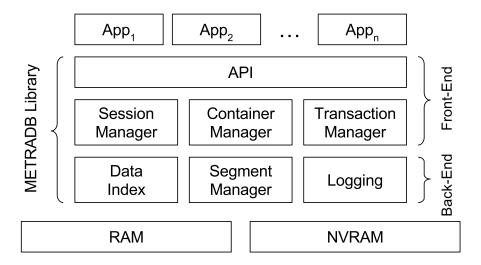

| 5.1  | METRADB architecture                                                                                                                                                                               | 50  |

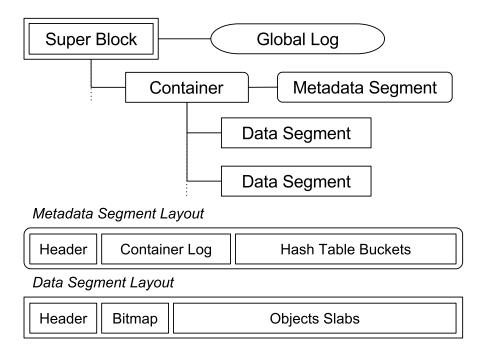

| 5.2  | Data layout in METRADB                                                                                                                                                                             | 53  |

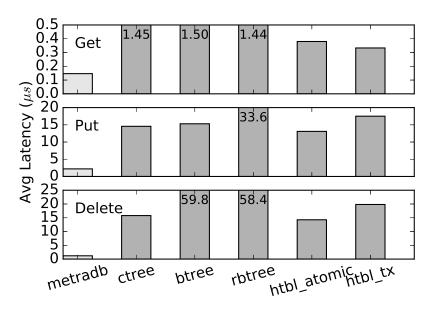

| 5.3  | Latency of each operation in each system                                                                                                                                                           | 54  |

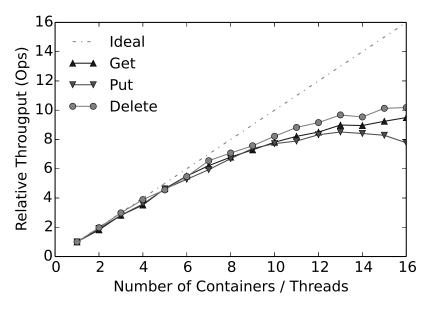

| 5.4  | Throughput scalability of METRADB                                                                                                                                                                  | 54  |

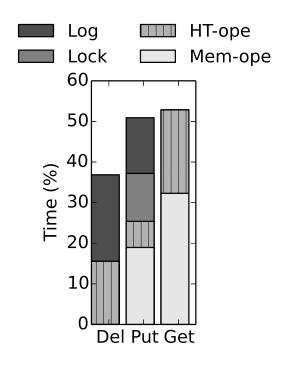

| 5.5  | METRADB execution breakdown                                                                                                                                                                        | 55  |

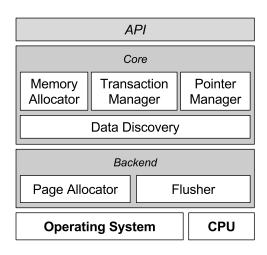

| 6.1  | LIBPM Architecture                                                                                                                                                                                 | 61  |

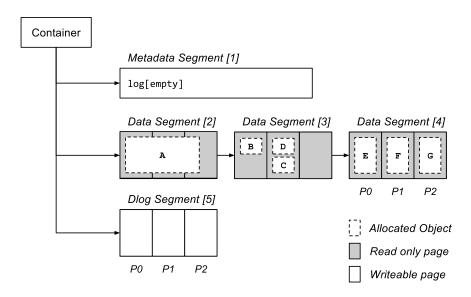

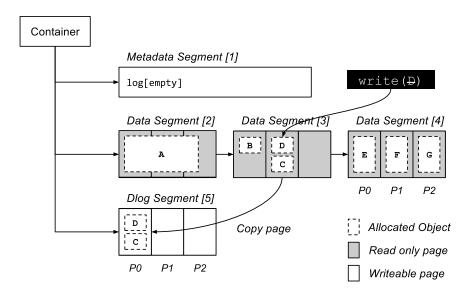

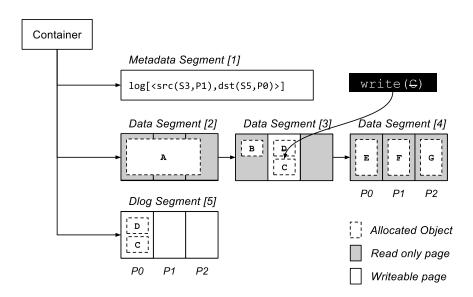

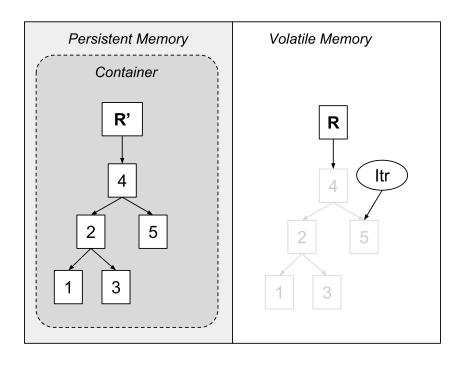

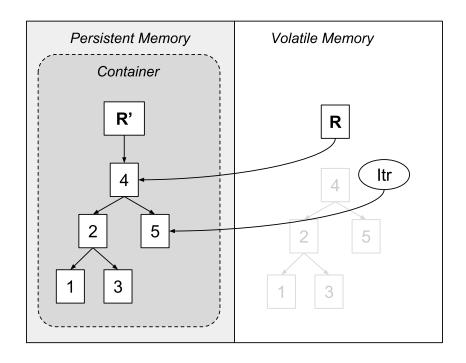

| 6.2  | LIBPM page logging. State of a container after a successful open                                                                                                                                   | 69  |

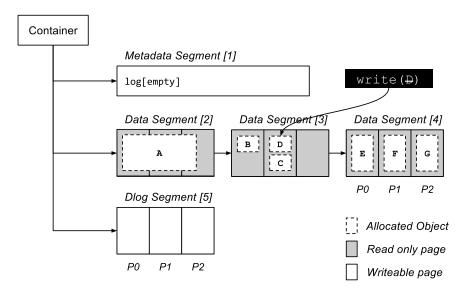

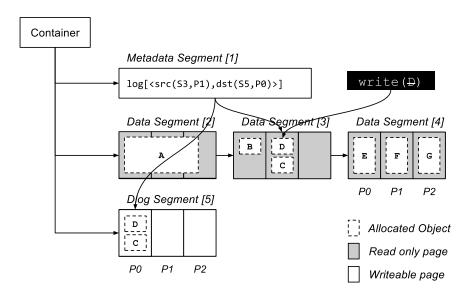

| 6.3  | LIBPM page logging. The application tries to update object $D$ which is mapped read-only                                                                                                           | 69  |

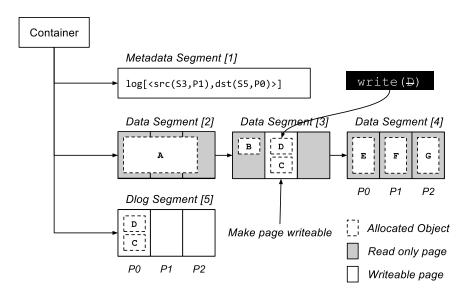

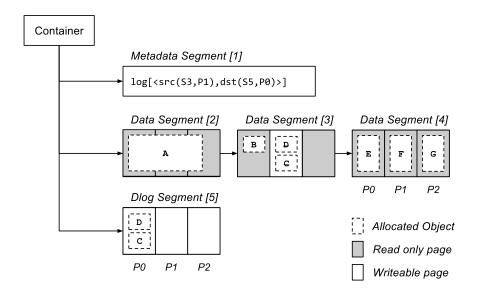

| 6.4  | LIBPM page logging. The update triggers the fault handler, which initiates the logging mechanism by making a copy of the page containing the faulting address                                      | 70  |

| 6.5  | LIBPM page logging. Next the update is logged                                                                                                                                                      | 70  |

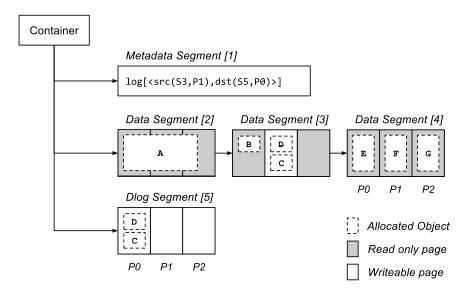

| 6.6  | LIBPM page logging. Then the page is made writable                                                                                                                                                 | 71  |

| 6.7  | intended, all without user intervention                                             | 71 |

|------|-------------------------------------------------------------------------------------|----|

| 6.8  | LIBPM page logging. Subsequent update to the same page proceed without any overhead | 72 |

| 6.9  | LIBPM page logging. State of the container after two updates                        | 72 |

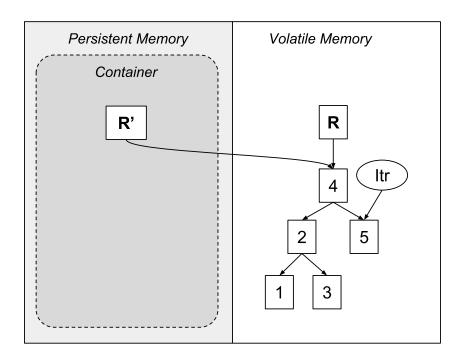

| 6.10 | Container Closure: Initial state                                                    | 75 |

| 6.11 | Container Closure: Moving all reachable nodes to the Container                      | 75 |

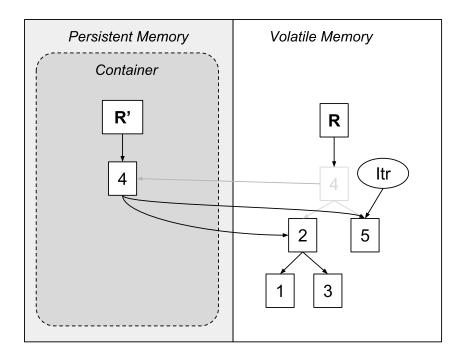

| 6.12 | Container Closure: All nodes moved                                                  | 76 |

| 6.13 | Container Closure: Fixing back references                                           | 76 |

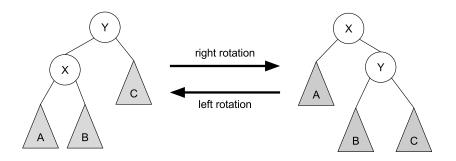

| 6.14 | Tree rotation                                                                       | 81 |

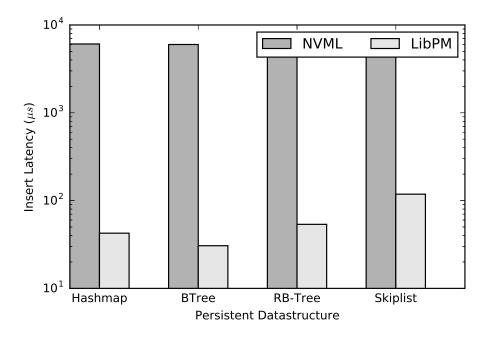

| 6.15 | NVML vs LIBPM (Inserts)                                                             | 84 |

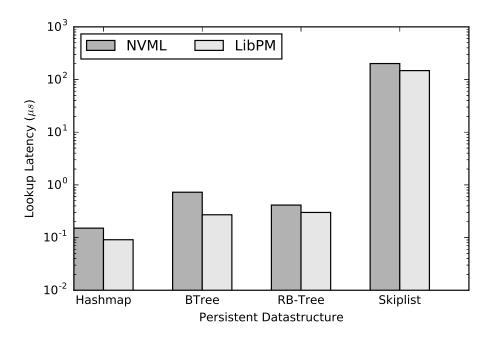

| 6.16 | NVML vs LibPM (Lookups)                                                             | 85 |

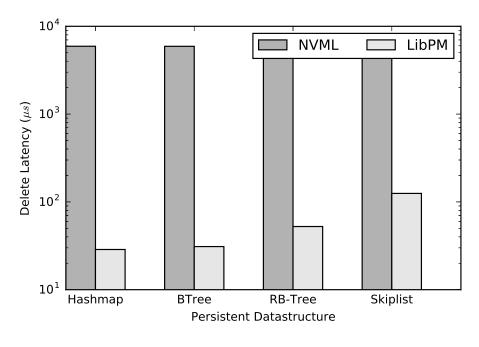

| 6.17 | NVML vs LIBPM (Deletes)                                                             | 85 |

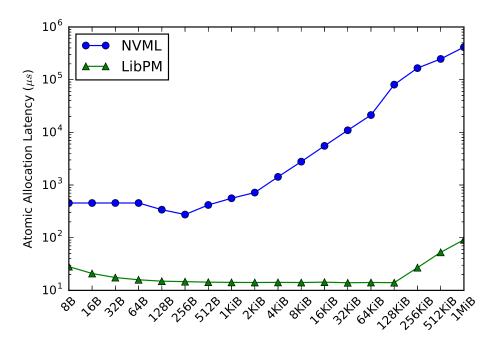

| 6.18 | Allocation Latency                                                                  | 87 |

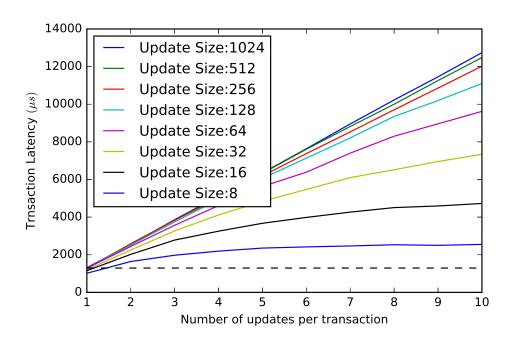

| 6.19 | Atomic update latency                                                               | 89 |

#### CHAPTER 1

#### INTRODUCTION

Storage systems are becoming increasingly important in private, public, and hybrid cloud data centers. Over time, interfaces to storage have evolved from being file oriented, to block oriented, to key-value oriented, and now memory oriented. The block interface established by early disk drives have sustained and dominated storage access for enterprise storage arrays including disk-only, hybrid, and flash-only implementations. Classic storage consuming applications such as SQL database have been increasingly optimized for the block interface over the years even as the underlying implementations have changed. A parallel evolution in the storage stack is that the underlying device technology has changed significantly as well. The industry has almost completely moved from disk to flash-based storage for primary storage in the enterprise.

A recent evolution of the application interface to storage is the key-value interface [mema, Mon14, Roc14, DSL11, MST<sup>+</sup>14] and a recent evolution in device technology is high-performance flash devices. Key-value stores have become a very popular storage solution for web services, NoSQL applications and distributed environments. The appeal of the interface is the ease of storing and accessing data when associating a minimum amount of semantic information with the data itself. One of the main reasons for the success of key-value stores is their higher performance [BPPP09, DSL10] and scalability [DHJ<sup>+</sup>07], when compared to traditional storage solutions like relational databases.

It is thus no surprise that modern key-value stores were particularly design for flash storage as a way to provide an even higher performing storage solutions. In doing so, developers often need to make assumptions about the internals of flash storage devices. But these details are often not made available to the public, and optimizations that work well for one vendor do not for others [YPG<sup>+</sup>14] To improve the situation, we propose

that FTL-aware designs, that expose to the applications some of the internal mechanisms of the flash storage, are necessary.

In this thesis, we explore the design of key-value store like solutions for a completely different storage technology, non-volatile memory (NVM). NVM technologies offer a unique duality that combines the byte-addressability and low latency of DRAM with the durability of traditional storage. This eliminates the need to come up clever ways of moving data back and forth between slow persistent storage and fast volatile memory. However, programming directly onto NVM is non trivial, and recycling existing solutions for managing memory or storage are not applicable to NVM. To bridge this gap, we propose and build on top of a new, extended device interface to flash storage that allows a custom library implementation to extract significantly higher performance from the storage device. We empirically demonstrate that the use of this extended interface, that is aware of the underlying flash management mechanisms not only simplify the design and implementation of key-value stores but also significantly improve their performance.

While flash based storage technology has a stronghold on primary storage products for primary data storage, we are currently at the beginning of the next evolution of storage — from flash-based block storage to byte-addressable persistent memory. The next generation of persistent storage devices are going to be memory oriented [Int15a]. The emergence of byte-addressable persistent memory (PM) hardware, such as ReRAM, STT-MRAM, PCM, and 3D-XPoint present a combination of properties of both memory and storage. 3D-XPoint persistent memory from Intel is currently the most promising and it is expected to provide storage access latencies in the order of tens of nanoseconds for 512-byte accesses. This is three orders of magnitude faster than state-of-the-art flash and immediately brings into focus the overheads contained in the storage stack.

Just as the onset of disk-based storage provided the impetus for seek-optimizing workload shaping and flash-based storage have addressed capacity constraints and flash lifetime management, this next evolution of storage technology will usher in entirely new class of applications and new mechanisms for application access to storage. Conventional block I/O processing in the OS has shown to add as much as 300  $\mu$ s of overhead to each operation and even highly optimized software stacks that bypass the OS for device access add as much as 20  $\mu$ s of overhead [CME<sup>+</sup>12, CS13]. The memory-like properties of this new class of persistent memory storage open up the possible of using lowlatency load/store access. However, store interfaces were design with a much slower medium in mind that operate a much coarse granularity [CLU+15, CME+12, VTS11b, CCA<sup>+</sup>11b]. Moreover, memory interfaces to storage do not automatically provide the consistency and durability properties that applications expect from traditional storage, and the other hand, When an application consuming storage through a KV interface chooses to utilize a persistent memory device, the existing solutions suffer an impedance mismatch whereby they map the KV implementation to a memory oriented block device (e.g., a RAMDISK) [CLU<sup>+</sup>15, CNF<sup>+</sup>09, DKK<sup>+</sup>14]. Alternatively, custom-built KV stores for memory lose generality. In this thesis, we propose to consume NVM through a native key-value interface with transactions support for updates. With our proposed solution, applications consume NVM without having to understand the details of NVM, and thereby trading high performance for generality.

In the last part of this thesis we focus on a more general approach to NVM in order to enable NVM for all types of applications. While key-value stores are very popular alternative for data storage solutions, many application have requirements that are not satisfy by the simple data model of key vale stores. In particular, having to access all data through a key value interface may impose too much impedance mismatch, and for some applications too much overhead. Additionally, hand-crafting point solutions for storing data within persistent memory could quickly become too costly and time consuming. Then is becomes necessary to have a more generic abstraction that exposes the

What is necessary is a generic abstraction that will expose the richness and performance of the memory interface to the applications and support seamless persistence. To this end, we propose LIBPM: a persistent memory library that implements the *containers* abstraction. The proposed persistent containers are self-contained data hosting units that allow applications to directly store, fetch, and update arbitrarily complex data structures at memory speeds. They provide a simple and light-weight transactional update capabilities that simplify applications development. Additionally, LIBPM simplifies the porting of legacy applications to NVM technologies by automatically discovering and persistent applications' in-memory data based on simple hints.

The next chapter outlines the main claims of this dissertation. It starts by listing the proposed problems to study, followed by descriptions of our proposed solutions and their significance. Each chapter of this dissertation is written to be as self contained as possible. However, in order to better understand the material here presented, readers are encouraged to get familiar with the terms and concepts described in the background chapter 3. The rest of this document dedicates a chapter to each of the systems we have built to address the proposed problems. We conclude the dissertation with a survey of related literature and a detailed description on how our solutions differs from previous ones, concluding statements, and directions for future work.

#### CHAPTER 2

#### PROBLEM STATEMENT

This chapter introduces the proposed research problems and their significance. In addition, this chapter also identifies the major challenges associated to the problems in question and outline our unique contributions.

#### 2.1 Thesis Statement

We propose building native storage solutions to applications that are tailor-made for the underlying storage device technology by:

- providing native integration between key-value stores and modern flash storage devices,

- 2. building a key-value store with native, transactional update capabilities when using *non-volatile memory* (NVM) devices, and

- 3. providing a new, generic application interfaces to NVM devices suitable for both supporting new applications and for porting of legacy applications to NVM.

#### 2.2 Thesis Contributions

This thesis addresses the challenges of building native storage support for applications and makes three distinct contributions.

First, we build native support for accessing today's advanced flash devices via a simple and commonly-used key-value interface. Existing key-value stores use flash storage like any other block device. This approach is convenient because it requires no application modifications, but it does not use the full potential of modern flash storage. Modern Flash Translation Layers (FTL) implement many advanced capabilities that, if exposed to

the application layer, could significantly simplify application design and improve performance. Because these interfaces are not exposed to the applications layer, key value stores end up re-implementing some of these capabilities, incurring in additional resources consumption, higher overhead and poorer performance. Examples of these capabilities include mapping from logical to physical addresses, logging, and atomic updates. In this thesis, we propose extending traditional block device interfaces for flash storage, so that these advanced capabilities are made available to the application layer.

Second, we build native support for using next generation *non-volatile memory* (NVM) devices via a key-value interface. With the arrival of NVM device technologies new opportunities for improving the performance of applications become available. Of these options, programming NVM directly is the most effective, yet also the most difficult and error prone. To correctly program NVM, developers would have to become familiar with the many subtleties of NVM that could only be expected from an expert in the subject. For example, even though NVM is persistent, CPU caches are not. So in order to make memory update persistent, CPU caches need to be carefully flushed to guarantee data durability without impacting performance. And depending on the NVM technology and the system architecture, additional instructions may be needed to avoid buffering on the memory controllers. In addition, CPU caches perform out-of-order evictions at any time, making the use memory fences a requirement to preserve applications data consistency. Finally, physical characteristics of competing technologies are often not available to the user, and optimizations for one type of NVM do not apply to others. For these reasons, we propose applications to consume NVM through an indirection layer that hide all the complexities of NVM. To this end, we build a key-value store with support for transactional updates as a viable interface for this indirection layer.

Finally, we go beyond the key-value interface to build native support for accessing NVM similar to how volatile memory is consumed today for increased generality and us-

age. Using a key-value store to consume NVM trades generality for simplicity and high performance. While the key-value interface is adequate for many applications, it is not good enough for others applications with more complex data requirements. In addition, the key-value store favors the development of new applications without providing a pathway for legacy applications to consume NVM without a significant rewrite of their core logic. To overcome these limitations, we propose LIBPM: a Persistent Memory Library that implements Container as the main abstraction for consuming NVM. Containers are a data hosting unit that can store arbitrarily complex data types while preserving their integrity and consistency. This abstraction facilities the use of NVM without having to navigate all the pitfalls of programming NVM directly. LIBPM provides a simple and high performing transactional update semantics which allows applications to manipulate persistent data at the speed of memory. In addition, LIBPM provides a mechanism to port legacy applications to NVM with automatic data discovery.

## 2.3 Thesis Significance

This thesis addresses current problems related to developing and deploying applications that consume storage with high-performance and correctness. The solutions discussed in this thesis allow applications to consume storage using high-level API without being concerned about the internals of the underlying storage device and storage software stack implementations. These solutions, in effect, create a sophisticated layer of indirection with native mechanisms for consuming the underlying storage device and exposing simple abstractions to the application developer.

#### 2.3.1 **NVMKV**

Designing a key-value store that uses the capabilities of moderns FTL layers has multiple benefits. Firstly, it significantly simplifies the design and implementation of the key-value store because many of the internal mechanism needed by the key-value store are already implemented by the FTL layer. Some of these mechanisms include data mapping, compaction/garbage collection, and sparse addressing. Secondly, it improves the performance of the key-value stores by minimizing applications-level write amplifications and reducing the number of IOs per operations. Thirdly, it reduces the resource utilization by the key-value layer because many of the internal in-memory mappings are maintained by the FTL-layer and replaced by simple hashing schemes. Finally, it improves the life time of the device as an consequence of the reduced write amplification and on average one IO per operation.

#### **2.3.2** METRADB

Piggy backing on the popularity of key-value stores, we propose the consumption of NVM through key-value store interfaces with support for transactional updates. This approach makes it easy for modern applications to use NVM without having to worry about the internals of NVM or maintaining application's data in a consistent state. The simplicity of key-value stores interfaces eases the design and implementation of high performing transactional semantics. Additionally, it eliminates many challenges related to using NVM directly such as managing persistent data structure integrity and data sharing. Finally, consuming NVM through an indirection layer facilitates the adoption of future NVM technologies at low development cost because the core application logic remains untouched.

#### **2.3.3** LIBPM

To address the limitations of the key-value store interface at address the needs of a lager number of application, LIBPM exposes a familiar memory-like interface that operate on Containers. At a high level, Container host persistent data and guarantee the durability and consistent of the data it hosts. Unlike key-value stores, LIBPM allows unsupervised access to the data it manages by memory mapping Container directly into the application's address space. This eliminates the impedance of having to access data in persistent memory through a key value stores APIs. Another advantage of LIBPM over key value stores is that LIBPM can manage arbitrarily complex data types and it's aware of object relations (pointers) which is typically not supported on key value stores. Once a LIBPM Container is open, all of is data is readily available for the applications without having to deal with any pointer swizzling. LIBPM also provide a simple transactional model that allows developers to make in-memory updates durable with a single atomic API call at the Container granularity. This atomic operations effectively mutates the state of the Container from one consistent point in time to the next. Additionally, LIBPM implements an automatic data discovery mechanism based on applications hints that facilitates porting legacy applications to NVM technologies in an incremental fashion and without any changes to their core logic. With LIBPM, applications effectively get to consume persistent memory as if it were volatile memory, enabling developers to write applications tailor-made for persistent memory with relative ease.

#### **CHAPTER 3**

#### **BACKGROUND**

In this chapter we define concepts that are prerequisite for understating the problem described in this thesis as well as the proposed solutions.

## 3.1 NAND Based Storage Systems

NAND flash memory is a type of non-volatile storage technology that does not require power to retain data. There three types of operations that can be performed on NAND flash: read, write and erase. Reads are typically faster than writes, and writes are faster than erase by about an order of magnitude. Due to the physical characteristics of NAND, data can not be overwritten without first erasing it. This unique characteristic of flash storage has a major impact on how applications use flash storage.

## 3.2 Flash Translation Layer

NAND Flash storage devices have a software component known as the flash translation layer. This software layer is in charge of presenting the flash storage device to the OS as a regular block device. Additionally, the FTL is in charge or maintaining the mapping between logical to physical addresses, reclaiming unused space in the device (this process is also known as garbage collection), and placing data across the device in a way that avoids uneven wear leveling.

## 3.3 Non-Volatile Memory

Non-volatile memory (NVM) or persistent memory is a type of memory that like NAND flash does not required power to retain data, but unlike flash it allows data accesses at a

byte (8 bits) granularity. NVM is also a random-access memory with latencies for reads and write operations that are comparable to those of DRAM. In this document we will use the terms non-volatile memory and persistent memory interchangeably.

## 3.4 NVM: Is it memory or storage?

Conventionally, applications have consumed memory and storage through different interfaces. Memory is typically managed by an external library (e.g. libc) which adds new mappings to an application's address space, allowing direct access to data. Storage, on the other hand, is traditionally managed by an external entity like a file system or a database, which provides supervised access to data and guarantees data consistency. Since the existing memory interface guarantees no data durability, it cannot be used *as-is* for NVM. The well-established file interface can also fall significantly short in utilizing the potential of NVM. The large granularity of block-oriented file system induces high software and data transfer overheads making small reads and updates expensive [DKK+14, CME+12, CLU+15]. For these reasons, we believe that in order to fully exploit the potential of NVM a software stack and developer interfaces will need to be created.

#### **CHAPTER 4**

#### **NVMKV**

In this chapter we examine flash storage devices and how to write applications for this new type of media in a way to utilizes flash full potential. In order to do so, we take a closer looks at the software component of flash storage, the Flash Translation Layer (FTL), and illustrate how exposing some of the FTL internals to user space applications could simplify applications design and improve applications performance. We demonstrate this approach by implementing a high-performance Key-Value Store with transactional update optimized for modern flash storage devices.

#### 4.1 Introduction

Flash-based key-value (KV) stores are becoming mainstream, with the importance of the KV interface to storage and flash technology have been well established through a gamut of implementations [AFK<sup>+</sup>09, BPPP09, DSL10, DSL11, LFAK11]. However, best utilizing the high-performance flash-based storage to drive the new generation of key-value stores continues to remain a challenge. The majority of the existing KV stores use a logging-based approach which induces significant additional *write amplification* (WA) at the KV software layer in addition to the internal WA caused by the FTL while managing physical flash. The recent LevelDB KV store from Google [GD11] also exhibits rather dramatic auxiliary write amplification. Figure 4.1 reveals a minimum of 2.5*x* auxiliary write amplification for sequential asynchronous writes and a maximum of 43*x* for random synchronous writes.

Modern FTLs offer new capabilities that enable compelling, new design points for KV stores [T1013, Ope14]. Integration with these advanced capabilities results in an optimized *FTL-aware* KV store [MST<sup>+</sup>14]. First, writing to the flash can be optimized to significantly improve both device lifetime and workload I/O performance. Second, mod-

Figure 4.1: A comparison of write amplification. LevelDB variants are RW: Random asynchronous writes, RW-S: random synchronous writes, SW: sequential asynchronous writes, SW-S: sequential synchronous writes.

ern FTLs already perform many functions that are similar to the functionality built into many KV stores such as log-structuring, dynamic data remapping, indexing, transactional updates, and thin provisioning [JBLF12, ONW<sup>+</sup>11, SSZ12]. Avoiding such replication of functionality can offer significant resource and performance benefits.

Next we present the design, implementation, and evaluation of NVMKV, an FTL-aware KV store. NVMKV has been designed from the ground up to utilize the advanced capabilities found in modern FTLs. It implements a hashing-based design that uses the FTLs sparse address-space support to eliminate all write amplification at the KV layer, improving flash device endurance significantly relative to current KV stores. It is able to achieve single I/O get/put operations with performance close to that of the raw device, representing a significant improvement over current KV stores. NVMKV uses the advanced FTL capabilities of *atomic multi-block write*, *atomic multi-block persistent trim*, *exists*, and *iterate* to provide strictly atomic and synchronous durability guarantees for

#### KV operations.

Two complementary factors contribute to increased collocation requirements for KV stores running on a single flash device. First, given the increasing flash densities, the performance points of flash devices are now based on capacity with larger devices being more cost-effective [YPG+14]. Second, virtualization supports increases in collocation requirements for workloads. A recent study has shown that multiple independent instances of such applications can have a counterproductive effect on the underlying FTL, resulting in increased WA [YPG+14]. NVMKV overcomes this issue by offering a new *pools* abstraction that allows transparently running multiple KV stores within the same FTL. While similar features exist in other KV stores, the FTL-aware design and implementation within NVMKV enables both efficient FTL coupling and KV store virtualization. NVMKV's design also allows for optimized flash writing across multiple KV instances and as a result lowers the WA.

In the quest for performance, KV stores and other applications are trending towards an in-memory architecture. However, since flash is still substantially cheaper than DRAM, any ability to offset DRAM for flash has the potential to reduce Total Cost of Ownership (TCO). We demonstrate how accelerating KV store access to flash can in turn result in similar or increased performance with much less DRAM.

We evaluated NVMKV and compared its performance to LevelDB. We evaluated the scalability of pools, compared it to multiple instances of LevelDB, and also found that NVMKV's atomic writes outperform both async and sync variants of LevelDB writes by up to 6.5x and 1030x respectively. NVMKV reads are comparable to that of LevelDB even when the workloads fit entirely in the filesystem cache, a condition that benefits LevelDB exclusively. When varying the available cache space, NVMKV outperforms LevelDB and more importantly introduces a write amplification of 2x in the worst case, which is small compared to the 70x for LevelDB. Finally, NVMKV improves YCSB

benchmark throughput by up to 25% in in comparison to LevelDB.

#### 4.2 Motivation

In this section, we discuss the benefits of better integration of KV stores with the FTL's capabilities. We also motivate other key tenets of our architecture, in particular the support of multiple KV stores on the same flash device and the need to increase performance with smaller quantities of DRAM.

An FTL-aware KV store: A common technique for performance improvement in flash optimized KV stores is some form of log structured writing. New data is appended to an immutable store and reorganized over time to reclaim space [Aer, Roc14, GD11, LFAK11]. The reclamation process, also called garbage collection or compaction, generates *Auxiliary Write Amplification (AWA)* which is the application level WA above that which is generated by the FTL. Unfortunately, AWA and the FTL induced WA have a multiplicative effect on write traffic to flash [YPG+13]. Previous work highlighted an example of this phenomenon with LevelDB, where a small amount of user writes can be amplified into as much as 40X more writes to the flash device [MST+14]. As another example, the SILT work describes an AWA of over 5x [LFAK11]. NVMKV entirely avoids AWA by leveraging native addressing mechanisms and optimized writing implemented within modern FTLs.

Multiple KV stores in the device: The most recent PCIe and SAS flash devices can provide as much as 4-6TB of capacity per device. As density per die increases with every generation of flash driven by the consumer market, the multiple NAND dies required to generate a certain number of IOPs will come with ever increasing capacities as well as reduced endurance [GDS12]. Multiple KV stores on a single flash device become cost effective but additional complexities arise. For instance, recent work shows how

applications that are log structured to be flash optimal can still operate in suboptimal ways when either placed above a file system or run as multiple independent instances over a shared FTL [YPG<sup>+</sup>14]. NVMKV provides the ability to have multiple independent KV workloads share a device with minimal AWA.

Frugal DRAM usage: The ever increasing need for performance is driving the inmemory computing trend [Mem14, SAP14, DFI<sup>+</sup>13]. However, DRAM cost does not scale linearly with capacity since high capacity DRAM and the servers that support it are more expensive per unit of DRAM (in GB) than the mid-range DRAM and servers. The efficacy of using flash to offset DRAM has also been established in the literature [BP11]. In the KV store context, similar arguments have been made showing the server consolidation benefits of trading DRAM for flash [Aer]. A KV store's ability to leverage flash performance contributes directly to its ability to trade off DRAM for flash. NVMKV operates with high performance and low WA in both single and multiple instance KV deployments.

## 4.3 Building an FTL-aware KV Store

NVMKV is built using the advanced capabilities of modern FTLs. In this section, we discuss its goals, provide an overview of the approach, and describe its API.

#### **4.3.1** Goals

NVMKV is intended for use within single node deployments by directly integrating it into applications. While it is not intended to replace the scale out key-value functionality provided by software such as Dynamo and Voldemort [DHJ<sup>+</sup>07, SKG<sup>+</sup>12], it can be used for single node KV storage within such scale out KV stores. From this point onward, we

refer to such single node KV stores simply as KV stores. We had the following goals in mind when designing NVMKV:

**Deliver Raw Flash Performance:** Convert the most common KV store operations, GET and PUT into a single I/O per operation at the flash device to deliver close to raw flash device performance. As flash devices support high levels of parallelism, the KV store should also scale with parallel requests to utilize the performance scaling capacity of the device. Finally, when multiple, independent KV instances are consolidated on a single flash device, the KV store should deliver raw flash performance to each instance.

Minimize Auxiliary Write Amplification: Given the multiplicative effect on I/O volume due to WA, it is important to minimize additional KV store writes, which in turn reduces the write load at the FTL and the flash device. Reducing AWA improves KV operation latency by minimizing the number of I/O operations per KV operation as well as improvement of flash device lifetime.

**Minimize DRAM Consumption:** Minimize DRAM consumption by (*i*) minimizing the amount of internal metadata, and (*ii*) by leveraging flash performance to offset the amount of DRAM used for caching.

**Simplicity:** Leverage FTL capabilities to reduce code complexity and development time for the KV store.

## 4.3.2 Approach

Our intent with NVMKV is to provide the rich KV interface while retaining the performance of a much simpler block based flash device. NVMKV meets its goals by leveraging the internal capabilities of the FTL where possible and complementing these with streamlined additional functionality at the KV store level. The high level capabilities that we leverage from the FTL include:

| Category   | API             | Description                                                 |

|------------|-----------------|-------------------------------------------------------------|

|            | get()           | Retrieves the value associated with a given key.            |

| Basic      | put()           | Inserts a KV pair into the KV store.                        |

|            | delete()        | Deletes a KV pair from the KV store.                        |

| Iterate    | begin()         | Sets the iterator to the beginning of a given pool.         |

| Herate     | next()          | Sets the iterator to the next key location in a given pool. |

|            | get_current()   | Retrieves the KV pair at the current iterator location in a |

|            |                 | pool.                                                       |

|            | pool_exist()    | Determines whether a key exists in a given pool.            |

| Pools      | pool_create()   | Creates a pool in a given NVMKV store.                      |

| Pools      | pool_delete()   | Deletes all KV pairs from a pool and deletes the pool from  |

|            |                 | NVMKV store.                                                |

|            | get_pool_info() | Returns metadata information about a given pool in a KV     |

|            |                 | store.                                                      |

|            | batch_get()     | Retrieves values for a batch of specified keys.             |

| Datahina   | batch_put()     | Sets the values for a batch of specified keys.              |

| Batching   | batch_delete()  | Deletes the KV pairs associated with a batch of specified   |

|            |                 | keys.                                                       |

|            | delete_all()    | Deletes all KV pairs from a NVMKV store in all pools.       |

|            | open()          | Opens a given NVMKV store for supported operations.         |

| Monogomont | close()         | Closes a NVMKV store.                                       |

| Management | create()        | Creates a NVMKV store                                       |

|            | destroy()       | Destroys a NVMKV store.                                     |

Table 4.1: **NVMKV API** The table provides brief descriptions for the NVMKV API calls.

Figure 4.2: NVMKV System Architecture

**Dynamic mapping:** FTLs maintain an indirection map to translate logical addresses into physical data locations. NVMKV leverages the existing FTL indirection map to the fullest extent to avoid maintaining any additional location metadata. Every read and write operation simply uses the FTL indirection map and thereby operates at raw flash device performance by definition. This approach also reduces the additional DRAM overhead of NVMKV.

**Persistence and transactional support:** FTLs access data and metadata, and in particular maintain the persistence of indirection maps, at the speed of raw flash. NVMKV leverages this highly tuned capability to reduce the overhead for metadata persistence, logging, and checkpointing operations. Further, as FTLs operate as non-overwriting redirect-on-write stores, they can easily provide high performance transactional write semantics [ONW<sup>+</sup>11]. NVMKV leverages these capabilities to limit locking and journaling overheads.

**Parallel operations:** FTLs already implement highly parallel read/write operations while coordinating metadata access and updates. NVMKV leverages this FTL feature to minimize locking, thus improving scalability. We also define batch operations that are directly executed by the FTL to enable parallel KV store requests to be issued with lower I/O stack overhead [VKA12a].

#### 4.3.3 NVMKV Architecture

NVMKV is a lightweight library in user space which interacts with the FTL through a *primitives interface* implemented as IOCTLs to the device driver that manages the flash device. Figure 4.2 shows the architecture of a system with NVMKV. Consumer applications, such as scale out KV stores, communicate with the NVMKV library using the

NVMKV API. The NVMKV API calls are translated to underlying FTL primitives interface calls to be executed by the FTL.

| Category      | API                 | Description                                            |

|---------------|---------------------|--------------------------------------------------------|

|               | read()              | Reads the data stored in the Logical Block Address     |

| Basic         |                     | (LBA).                                                 |

|               | write()             | Writes the data stored in buffer to destination LBA.   |

|               | trim()              | Deletes (or discards) the mapping in FTL for the       |

|               |                     | passed LBA range.                                      |

|               | exists()            | Returns the presence of FTL mapping for the passed     |

| Sparse        |                     | LBA.                                                   |

| Sparse        | range_exist()       | Returns the subset of LBA ranges that are mapped in    |

|               |                     | the FTL.                                               |

|               | ptrim()             | Persistently deletes the mapping in FTL for the passed |

|               |                     | LBA range.                                             |

|               | iterate()           | Returns the next populated LBA starting from the       |

|               |                     | passed LBA.                                            |

|               | atomic_read()       | Executes read for a contiguous LBAs as an ACID         |

|               |                     | transaction.                                           |

| Transactional | atomic_exists()     | Executes exists for a contiguous LBAs as an ACID       |

|               |                     | transaction.                                           |

| Persistence   | atomic_write()      | Executes write of a contiguous LBAs as an ACID         |

|               |                     | transaction.                                           |

|               | atomic_ptrim()      | Executes ptrim of a contiguous LBAs as an ACID         |

|               |                     | transaction.                                           |

| Conditional   | cond_atomic_write() | Execute the atomic_write only if a condition is satis- |

| Conditional   |                     | fied.                                                  |

|               | cond_range_read()   | Returns the data only from a subset of LBA ranges      |

|               |                     | that are mapped in the FTL.                            |

| Batching      |                     | Operations within each category can be batched and     |

|               |                     | executed in the FTL.                                   |

Table 4.2: **FTL Primitive Interface** *Enhanced FTL capabilities that NVMKV builds upon.*

## 4.3.4 NVMKV Consumer API

NVMKV's consumer applications interact with the library through the NVMKV API. We held discussions with the creators and vendors of several scale out KV stores to identify a set of operations commonly needed in a KV store. These operations formed the NVMKV

API and they fall under five broad categories based on the functionality they provide. The categories are: *basic*, *iterate*, *pools*, *batching*, and *management*.

Table 4.1 presents the overview of the NVMKV API. We leverage the FTL's ability to provide enhanced operations such as *Atomic Writes* to provide transactional guarantees in NVMKV operations. Most existing KV stores do not offer such guarantees for their operations, and adopt more relaxed semantics such as eventual consistency to provide higher performance. On the other hand, we found that our approach enabled us to provide transactional guarantees with no loss of performance. We believe such guarantees can be of use to specific classes of applications as well as for simplifying the store logic contained within such applications. For instance, atomic KV operations imply that applications no longer need to be concerned with partial updates to flash.

The *Basic* and *Iterate* categories contain common features provided by many KV stores today. The *Pools* category interfaces allow for grouping KV pairs into buckets that can be managed separately within an NVMKV store. Pools provide the ability to transparently run multiple KV stores within the same FTL (discussed in more detail in § 4.6). The *Batching* category interfaces allow for group operations both within and across *Basic*, *Iterate*, and *Pools* categories, a common requirement in KV stores [BFPS11]. Finally, the *Management* category provides interfaces to perform KV store management operations.

## 4.4 Overview and FTL Integration

NVMKV's design is closely linked to the advanced capabilities provided by modern FTLs. Before describing its design in more detail, we provide a simple illustrative example of NVMKV's operation and discuss the advanced FTL capabilities that NVMKV leverages.

## 4.4.1 Illustrative Overview

To illustrate the principles behind NVMKV's design simply, we now walk through how a get, a put, and a delete operation are handled. We assume the sizes of keys and values are fixed and then address arbitrary sizes when we discuss design details (§4.5).

By mapping all KV operations to FTL operations, NVMKV eliminates any additional KV metadata in memory. To handle puts, NVMKV computes a hash on the key and uses the hash value to determine the location (i.e., LBA) of the KV pair. Thus, a put operation gets mapped to a write operation inside the FTL.

A get operation takes a key as input and returns the value associated with it (if the key exists). During a get operation, a hash of the key is computed first to determine the starting LBA of the KV pair's location. Using the computed LBA, the get operation is translated to a read operation to the FTL wherein the size of the read is equal to the combined sizes of the key and value. The stored key is matched with the key of the get operation and in case of a match, the associated value is returned.

To handle a delete operation, the given key is hashed to compute the starting LBA of the KV pair. Upon confirming that the key stored at the LBA is the key to be deleted, a discard operation is issued to the FTL for the range of LBAs containing the KV pair.

In this simplistic example, translating existing KV operations to FTL operations is straightforward and the KV store becomes a thin layer offloading most of its work to the underlying FTL with no in-memory metadata. However, additional work is needed to handle hash collisions in the LBA space and persisting discard operations.

## 4.4.2 Leveraging FTL Capabilities

We now describe the advanced FTL capabilities that are available and also extended to enable NVMKV. Many of these advanced FTL capabilities have already been used in

other applications [DAT<sup>+</sup>14, JBLF12, ONW<sup>+</sup>11, SSZ12, YPG<sup>+</sup>13]. The FTL interface available to NVMKV is detailed in Table 4.2.

#### **Dynamic Mapping**

Conventional SSDs provide a dense address space, with one logical address for every advertised available physical block. This matches the classic storage model, but forces applications to maintain separate indexes to map items to the available LBAs. *Sparse address spaces* are available in advanced FTLs which allow applications to address the device via a large, thinly provisioned, virtual address space [ONW+11, SSZ12, YPG+13]. Sparse address entries are allocated physical space only upon a write. In the NVMKV context, a large address space enables simple mapping techniques such as hashing to be used with manageable collision rates.

Additional primitives are required to work with sparse address spaces. EXISTS queries whether a particular sparse address is populated. PTRIM is a persistent and atomic deletion of the contents at a sparse address. These primitives can be used for individual, or ranges of, locations. For example, RANGE-EXISTS returns a subset of a given virtual address range that has been populated. The ITERATE primitive is used to cycle through all populated virtual addresses, whereby ITERATE takes a virtual address and returns the next populated virtual address.

#### **Transactional Persistence**

The transactional persistence capabilities of the FTL are provided by ATOMIC-WRITE and PTRIM [DAT+14, JBLF12]. ATOMIC-WRITE allows a sparse address range to be written as a single ACID compliant transaction.

#### **Optimized Parallel Operations**

The FTL is well-placed to optimize simultaneous device-level operations. Two classes of FTL primitives, *conditional* and *batch*, provide atomic parallel operations that are well-utilized by NVMKV. For example, <code>cond\_atomic\_write</code> allows for an atomic write to be completed only if a particular condition is satisfied, such as the LBA being written to is not already populated. This primitive removes the need to issue separate <code>exists</code> and <code>atomic\_write</code> operations. Batch or vectored versions of all primitives are also implemented into the FTL (such as <code>batch\_read</code>, <code>batch\_atomic\_write</code>, and <code>batch\_ptrim</code>) to amortize lock acquisition and system call overhead. The benefits of batch (or vector) operations have been explored earlier [VKA12b].

### 4.5 Design Description

NVMKV implements novel techniques to make sparse addressing practical and efficient for use in KV stores and for providing low-latency, transactional persistence.

# 4.5.1 Mapping Keys via Hashing

Conventional KV stores employ two layers of translations to map keys to flash device locations, both of which need to be persistent [Mon14, Roc14, AFK<sup>+</sup>09]. The first layer translates keys to LBAs. The second layer (i.e., the FTL) translates the LBAs to physical locations in flash device. NVMKV leverages the FTLs sparse address space and encodes keys into sparse LBAs via hashing, thus collapsing an entire layer.

NVMKV divides the sparse address into equal sized virtual slots, each of which stores a single KV pair. More specifically, the sparse address space (with addressability through N bits) is divided into two areas: the *Key Bit Range* (KBR) and the *Value Bit Range*

Figure 4.3: Hash model used in NVMKV. The arguments to the functions represent k:key, v:value, and pid:pool\_id.

(VBR). This division can be set by the user at the time of creating the NVMKV store. The VBR defines the amount of contiguous address space (i.e., maximum value size or virtual slot size) reserved for each KV pair. The KBR determines the maximum number of such KV pairs that can be stored in a given KV store. In the expected use cases, the sparse virtual address range provided by the KBR will still be several orders of magnitude larger than the number of KV pairs as limited by the physical media.

The keys are mapped to LBAs through a simple hash model as shown in Figure 4.3. User supplied keys can be of variable length up to the maximum supported key size. To handle a put operation, the specified key is hashed into an address which also provides its KBR value. The maximum size of the information (Key, Value, metadata) that can be stored in a given VBR is half of the size addressed by the VBR. For example, if the VBR is 11 bits and each address represents a 512B sector, a given VBR value can address 2 MB.

The above layout guarantees the following two properties. First, each VBR contains exactly one KV pair, ensuring that we can quickly and deterministically search and identify KV pairs stored in the flash device. Second, no KV pairs will be adjacent in the sparse address space. In other words, there is always unpopulated virtual addresses between ev-

ery KV pair. This deliberately wasted virtual space does not translate into unutilized storage since it is in virtual and physical space. These two properties are critical for NVMKV as the value size and exact start location of the KV pair are not stored as part of NVMKV metadata but are inferred via the FTL. Doing so helps in significantly reducing the in-memory metadata footprint of NVMKV. Non-adjacent KV pairs in the sparse address space help in determining the value size along with the starting virtual address of each KV pair. To determine the value size, NVMKV issues a range\_exist call to the FTL.

A direct consequence of this design is that every access pattern becomes a random pattern, losing any possible order in the key space. The decision to not preserve sequentiality was shaped by two factors: metadata overhead and flash I/O performance. To ensure sequential writes for contiguous keys, additional metadata would be required. This metadata would have to be consulted when reading, updated after writing, and cached in RAM to speed up the lookups. While straightforward to implement, doing so is unnecessary since the performance gap between random and sequential access for flash is ever decreasing; for current high performance flash devices, it is practically non-existent.

# 4.5.2 Handling Hash Collisions

Hashing variable sized keys into fixed size virtual slots could result in collisions. Since each VBR contains exactly one KV pair, hash conflicts only occur in the KBR. To illustrate the collision considerations, consider the following example. A 1TB Fusion-io ioDrive can contain a maximum of  $2^{31}$  (2 billion) keys. Given a 48 bit sparse address space with 36 bits for KBR and 12 bits for VBR, NVMKV would accommodate  $2^{36}$  keys with a maximum value size of 512KB. Under the simplifying assumption that our hash function uniformly distributes keys across the value ranges, for a fully-utilized 1TB io-

Drive, the chances of a new key insertion resulting in a collision is  $1/2^5$  or a little under 3 percent.

NVMKV implicitly assumes that the number of KBR values is sufficiently large, relative to the number of keys that can be stored in a flash device, so that the chances of a hash collision are small. If the KV pair sizes are increased, the likelihood of a collision reduces because the device can accommodate fewer keys while preserving the size of the key address space. If the size of the sparse address space is reduced, the chances of a collision will increase. Likewise, if the size of the flash device is increased without increasing the size of its sparse address space, the likelihood of a collision will increase.

Collisions are handled deterministically by computing alternate hash locations using either linear or polynomial probing. By default, NVMKV uses polynomial probing and up to eight hash locations are tried before NVMKV refuses to accept a new key. With this current scheme, the probability of a put failing due to hash failure is vanishingly small. Assuming that the hash function uniformly distributes keys, the probability of a put failing equals the probability of 8 consecutive collisions. This is approximately  $(1/2^5)^8 = 1/2^{40}$ , roughly one failure per trillion put operations. The above analysis assumes that the hash function used is well modeled by a uniformly distributing random function. Currently, NVMKV uses the FNV1a hash function [FNV91] and we experimentally validated our modeling assumption.

# 4.5.3 Caching

Caching is employed in two distinct ways within NVMKV. First, a read cache speeds up access to frequently read KV pairs. NVMKV's read cache implementation is based on LevelDB's cache [GD11]. The read cache size is configurable at load time. Second, NVMKV uses a collision cache to improve collision handling performance. It caches

#### NVMKV layout on a sparse block layer

Figure 4.4: NVMKV layout

the key hash (the sparse LBA) along with the actual key which is used during puts (i.e., inserts or updates). If the cached key matches the key to be inserted, the new value can be stored in the corresponding slot (the key's hash value). This significantly reduces the number of additional I/Os needed during collision resolution. In most cases, only a single I/O is needed for a get or a put to return or store the KV pair.

# 4.5.4 KV Pair Storage and Iteration

KV pairs are directly mapped to a physical location in the flash device and addressable through the FTL's sparse address space. In our current implementation, the minimum unit of storage is a sector and KV pairs requiring less than 512B will consume a full 512B sector. Each KV pair also contains metadata stored on media. The metadata layout is shown in Figure 4.4; it includes the length of the key, the length or the value, pool identifier (to be discussed further in §4.6), and other information.

To minimize internal fragmentation, NVMKV packs and stores the metadata, the key, and the value in a single sector whenever possible. If the size of the KV pair and the metadata is greater than a sector, NVMKV packs the metadata and key into the first sector and stores the value starting from the second sector. This layout allows for optimal

storage efficiency for small values and zero-copy data transfer into the users buffer for larger values.

NVMKV supports unordered iteration through all KV pairs stored in the flash device. Key iteration is accomplished by iterating across the populated virtual addresses inside the FTL in order. The iterator utilizes the ITERATE primitive in the FTL, which takes in the previously reported start virtual address and returns the start address of the next contiguously populated virtual address segment in the sparse address space. Note that this approach relies on the layout guarantee that each KV pair is located contiguously in a range of virtual addresses, and that there are unpopulated virtual addresses in between each KV pair.

## 4.5.5 Optimizing KV Operations

NVMKV's design goal is one I/O for a get or a put operation. For get, this is achieved with the KV data layout and the CONDITIONAL-RANGEREAD primitive. The layout guarantees that individual KV pairs occupy a single contiguous section of the sparse address space, separated from other KV pairs by unpopulated virtual addresses. Given this, a CONDITIONAL-RANGEREAD can retrieve the entire KV pair in one operation without knowing the size of the value up front. Second, collisions induce a minimal number of additional operations. Since get and put operations for a given key map to hash addresses in a deterministic order, and since put places the new KV pair at the first available hash address (that is currently unused) in this order, subsequent gets are guaranteed to retrieve the most recent data written to this key. Finally, DELETE operations may require more than one I/O per operation, since they are required to read and validate the key before issuing a PTRIM. It also needs to check multiple locations to ensure that previous instances of a particular key have all been deleted.

NVMKV is intended to be zero copy and avoid memory comparison operations wherever possible. First, for any value that is large enough to start at its own sector, the data retrieved from a get (or written during a put) operation will be transferred directly to (or from) the user provided memory buffer. Second, no key comparisons occur unless the key hashes match. Given that the likelihood of collisions is small, the number of key comparisons that fail is also correspondingly small.

### 4.6 Multiple KV Instances Via Pools

Pools in NVMKV allow applications to group related keys into logical abstractions that can then be managed separately. Besides simplifying KV data management for applications, pools enable efficient access and iteration of related keys. The ability to categorize or group KV pairs also improves the lifetime of flash devices.

### 4.6.1 Need for Pools

NVMKV as described thus far, can support multiple independent KV stores. However, it would need to either partition the physical flash device to create multiple block devices each with its own sparse address space or logically partition the single sparse address space to create block devices to run multiple instances of KV stores.

Unfortunately, both approaches do not work well for flash. Since it is difficult to predict the number of KV pairs or physical storage needed in advance, static partitioning would result in either underutilization or insufficient physical capacity for KV pairs. Further, smaller capacity physical devices would increase pressure on the garbage collector, resulting in both increased write amplification and reduced KV store performance. Alternatively, partitioning the LBA space would induce higher key collision rates as the KBR would be shrunk depending on the number of pools that need to be supported.

## 4.6.2 Design Overview

NVMKV encodes pools within the sparse LBA to avoid any need for additional inmemory pool metadata. The encoding is done by directly hashing both the pool ID and the key to determine the hash location within the KBR. This ensures that all KV pairs are equally distributed across the sparse virtual address space regardless of which pool they are in. Distributing KV pairs of multiple pools evenly across the sparse address space not only retains the collision probability properties but also preserves the get and put performance with pools.

Pool IDs are also encoded within the VBR to optimally search or locate pools within the sparse address space. Encoding pool IDs within the VBR preserves the collision properties of NVMKV. The KV pair start offset within the VBR determines the Pool ID. The VBR size determines the maximum number of pools that can be addressed without hashing, while also maintaining the guarantee that each KV pair is separated from neighboring KV pairs by unpopulated sparse addresses. For example, with a 12 bit VBR, the maximum number of pools that can be supported without pool ID hashing is 1024. If the maximum number of pools is greater than 1024, the logic of get is modified to also retrieve the KV pair metadata that contains the pool ID now needed to uniquely identify the KV pair.

# 4.6.3 Operations

Supporting pools requires changes to common operations of the KV store. We now describe three important operations in NVMKV that have either been added or significantly modified to support pools.

**Creation and Deletion:** Pool creation is a lightweight operation. The KV store performs a one-time write to record the pool's creation in its persistent configuration meta-

data. On the other hand, pool deletion is an expensive operation since all the KV pairs of a pool are distributed across the entire LBA space, each requiring an independent PTRIM operation. NVMKV implements pool deletion as an asynchronous background operation. Upon receiving the deletion request, the library marks the pool as invalid in its on-drive metadata, and the actual deletion of pool data occurs asynchronously.

**Iteration:** NVMKV supports iteration of all KV pairs in a given pool. If no pool is specified, all key-value pairs on the device are returned by the iteration routines. Iteration uses the ITERATE primitive of the FTL to find the address of the next contiguous chunk of data in the sparse address space. During pool iteration, each contiguous virtual address segment is examined as before. However, the iterator also examines the offset within the VBR of each starting address, and compares it to the pool ID, or the hash of the pool ID, for which iteration is being performed. Virtual addresses are only returned to the KV store if the pool ID match succeeds.

NVMKV guarantees that each KV pair is stored in a contiguous chunk, and that adjacent KV pairs are always separated by at least one empty sector, so the address returned by ITERATE locates the next KV pair on the drive (see §4.5.1). When the maximum number of pools is small enough that each pool ID can be individually mapped to a distinct VBR offset, the virtual addresses returned by the ITERATE primitive are guaranteed to belong to the pool currently being iterated upon. When the maximum number of pools is larger, the ITERATE uses the hash of the pool ID for comparison. In this case, the virtual addresses that match are not guaranteed to be part of the current pool, and a read of the first sector of the KV pair is required to complete the match.

## 4.7 Implementation

NVMKV is implemented as a stand-alone KV store written in C++ using 6300 LoC. Our current prototype works on top of ioMemory VSL and interacts with the FTL using the IOCTL interface [Fus]. The default subdivision for KBR and VBR used in the current implementation is 36 bits and 12 bits respectively, in a 48 bit address space. The KBR/VBR subdivision is also configurable at KV store creation time. To accelerate pool iteration, we implemented filters inside the ITERATE/BATCH-ITERATE FTL primitives. During the iteration of keys from a particular pool, the hash value of the pool is passed along with the IOCTL arguments to be used as a filter for the iteration. The FTL services (BATCH-) ITERATE by returning only populated ranges that match the filter. This reduces data copying across the FTL and NVMKV.

## **4.7.1** Extending FTL Primitives