# Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-31-2016

# Advanced Graphene Microelectronic Devices

Chowdhury G. Al-Amin calam003@fiu.edu

DOI: 10.25148/etd.FIDC000252

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the <u>Electrical and Electronics Commons</u>, <u>Electronic Devices and Semiconductor</u> Manufacturing Commons, and the <u>Nanotechnology Fabrication Commons</u>

## **Recommended** Citation

Al-Amin, Chowdhury G., "Advanced Graphene Microelectronic Devices" (2016). *FIU Electronic Theses and Dissertations*. 2512. https://digitalcommons.fiu.edu/etd/2512

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fu.edu.

FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# ADVANCED GRAPHENE MICROELECTRONIC DEVICES

A dissertation submitted in partial fulfillment of the

requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

## ELECTRICAL ENGINEERING

by

Chowdhury G. Al-Amin

2016

To: Interim Dean Ranu Jung College of Engineering and Computing

This dissertation, written by Chowdhury G. Al-Amin, and entitled Advanced Graphene Microelectronic Devices, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommended that it be approved.

Sakhrat Khizroev

Chunlei Wang

Irene Calizo

Faisal Jahan

Nezih Pala, Major Professor

Date of Defense: March 31, 2016

The dissertation of Chowdhury G. Al-Amin is approved.

Interim Dean Ranu Jung College of Engineering and Computing

Andrés G. Gil Vice President for Research and Economic Development and Dean of the University Graduate School

Florida International University, 2016

© Copyright 2016 by Chowdhury G. Al-Amin

All rights reserved.

# DEDICATION

I dedicate this thesis to my family. Without their patience, understanding, support and most of all love, the completion of this work would not have been possible.

#### ACKNOWLEDGMENTS

I wish to thank the members of my committee for their support and patience. Their firm but gentle direction has been most appreciated. Dr. Sakhrat Khizroev, Dr. Chunlei Wang and Dr. Irene Calizo were very helpful in guiding me toward a qualitative methodology. Dr. Faisal Jahan's expertise in Capacitively Coupled Contacts and on-wafer RF measurement was the impetus for my proposal. Finally, I would like to thank my major professor, Dr. Nezih Pala. From the beginning, he had confidence in my abilities to not only complete a degree, but to complete it with excellence. His continuous support with patience made this dissertation possible.

I would like to thank my funding sources. I received grant from Army Research Office; without that support, I would not have been able to conduct my doctoral Research. I was also supported by an NSF CAREER AWARD (N. Pala), Dissertation Year Fellowship from University Graduate School, FIU, and three travel awards from The Graduate & Professional Student Committee (GPSC), FIU.

#### ABSTRACT OF THE DISSERTATION

#### ADVANCED GRAPHENE MICROELECTRONIC DEVICES

by

Chowdhury G. Al-Amin

Florida International University, 2016

Miami, Florida

Professor Nezih Pala, Major Professor

The outstanding electrical and material properties of Graphene have made it a promising material for several fields of analog applications, though its zero bandgap precludes its application in digital and logic devices. With its remarkably high electron mobility at room temperature, Graphene also has strong potential for terahertz (THz) plasmonic devices. However there still are challenges to be solved to realize Graphene's full potential for practical applications.

In this dissertation, we investigate solutions for some of these challenges. First, to reduce the access resistances which significantly reduces the radio frequency (RF) performance of Graphene field effect transistors (GFETs), a novel device structure consisting of two additional contacts at the access region has been successfully modeled, designed, microfabicated/integrated, and characterized. The additional contacts of the proposed device are capacitively coupled to the device channel and independently biased, that induce more carriers and effectively reduce access resistance. In addition to that, in this dissertation, bandgap has been experimentally introduced to semi-metallic Graphene, by decorating with randomly distributed gold nano-particles and zinc oxide (ZnO) nano-seeds, where their interaction breaks its sublattice symmetry and opens up bandgap. The engineered bandgap was extracted from its temperature dependent conductivity characteristics and compared with reported theoretical estimation. The proposed method of device engineering combined with material bandgap engineering, on a single device, introduces a gateway towards high speed Graphene logic devices.

Finally, THz plasmon generation and propagation in Graphene grating gate field effect transistors and Graphene plasmonic ring resonators have been investigated analytically and numerically to explore their potential use for compact, solid state tunable THz detectors.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

| CHAPTER                                                                                         | PAGE |

|-------------------------------------------------------------------------------------------------|------|

| I. INTRODUCTION                                                                                 | 1    |

| 1.1 Graphene Material Overview                                                                  |      |

| 1.2 Prospect of Graphene as an Electronic Material                                              |      |

| 1.3 Effect of Zero Bandgap Graphene as Channel Material                                         |      |

|                                                                                                 |      |

| II. GRAPHENE FET WITH IMPROVED CONTACT RESISTANCE                                               | 12   |

| 2.1 Introduction                                                                                | 13   |

| 2.2 Theory                                                                                      |      |

| 2.2.1 Current Gain and Current Gain Cut-off Frequency                                           | 15   |

| 2.2.2 Small Signal Circuit Analysis of Regular Graphene FET                                     |      |

| 2.2.3 Small Signal Circuit Analysis of Top FCE GFET                                             |      |

| 2.2.4 Small Signal Circuit Analysis of Bottom FCE GFET                                          |      |

| 2.2.5 Small Signal Circuit Analysis of Hybrid Contact GFET                                      |      |

| 2.3 Simulation of GFET with FCEs                                                                |      |

| 2.3.1 Simulation of Top FCE GFET                                                                |      |

| 2.3.2 Simulation of Bottom FCE GFET                                                             |      |

| 2.3.3 Simulation of Hybrid Contact GFET                                                         |      |

| 2.4 Fabrication/Integration of GFET                                                             |      |

| 2.4.1 Theory of Microfabrication                                                                |      |

| 2.4.2 Fabrication of GFET: Process Details                                                      |      |

| 2.5 Characterization of GFET                                                                    |      |

| 2.6 Conclusion                                                                                  | 66   |

|                                                                                                 | (7   |

| III. BANDGAP ENGINEERING OF GRAPHENE                                                            |      |

| 3.1 Introduction                                                                                |      |

| 3.2 Theory of Bandgap Opening                                                                   |      |

| 3.3 Method                                                                                      |      |

| 3.4 Fabrication of Decorated Single Layer Graphene                                              |      |

| 3.4.1 Graphene Decorated with ZnO Nano-Seed<br>3.4.2 Graphene Decorated with Gold Nanoparticles |      |

| 3.5 Bandgap Measurement of Decorated Graphene                                                   |      |

| 3.6 Conclusion                                                                                  |      |

|                                                                                                 |      |

| IV. GRAPHENE THz DETECTOR                                                                       |      |

| 4.1 Graphene Grating Gate THz Detector                                                          |      |

| 4.1.1 Introduction                                                                              |      |

| 4.1.2 Theory                                                                                    |      |

| 4.1.3 Simulation and Results                                                                    |      |

| 4.2 Graphene THz Plasmonic Ring Resonators                                                      |      |

| 4.2.1 Introduction                                                                              |      |

| 4.2.2 Simulation and Results                                                                    |      |

| 4.3 Conclusion                | 93  |

|-------------------------------|-----|

| V. CONCLUSION AND FUTURE WORK | 95  |

| 5.1 Conclusion                |     |

| 5.2 Future Work               |     |

|                               |     |

| REFERENCES                    |     |

|                               |     |

| APPENDICES                    |     |

|                               |     |

| VITA                          | 119 |

| L | <b>IST</b> | OF | FIG | URES |

|---|------------|----|-----|------|

|---|------------|----|-----|------|

| FIGURE PAGE                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. SP2 hybridization in Graphene                                                                                                                                    |

| 2. (a) Fullerine, (b) Carbon Nanotube, (c) Graphene, and (d) Graphite                                                                                               |

| 3. Honeycomb lattice structure of Graphene, made out of two interpenetrating triangular lattice                                                                     |

| 4. Energy-Momentum relation of (a) conventional semiconductor (b) Graphene5                                                                                         |

| 5. Graphene based transparent and flexible electronics                                                                                                              |

| 6. Graphene nanowire gate GFET                                                                                                                                      |

| 7. Schematic of THz plamsonic detectors based on Graphene                                                                                                           |

| 8. Band structure of insulators, semiconductors, metals and Graphene10                                                                                              |

| 9. Relation between current gain,  h21  and frequency                                                                                                               |

| 10. Schematic of a conventional 3-terminal GFET on SiO <sub>2</sub> with the small-signal equivalent circuit laid on top                                            |

| 11. Intrinsic and parasitic time delays vs. gate length of In <sub>0.7</sub> Ga <sub>0.3</sub> As-channel HEMTs reproduced from                                     |

| 12. (a) Small signal equivalent circuit overlaid on top of top FCE GFET (b)<br>Schematic of the proposed top FCE GFET (not in scale)21                              |

| 13. Schematic of the proposed GFET with 2 bottom FCEs at the ungated region23                                                                                       |

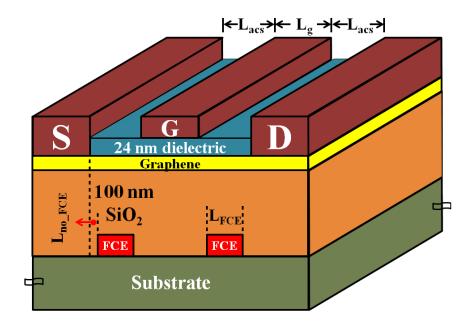

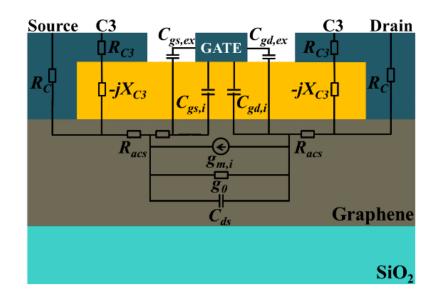

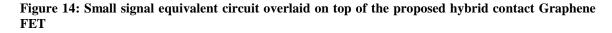

| 14. Small signal equivalent circuit overlaid on top of the proposed hybrid contact<br>Graphene FET                                                                  |

| 15. (a) Matching Network-1 (b) Matching Network-2                                                                                                                   |

| 16. Schematic of a RF TLM structure on Graphene with small-signal equivalent circuit overlaid on top and the equivalent 2-port network                              |

| 17. (a) Schematic of the baseline GFET-A, (b) DC and RF characteristics (Current Gain,  h21  and Unilateral Power Gain, UPG) of the baseline GFET-A from simulation |

| 18. RF characteristics of both GFET-A and GFET-B with $V_{FCE}$ =-3V and $V_{gs}$ =-2V.<br>Inset shows the Id-Vd characteristics of GFET-A & B with VFCE in hole<br>transportation ragime at $V_{res}$ = 2V considering concentration dependence of the hole                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| transportation regime at $V_{gs}$ =-2V considering concentration dependence of the hole mobility                                                                                                                                                                                                                                                                   |

| 19. Improvement of $f_T$ with $V_{FCE}$ for both GFET-A and GFET-B in hole regime32                                                                                                                                                                                                                                                                                |

| 20. Improvement of $f_T$ with $V_{FCE}$ for both GFET-A and GFET-B in electron regime at $V_{gs}$ =6.0 V (numerical simulation results                                                                                                                                                                                                                             |

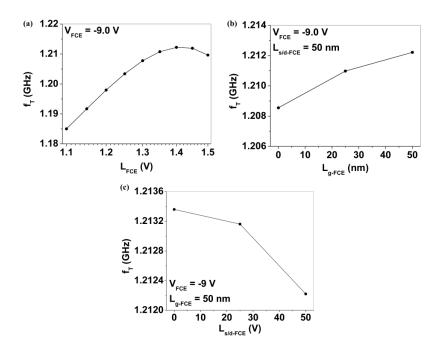

| 21. At $V_{FCE}$ = - 9 V (a) $f_T$ plotted against different $L_{FCE}$ . (b) At $L_{s/d-FCE}$ =50 nm, $f_T$ plotted against $L_{g-FCE}$ . (c) At $L_{g-FCE}$ = 50 nm, $f_T$ plotted against $L_{s/d-FCE}$                                                                                                                                                          |

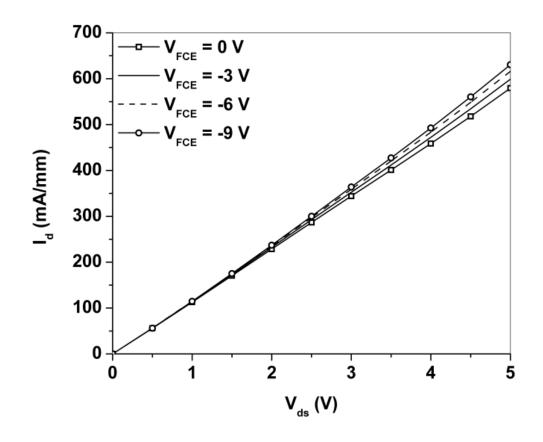

| 22. Increment of drain current with FCE bias at $V_{ds} = 5.0$ V and $V_{gs} = -2.0$ V                                                                                                                                                                                                                                                                             |

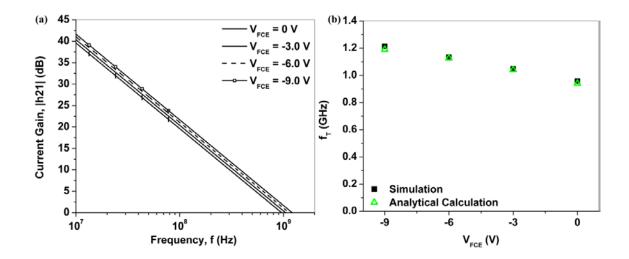

| 23. (a) Current gain $ h21 $ - frequency relationship of the GFET-A with FCEs at varying V <sub>FCE</sub> values in hole regime of operation. (b) f <sub>T</sub> vs. V <sub>FCE</sub> where f <sub>T</sub> is calculated using analytical technique and also extracted from (a)37                                                                                  |

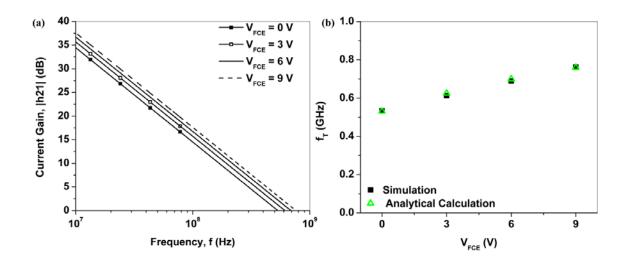

| 24. (a) Current Gain $ h21 $ - Frequency relationship of GFET-A with FCEs at different V <sub>FCE</sub> values in electron regime of operation. (b) $f_T$ vs. V <sub>FCE</sub> where $f_T$ is calculated using analytical technique and also extracted from (a)                                                                                                    |

| 25. Current Gain and Unilateral Power Gain vs. frequency of the short channel high mobility baseline GFET                                                                                                                                                                                                                                                          |

| 26. At V <sub>FCE</sub> = - 9 V (a) $f_T$ plotted against different L <sub>FCE</sub> . (b) At L <sub>s/d-FCE</sub> =150 nm, $f_T$ plotted against L <sub>g-FCE</sub> . (c) At L <sub>g-FCE</sub> = 150 nm, $f_T$ plotted against L <sub>s/d-FCE</sub> 40                                                                                                           |

| 27. Extracted $f_T$ from frequency response and from analytical calculations plotted against $V_{FCE}$ for (a) hole regime operation and (b) electron regime operation41                                                                                                                                                                                           |

| 28. (a) Schematic of the capacitor like structure (b) The real and imaginary part of impedance estimated from simulation and analytical calculation                                                                                                                                                                                                                |

| 29. (a) Schematic of RF TLM structure on Graphene. (b) The real and imaginary part of C3 impedance estimated from both simulation and analytical calculations plotted with respect to frequency                                                                                                                                                                    |

| 30. Schematic of the proposed GFET (not in scale)44                                                                                                                                                                                                                                                                                                                |

| 31. (a) Current Gain, $ h21 $ of the baseline GFET-1 along with that of the proposed<br>hybrid contact GFET in electron regime ( $V_{gs}$ =+2.0 V and $V_{ds}$ =+5.0 V) plotted with<br>respect to frequency (b) The current gain cut-off frequency ( $f_T$ ) of the proposed<br>GFET extracted from $ h21 vs$ f characteristics, plotted with respect to $L_{C3}$ |

| 32. (a) Current Gain, $ h21 $ of the baseline GFET-2 along with that of the proposed hybrid contact GFET in electron regime ( $V_{gs}$ =+0.6 V and $V_{ds}$ =+1.6 V) plotted with respect to frequency (b) The current gain cut-off frequency ( $f_T$ ) of the proposed                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| GFET extracted from $ h21 vs$ f characteristics, plotted with respect to $L_{C3}$                                                                                                                                                                                                                                                                                                              | 46 |

| 33. Layout design of 6 different layers                                                                                                                                                                                                                                                                                                                                                        | 56 |

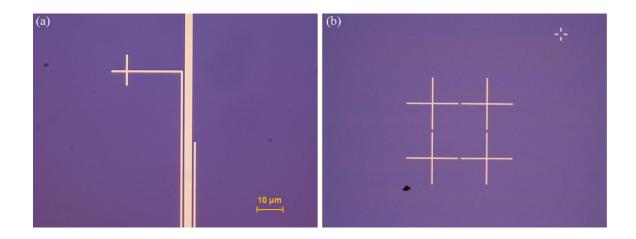

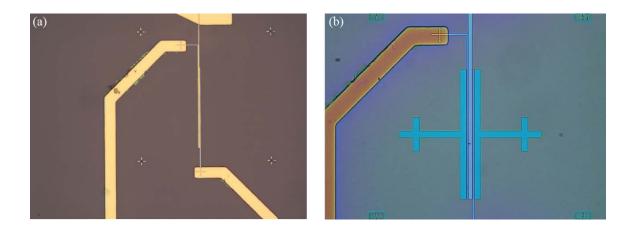

| <ul><li>34. Optical microscope image of (a) Gate-FCE layer after metallization and lift-off</li><li>(b) Alignment marks for mask alignment after metallization and lift-off</li></ul>                                                                                                                                                                                                          | 57 |

| 35. Optical microscope image of (a) Gate-FCE pad layer after metallization and lift-off, (b) Source/drain layer after metallization and lift-off                                                                                                                                                                                                                                               | 58 |

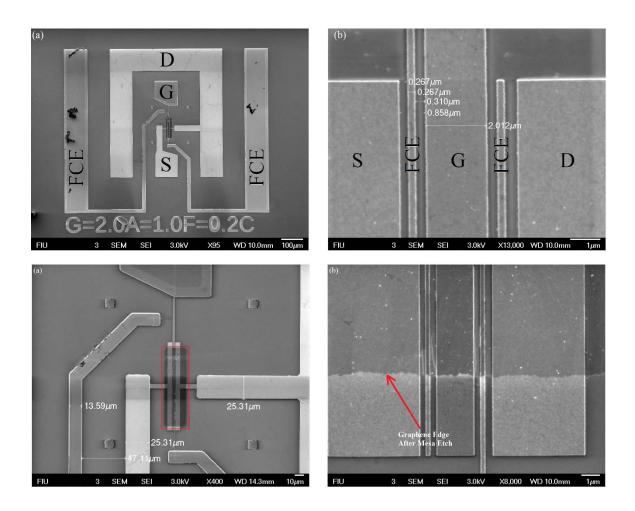

| 36. (a) SEM image of the GFET with source, drain, gate, and FCEs marked. The letters S, D, and G stand for source, drain, and gate respectively. (b) High magnification image of the device with embedded scale showing FCE length, gate length, and access region length, (c) The Graphene channel after mesa etch, marked with red rectangle, (d) a closer view of the Graphene channel edge | 59 |

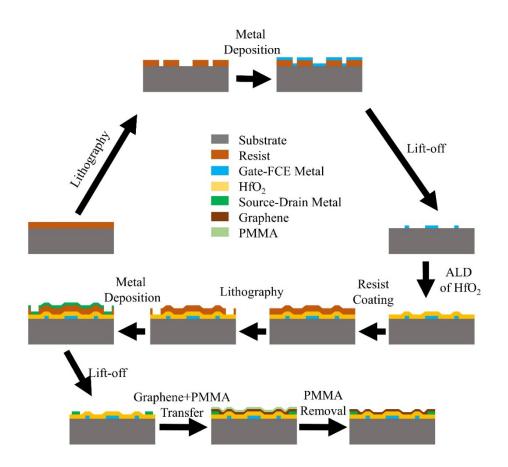

| 37. Simplified process flow of GFET fabrication/integration                                                                                                                                                                                                                                                                                                                                    | 60 |

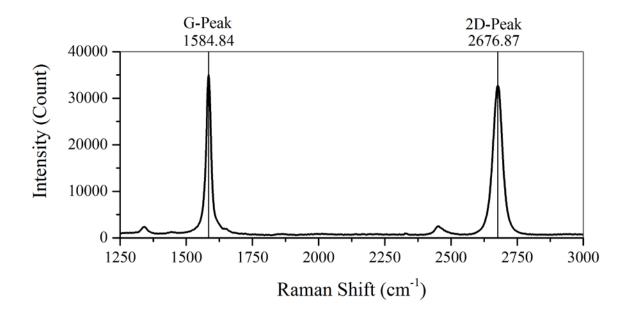

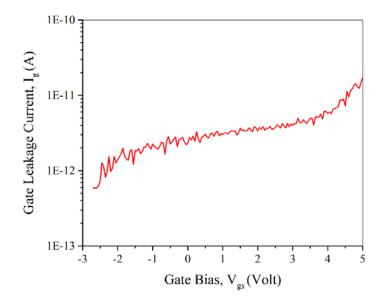

| 38. Raman spectrum of single layer Graphene forming FET channel                                                                                                                                                                                                                                                                                                                                | 61 |

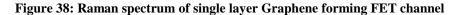

| 39. (a) The $I_d$ - $V_d$ characteristics of GFET at different $V_{FCE}$ (b) The $I_d$ - $V_g$ characteristics of GFET at different $V_{FCE}$                                                                                                                                                                                                                                                  | 62 |

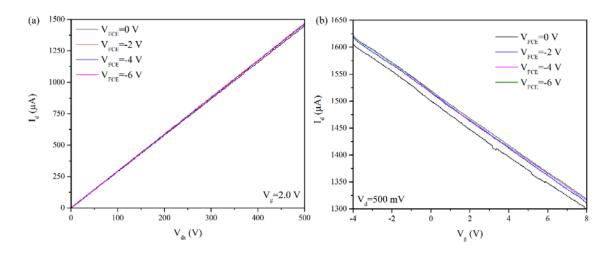

| 40. Gate leakage current                                                                                                                                                                                                                                                                                                                                                                       | 62 |

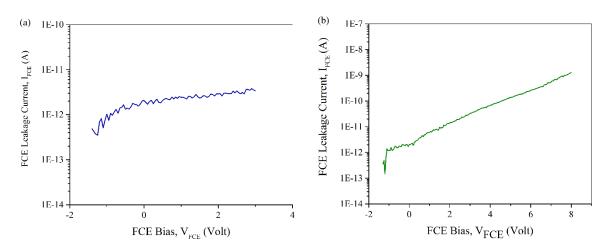

| 41. Leakage current of (a) FCE-1 and (b) FCE-2                                                                                                                                                                                                                                                                                                                                                 | 63 |

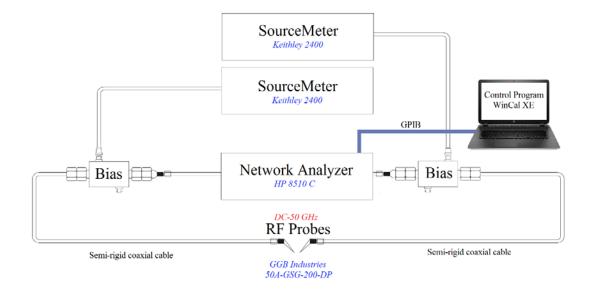

| 42. Schematic of the S-parameter measurement setup                                                                                                                                                                                                                                                                                                                                             | 63 |

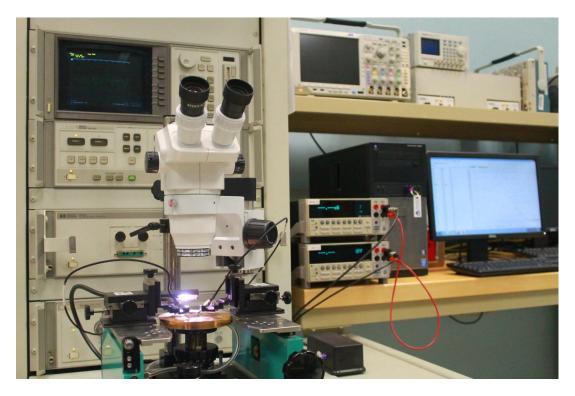

| 43. A picture of RF measurement Setup                                                                                                                                                                                                                                                                                                                                                          | 64 |

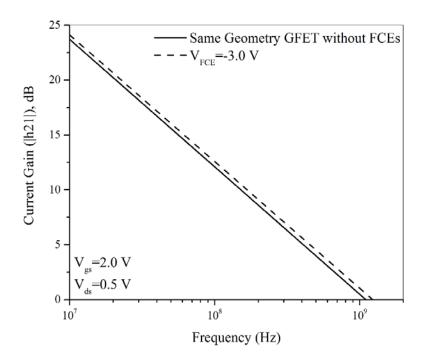

| 44. Current gain of a conventional 3 terminal GFET along with that of a same geometry proposed GFET plotted with respect to frequency for comparison                                                                                                                                                                                                                                           | 65 |

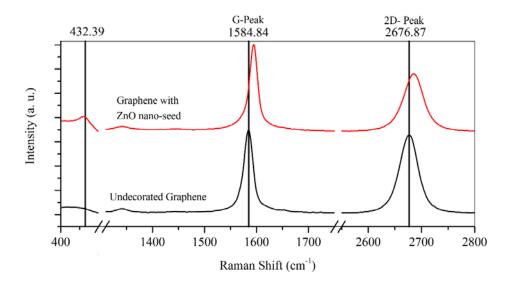

| 45. Raman spectra of pristine and ZnO nano-seed decorated single layer Graphene                                                                                                                                                                                                                                                                                                                | 71 |

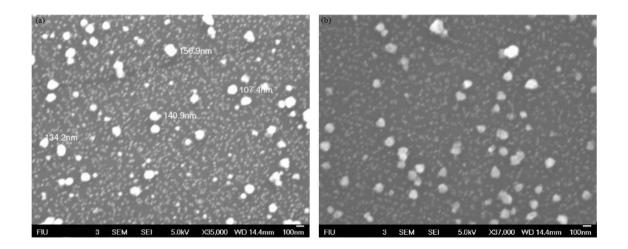

| 46. SEM image of ZnO nano-seed decorated single layer Graphene at two different magnifications                                                                                                                                                                                                                                                                                                 | 72 |

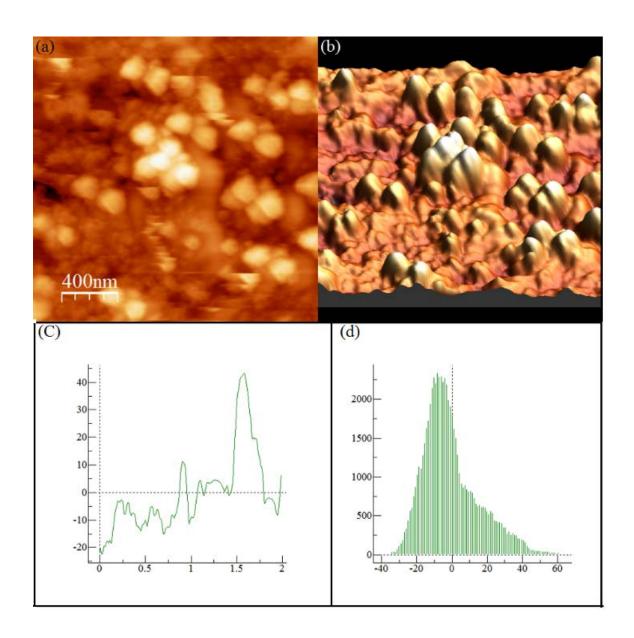

| <ul><li>47. AFM image of ZnO nano-seed decorated single layer Graphene. (a) 2D image.</li><li>(b) 3D image. (c) The profile along a straight line. (d) Roughness analysis: RMS Roughness= 15.85 nm and Average Roughness= 12.34 nm</li></ul>                                                                                                                                                   | 73 |

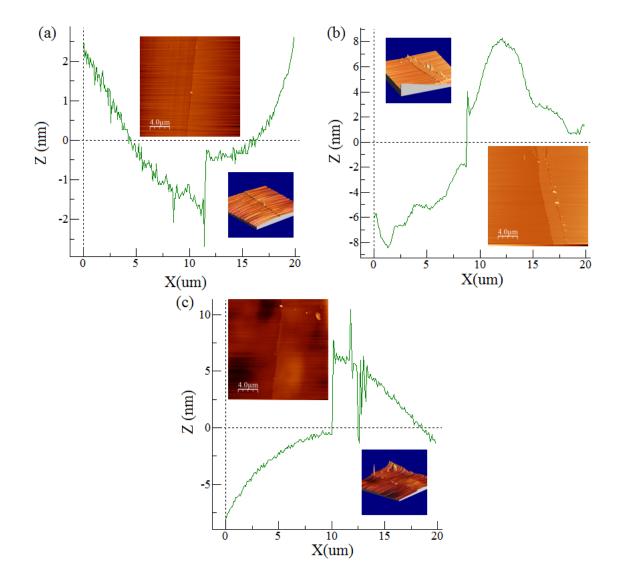

| <ul><li>48. The profile of the step at the edge of sputtered gold thin film on (a) Sample-A,</li><li>(b) Sample-B, and (c) Sample-C, measured by Atomic Force Microscopy (AFM) with 2D and 3D views (inset)</li></ul>                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

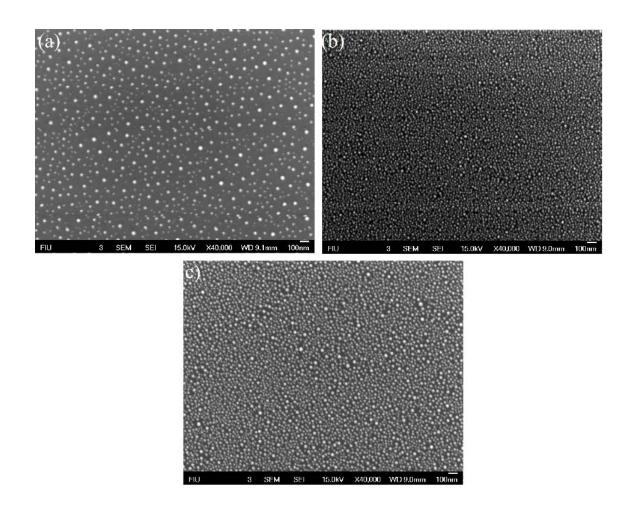

| 49. SEM image of gold nanoparticles grown on SiO <sub>2</sub> of (a) Sample-A, (b)<br>Sample-B, and (c) Sample-C75                                                                                                                                                                                                                                        |

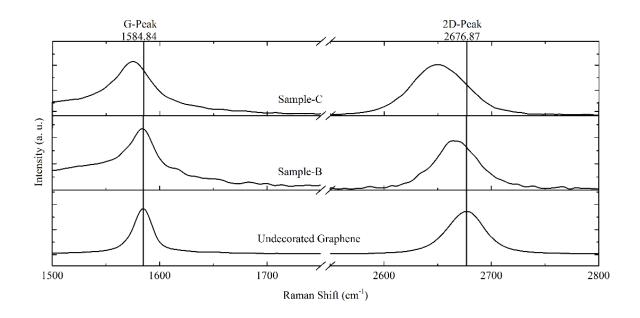

| 50. Raman spectrum of undecorated Graphene and decorated Graphene:<br>Samples-B, C                                                                                                                                                                                                                                                                        |

| 51. A picture of the temperature dependent conductivity measurement setup77                                                                                                                                                                                                                                                                               |

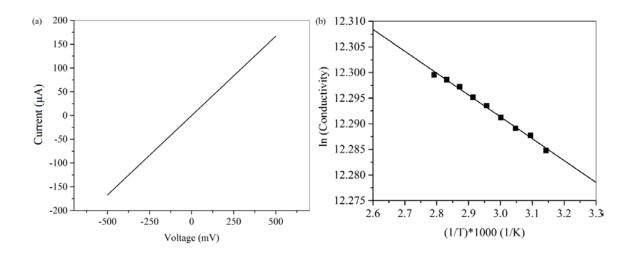

| 52. (a) The current-voltage characteristics of the ZnO nano-seed decorated<br>Graphene at various temperatures, (b) The temperature dependent conductivity<br>property                                                                                                                                                                                    |

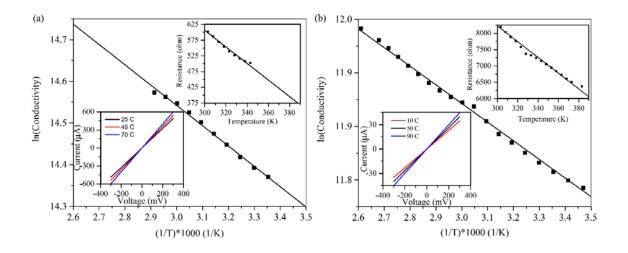

| 53. The temperature dependent conductivity curve of (a) Sample-B and (b)<br>Sample-C, with corresponding current-voltage characteristics at different<br>temperatures and temperature-resistance characteristics, inset                                                                                                                                   |

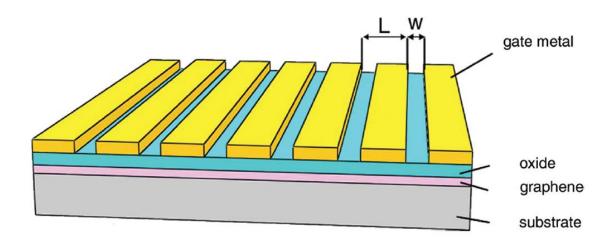

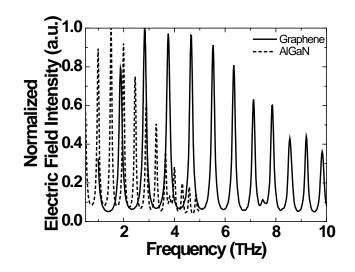

| 54. Cross section of the studied structures (not to scale)                                                                                                                                                                                                                                                                                                |

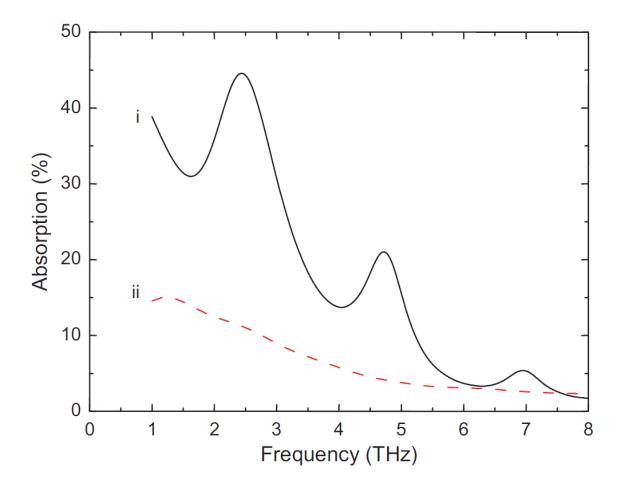

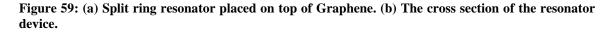

| 55. Room temperature absorption spectra of AlGaN/GaN and Graphene grating gate FET structures with L = 1.5 $\mu$ m, w = 0.15 $\mu$ m, N <sub>S</sub> = 7.5×1012 cm <sup>-2</sup> . (i) Graphene (ii) Al <sub>0.2</sub> Ga <sub>0.8</sub> N/GaN                                                                                                            |

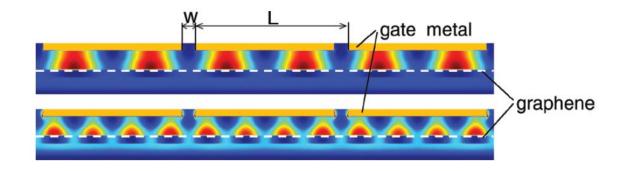

| 56. Electric field distribution for the first mode (top) and second mode (bottom) of plasmon resonances in Graphene grating gate devices. Light colored boxes representing gate metals and dashed lines representing Graphene layers are added for the clarity                                                                                            |

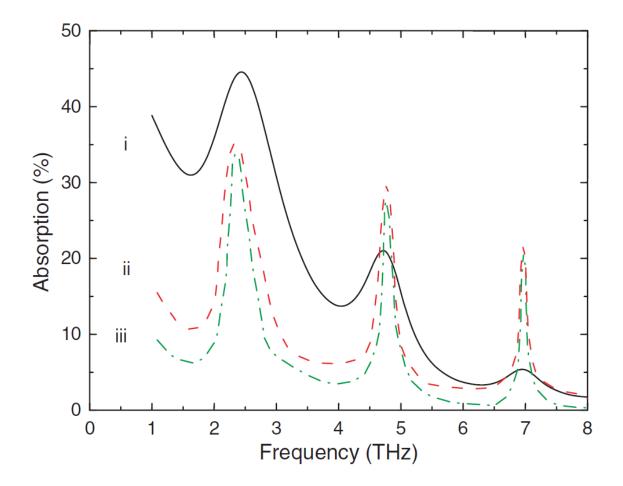

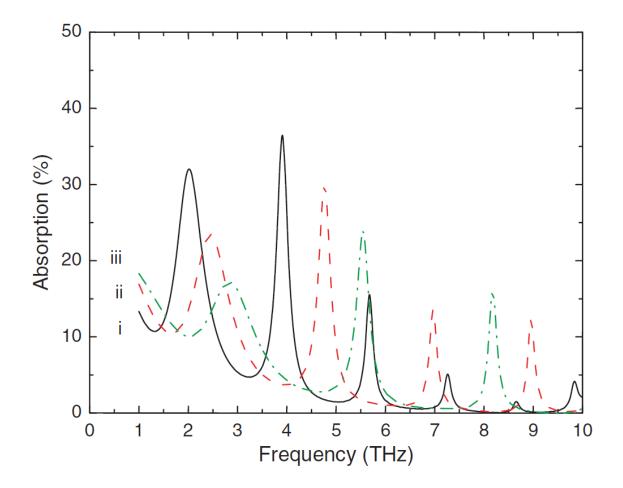

| 57. Absorption spectra of Graphene with different mobilities. L = 1.5 $\mu$ m, w = 0.15 $\mu$ m, N <sub>S</sub> = 7.5×1012 cm <sup>-2</sup> . (i) $\mu$ = 3000 cm <sup>2</sup> /V · s (ii) $\mu$ = 15000 cm <sup>2</sup> /V · s (iii) $\mu$ = 40000 cm <sup>2</sup> /V · s                                                                                |

| 58. Absorption spectra of Graphene grating gate FET structure with different carrier concentrations. L = 1.5 $\mu$ m, w = 0.15 $\mu$ m, $\mu$ =15000 cm <sup>2</sup> /V · s (i) N <sub>s</sub> = 3.6 × 10 <sup>12</sup> cm <sup>-2</sup> (ii) N <sub>s</sub> = 8.3 × 10 <sup>12</sup> cm <sup>-2</sup> (iii) Ns= 1.5×10 <sup>13</sup> cm <sup>-2</sup> 90 |

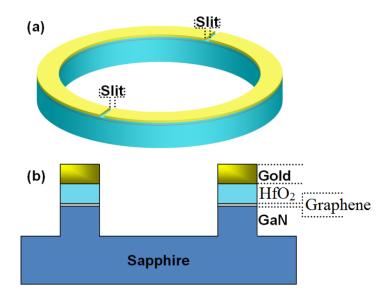

| 59. (a) Split ring resonator placed on top of Graphene. (b) The cross section of the resonator device                                                                                                                                                                                                                                                     |

| 60. (a) Calculated electric field intensity of the fundamental mode in between the circular grating and 2DEG, (b) second mode, (c) summation of modes from 1 to 593                                                                                                                                                                                       |

CHAPTER I

INTRODUCTION

#### **1.1 Graphene Material Overview**

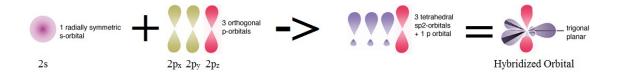

Graphene, a novel electro-optic material consisting of one or a few atomic layers of carbon sheets is considered to be the first truly 2D crystal ever observed in nature and is very promising for high performance micro/nanoelectronics [1]. Carbon, the elementary constituent of Graphene, is the 6th element of periodic table consisting of 6 protons, 6 to 8 neutrons, and 6 electrons. The electronic configuration of carbon is  $1s^22s^22p^2$ ; 2 electrons in 1s atomic orbital (full), 2 electrons in 2s atomic orbital (full), 1 electron in  $2p_x$  atomic orbital (not full), 1 electron in  $2p_y$  atomic orbital (not full) and 0 electron in  $2p_z$  atomic orbital (empty) [2]. In Graphene, the orbitals 2s,  $2p_x$  and  $2p_y$  make a sp2 hybridization while the remaining  $p_z$  is perpendicular to the x-y plane as shown in Figure 1, and thus it forms a honeycomb lattice.

#### Figure 1: SP2 hybridization in Graphene

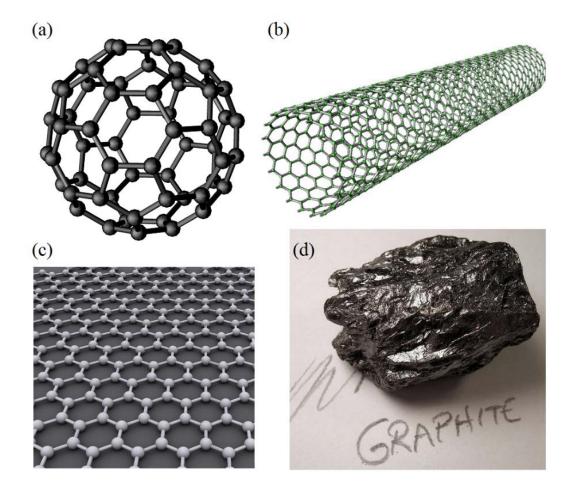

Fullerine, carbon nanotube, Graphene, and graphite are respectively 0D, 1D, 2D and 3D allotropes of carbon as shown in Figure 2 [3]. Fullerines are molecules consisting of wrapped Graphene by the introduction of pentagons on the hexagonal lattice, carbon nanotubes can be viewed as rolled-up cylinders of Graphene, while graphite can be viewed as a stack of Graphene layers sticking together due to van der Waals interaction. As we

already know, three out of four valence electrons of carbon in Graphene form covalent bond with the neighbor atoms and their wave function can be expressed as follows [4]:

$$\frac{1}{\sqrt{3}} \Big( \psi_e(2s) + \sqrt{2} \psi_e(\tau_i 2p) \Big), (i = 1, 2, 3)$$

(1)

Here,  $\psi_e(2s)$  is the 2s wave function and  $\psi_e(\tau_i 2p)$  are the 2p wave function. The forth electron is in the 2p<sub>z</sub> state. As three of the valence electrons form the coplanar bonds, they do not participate in electric conduction and thus has one conduction electron in 2p<sub>z</sub> state.

Figure 2: (a) Fullerine, (b) Carbon Nanotube, (c) Graphene, and (d) Graphite [3]

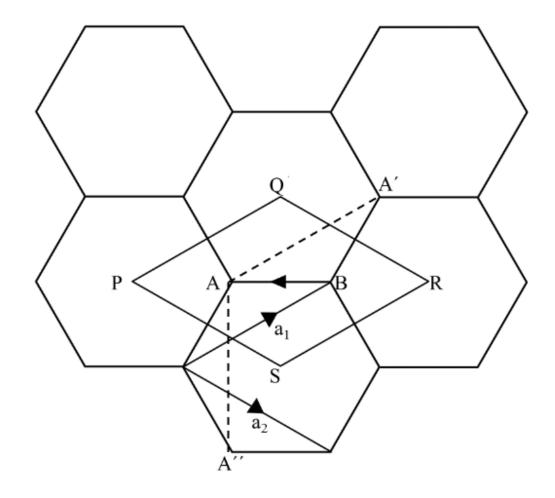

The unit cell of the hexagonal layer, *PQRS* as shown in Figure 3 contains two carbon atoms A and B. The distance *AB* is the lattice constant *a*=1.42 A°. The fundamental lattice displacements of Graphene are a1=AA' and a2=AA'' and theirs magnitude is a1=a2= $\sqrt{3} \times 1.42$  A°=2.46 A°. The reciprocal lattice vectors are  $8\pi/3a$  and are in the directions of *AB* and *AS*, respectively.

Figure 3: Honeycomb lattice structure of Graphene, made out of two interpenetrating triangular lattice.

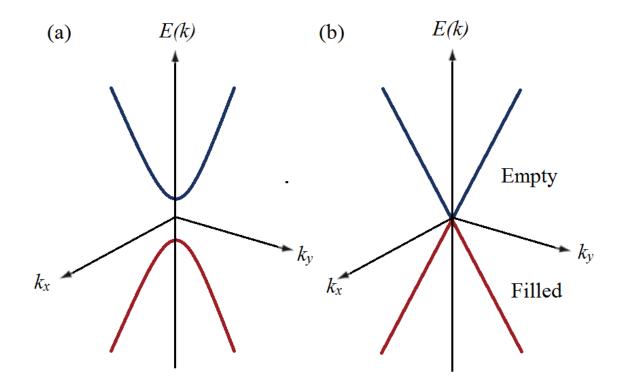

Graphene has an unusual band structure with a zero bandgap. The energy momentum

relation of a conventional semiconductor material can be expressed as [5]:

$$E^2 = m^2 c^4 + p^2 c^2$$

(2)

where E= total energy, m= rest mass, c= velocity of light, p= momentum.

Figure 4: Energy-Momentum relation of (a) conventional semiconductor (b) Graphene

This equation represents a parabolic relationship which is true for ordinary semiconductors as shown in Figure 4 (a). For Graphene, this relationship is linear as in Figure 4 (b) and it can be expressed by the above equation if and only if we consider m=0. When an object moves with velocity (v), it has kinetic energy. Electrons in ordinary systems obey Newton's equation where energy increases quadratically in relation to velocity ( $E \sim v^2$ ). But in Graphene, electrons' energy increases linearly with velocity ( $E \sim v$ ). That is the reason electrons in Graphene behave as if they are relativistic, massless particles that obey Diract's equation and have high fermi velocity, 1/300 times the velocity of light [6].

Single layer Graphene and few layer Graphene can be synthesized by several methods and can be broadly classified into exfoliation, chemical vapor deposition (CVD), arc discharge, and reduction of Graphene oxide [7]. Exfoliation can be divided into two sub-categories: mechanical exfoliation and chemical exfoliation. Stacking of Graphene sheets in graphite is due to the overlap of partially filled  $p_z$  orbital which is perpendicular to the plane. Exfoliation of Graphene from graphite is the reverse process of stacking where work is done against the weak van der Waals force between Graphene layers with large lattice spacing. It has been possible to peel off one or a few sheets of Graphene using scotch tape and deposition on SiO<sub>2</sub>/Si substrate. Mechanical exfoliation produces highest quality Graphene though it's limited due to low productivity. In case of chemical exfoliation, the first step is to increase the interlayer spacing by intercalating Graphene to prepare Graphene intercalated compounds (GICs) which are then exfoliated into Graphene in the second step by heating or sonication [7]. The most promising and inexpensive process for deposition of reasonably high quality Graphene is CVD on transition metal substrate. A RF plasma-enhanced CVD system is widely used to synthesize Graphene on various transition metal substrates by decomposing hydrocarbons such as methane, ethylene, acetylene, and benzene. The layer number of Graphene depends on the hydrocarbon and reaction parameters. Synthesis of Graphene by arc evaporation of graphite in presence of H<sub>2</sub> has also been possible and reported. In this process, two or three layers of Graphene with flake size of 100-200 nm can be prepared. Chemical reduction of graphite oxide is another established procedure in which large quantity of Graphene can be prepared. Graphite oxide when ultrasonicated in water forms a homogeneous colloidal dispersion of predominantly sheet Graphene oxide (SGO) in water. Reduced Graphene oxide (RGO)

with properties similar to that of Graphene is prepared through chemical, thermal, or electrochemical reduction pathways [7].

#### **1.2 Prospect of Graphene as an Electronic Material**

Graphene is considered to be a very promising novel material for high performance nanoelectronics, due to its high carrier mobility, concentration, and stability [8, 9]. It is a prime candidate for many electrical and optical applications due to its extremely high thermal conductivity, long phonon mean free path, and as a 2D material, it could also enable extreme device scaling [10, 11]. With its large band structure velocity ( $1 \times 10^8$  cm/s), large saturation velocity ( $4 \times 10^7$  cm/s), and low 1/f noise characteristics [12, 13, 14, and 15], Graphene is particularly attractive for high frequency electronics. Significant progress has been made on Graphene analog devices capable of good high frequency performance in the region of radio frequency (RF) and Terahertz (THz) frequency.

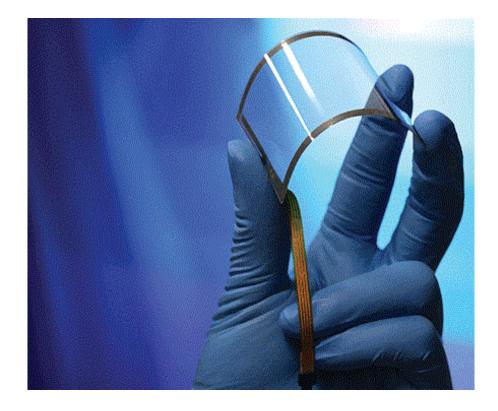

Numerous groups have reported Graphene based analog devices with amplification and phase detection capability [16, 17] as well as plasmonic THz detection capability [18]. Moreover, because of strong ambipolar effect and lack of bandgap [9], Graphene is believed to be more suitable for analog applications than for digital electronics. The physical thinness of Graphene shows prospect of two dimensional high-speed electronics. In addition to its outstanding electrical and thermal properties, its high optical transparency (97.7%) and mechanical elasticity open windows for high-speed transparent and flexible electronics.

Figure 5: Graphene based transparent and flexible electronics [19]

Numerous groups have reported many fascinating and outstanding high frequency characteristics of Graphene field effect transistors. For example, Lin et al. reported a GFET with a gate length of 144 nm and a current gain cut-off frequency,  $f_T$  of 350 GHz [1].

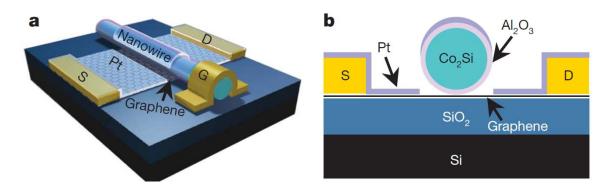

Figure 6: Graphene nanowire gate GFET

Duan et al. reported a nanowire gate GFET as shown in Figure 6 of 144 nm long gate with a  $f_T$  of 300 GHz [20]. Similarly, Avouris et al. and Farmer et al. reported GFET with gate length of 40 nm and 240 nm with a  $f_T$  of 100 GHz and 155 GHz, respectively [8, 21].

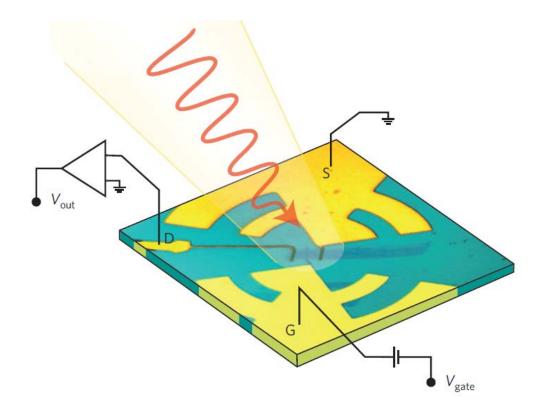

In addition to Graphene based RF FETs, numerous groups have also worked and reported on Graphene based plasmonic THz detectors that operates in room temperature. For example, Knap et al. reported GFETs based on single layer and bilayer Graphene as shown in Figure 7, with acceptable responsivity and photoresponse in room temperature [89].

Figure 7: Schematic of THz plamsonic detectors based on Graphene

## 1.3 Effect of Zero Bandgap Graphene as Channel Material

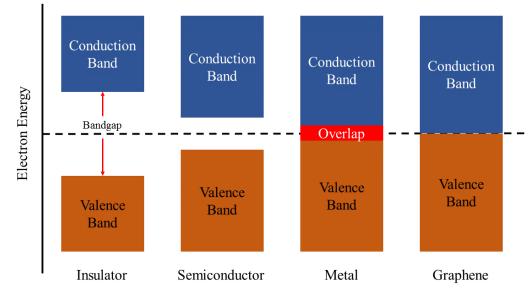

The electronic bandgap of a solid material is the energy gap between the bottom of the conduction band and the top of the valence band. Electrons from the valence band can jump the gap to the conduction band to participate in electric conduction by means of thermal or optical excitation [22]. The band structure of different types of materials including Graphene is shown in Figure 8.

The insulators have a large bandgap that the electrons in valence band cannot gain enough energy to jump up to conduction band, as a result, insulators are bad conductors. On the other hand, metals valence and conduction bands overlap and the electrons in valence band can go to conduction band without any excitation, that's why metals are good conductors.

Energy Bandgap in Materials

Figure 8: Band structure of insulators, semiconductors, metals and Graphene

The existence of a small bandgap allows semiconductor devices to partially conduct as the word "semiconductor" implies. It is the bandgap that gives semiconductors the ability to switch currents on and off as, in order to achieve a desired electrical function. Unlike metals, the band structure of Graphene exhibits two bands intersecting at the k and k' points in the Brillouin zone—Dirac point, and at this point, valence and conduction band are degenerate, which results in Graphene to be a zero bandgap semi-metal material. As it has a zero bandgap, Graphene transistors can never be turned off, which precludes it use in digital and logic application, as well as in pseudospintronics, and infrared nanophotonics [23].

CHAPTER II

# GRAPHENE FET WITH IMPROVED CONTACT RESISTANCE

#### **2.1 Introduction:**

The advantages of Graphene as a channel material of FETs include but not limited to its perfect 2D confinement of carriers, high residual carrier concentration, high carrier mobility, mechanical flexibility, and extremely high thermal conductivity. The access resistance of GFETs adversely affect the current gain cut-off frequency,  $f_T$  by reducing the transconductance and drain current and specially becomes very crucial in downscaled GFETs with shorter gate length. It is therefore desired to minimize GFET access resistance. In conventional silicon based RF transistors, the resistance of access regions is reduced by doping through ion implantation [24]. However, In GFETs, the access regions consist of just a monolayer ungated Graphene with a high sheet resistance, compared to that of heavily doped Si MOSFETs. As a result, the access resistance of GFETs is comparable to the resistance of gated Graphene channel and the 2D structure of Graphene negates the use of ion implantation to dope [25]. The typical value of access resistance of a Silicon MOSFET is at the order of ~150  $\Omega$ -µm [26]. On the other hand, the typical access resistance value of a Graphene FET is ~350  $\Omega$ -µm and 80% of the total device resistance [27]. To utilize the complete advantage of Graphene as a channel material, the set of limitations on the high-frequency performance of GFETs arisen from the access resistances must be eliminated.

It is well known that the source/drain resistances comprising of contact resistance and access resistance impose important set of limitations on the high frequency performance of sub-micrometer FETs by reducing the external transconductance leading to a lower drain current and their minification ensures improved RF performance. These resistances delay

the transition of carriers through the device and in terms of delay time, reduction of transit delay time caused by channel resistance and parasitic delay time caused by source/drain resistance ensure high cut-off frequency that can be achieved through shorter gate length and smaller access regions, respectively. Here are some attempts of transit time reduction to improve RF performance: 550 nm and 240 nm long top gated GFET with epitaxially formed Graphene on the Si face of a semi-insulating high purity SiC wafer and 10 nm HFO<sub>2</sub> as gate dielectric demonstrated cutoff frequency of 53 GHz and 100 GHz respectively [8]. GFET with epitaxial Graphene on Si-face of 4H-SiC having gate lengths between 2  $\mu$ m to 0.5  $\mu$ m demonstrated current gain cut-off frequency  $f_T$  of 4.1 GHz for 2.0  $\mu$ m long gate GFET whereas the 0.5  $\mu$ m long gate GFET showed an exceptional high power gain cut-off frequency of 16 GHz [28]. GFETs having CVD Graphene transferred from copper to diamond-like carbon (DLC) as substrate with 500nm, 140nm and 40nm long gates demonstrated cut-off frequencies of 26GHz, 70GHz and 155GHz respectively [21].

Self-aligned process is used to reduce access region length that can effectively reduce parasitic delay time and increase  $f_T$ . Self-aligned fabrication of T-gate CVD Graphene FET with gate length of 110nm and 170nm with shorter ungated Graphene sections of about 20-40nm were reported showing  $f_T$  of 15 GHz and 23 GHz respectively [29]. GFETs with selfaligned nanowire gate having gate length of 210 nm, 182 nm and 144 nm demonstrated  $f_T$ of 125 GHz, 168 GHz and 300 GHz respectively [20]. However self-aligned process makes fabrication more complex with smaller tolerances.

Reduction of access resistance for enhanced RF performance in III-N high electron mobility transistors (HEMT) [30] and in Graphene FETs (GFET) have been reported [31,

32]. Here, rather than reducing the access resistance by minimizing ungated region length or doping, we propose, extensively analyze, fabricate/integrate, and characterize a novel device structure with controllable access resistance having a total of 5 contacts including source, drain, gate, and 2 field controlling electrodes (FCEs). The FCEs are capacitively coupled to the access regions of the device. The proposed device shows a higher cut-off frequency due to minimization of parasitic resistance. In addition to that, the capacitive coupling technique of the additional contacts ensures mitigation from additional power consumption.

#### 2.2 Theory

## 2.2.1 Current Gain and Current Gain Cut-off Frequency

An important metric for RF transistor's performance measurement is its current gain cutoff frequency,  $f_T$ . Current gain is the ratio of current at the output terminal to that in the input terminal [33]. In common emitter configuration, the input terminal of a FET is the gate and the output terminal is drain.

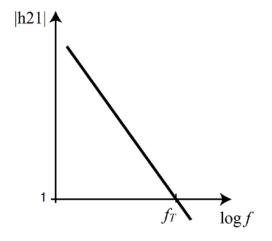

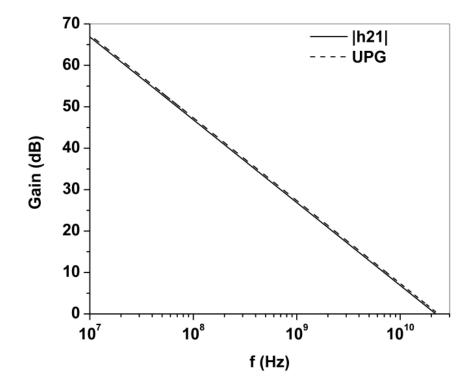

Figure 9: Relation between current gain, |h21| and frequency

As it is a FET, the input current in DC is zero. As a result, the current gain for DC is theoretically infinite,  $h21 = i_{out}/i_{in} = i_{out}/0 = infinite$ . The reactance of gate to channel capacitance is inversely dependent on frequency and with increasing frequency, the reactance decreases. As a result, the input AC current also increases with frequency which results in a decrement of current gain. The frequency at which, current gain drops to unity is called current gain cut-off frequency. A typical relation of current gain, |h21| and frequency is shown in Figure 9.

## 2.2.2 Small Signal Circuit Analysis of Regular Graphene FET

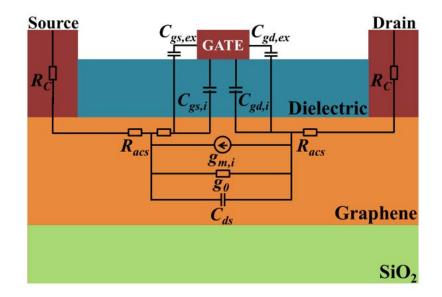

The schematic of a conventional 3-terminal GFET on  $SiO_2$  with the small-signal equivalent circuit laid on top is shown in Figure 10.

# Figure 10: Schematic of a conventional 3-terminal GFET on SiO<sub>2</sub> with the small-signal equivalent circuit laid on top.

The gate to channel capacitance is actually a distributed capacitance and is usually simplified as two capacitors: gate to source capacitance,  $C_{gs}$  and gate to drain capacitance,

$C_{gd}$ , such that

$$C_g = C_{gs} + C_{gd} \tag{3}$$

The gate to source capacitance and gate to drain capacitance are composed of both internal and external parts which can be expressed as

$$C_{gd} = C_{gd,i} + C_{gd,ex}$$

$$C_{gs} = C_{gs,i} + C_{gs,ex}$$

(4)

Where  $C_{gd,i}$  and  $C_{gd,ex}$  are the intrinsic and extrinsic part of gate to drain capacitance, whereas,  $C_{gs,i}$  and  $C_{gs,ex}$  are the intrinsic and extrinsic part of gate to source capacitance. The intrinsic capacitances,  $C_{gd,i}$  and  $C_{gs,i}$  are parallel plate capacitances which are dependent on gate length. On the other hand, the extrinsic capacitances  $C_{gd,ex}$  and  $C_{gs,ex}$  are in fact fringe capacitances and independent on gate length [34].

The small-signal gate-source and gate-drain capacitance can be calculated as:

$$C_{gs} = \frac{\delta Q_{CH}}{\delta V_{GS}}$$

,  $V_{DS}$  is constant (5)

$$C_{gd} = \frac{\delta Q_{CH}}{\delta V_{DS}}, V_{GS} \text{ is constant}$$

(6)

Here,  $Q_{CH}$  is the total charge in Graphene channel,  $V_{GS}$  is gate to source voltage and  $V_{GD}$  is the gate to drain voltage. The total channel charge  $Q_{CH}$  can be expressed as:

$$Q_{CH} \approx \frac{WC_{OX}}{E_{AV}} V_{DS} \left( V_{eff} - \frac{V_{DS}}{2} \right)$$

(7)

Here, W is the device width,  $C_{OX}$  is the gate oxide capacitance,  $E_{AV}$  is the average electric field, and  $V_{eff}$  is effective gate-source overdrive voltage. If we replace  $E_{AV} \approx \frac{V_{DS}}{L}$  in the above equation, the simplified expression for  $Q_{CH}$  turns out to be:

$$Q_{CH} = C_{OX} WL(V_{eff} - \frac{V_{DS}}{2})$$

(8)

Now, the small signal gate to drain and gate to source capacitance can be calculated as:

$$C_{gs} = C_{ox}WL$$

$$C_{gd} = \frac{C_{ox}WL}{2}$$

(9)

If  $g_{m,i}$  is the intrinsic transconductance, the extrinsic delay of the device  $\tau_{ext}$  can be expressed as [35]

$$\tau_{ext} = \frac{C_{gs,ex} + C_{gd,ex}}{g_{m,i}} \tag{10}$$

The intrinsic capacitances  $C_{gd,i}$  and  $C_{gs,i}$  are dependent on gate length and directly scale with that. The intrinsic delay time  $\tau_{int}$  can be expressed as

$$\tau_{int} = \frac{C_{gs,i} + C_{gd,i}}{g_{m,i}} \tag{11}$$

The parasitic time delay due to parasitic resistances and capacitances can be expressed as [34]

$$\tau_{par} = C_{gd} (R_S + R_D) [1 + (1 + C_{gs} / C_{gd}) g_0 / g_m]$$

(12)

where  $g_0 = 1/R_{SD}$  is the output conductance and  $R_S$  and  $R_D$  are the source and drain resistance representing the ohmic contact resistance,  $R_C$  and source/drain access resistance,  $R_{acs}$  in series:

$$R_{D} = R_{S} = R_{C} + (L_{acs} / \mu q n_{0} W)$$

(13)

here  $L_{acs}$  is the access region length ( $L_{gs}$  and  $L_{gd}$ ),  $\mu$  is the carrier mobility, q is electronic charge,  $n_0$  is the residual carrier density in Graphene and W is the device width. The current gain cut-off frequency  $f_T$  is inversely proportional to the total delay time in the device and can be expressed as

$$1/2\pi f_T = \tau_{\rm int} + \tau_{ext} + \tau_{par} \tag{14}$$

Thus according to [35], through summing up all the delay times and rearranging, the  $f_T$  of the device can be related to the small signal circuit parameters as follows:

$$f_T = \frac{g_m / (2\pi)}{[C_{gs} + C_{gd}] \cdot [1 + (R_s + R_D) / R_{SD}] + C_{gd} \cdot g_m \cdot (R_s + R_D)}$$

(15)

where  $R_{SD}$  is the channel resistance that can be expressed as follows [29]:

$$R_{SD} = L_G / \mu q (n_0^2 + n_g^2)^{1/2} W$$

(16)

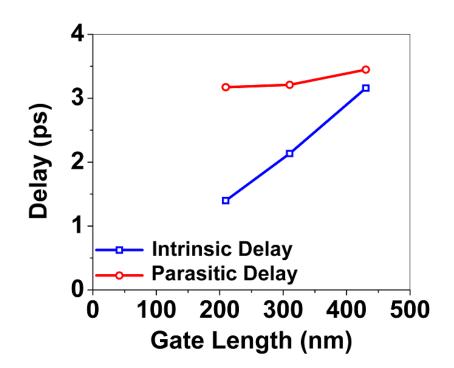

where  $n_g$  is the carrier density due to gate modulation. One needs to minimize the delay times to increase the current gain cut-off frequency,  $f_T$  as well as maximum oscillation frequency,  $f_{MAX}$ , which is proportional to  $f_T$ . From Figure 11, it is visible that for short channel devices, the effect of parasitic time delay,  $\tau_{par}$  becomes more prominent compared to that of long channel devices. So, for short channel devices with good high frequency performance, its minimization becomes indispensable [36].

Figure. 11: Intrinsic and parasitic time delays vs. gate length of In<sub>0.7</sub>Ga<sub>0.3</sub>As-channel HEMTs reproduced from [36].

## 2.2.3 Small Signal Circuit Analysis of Top FCE GFET

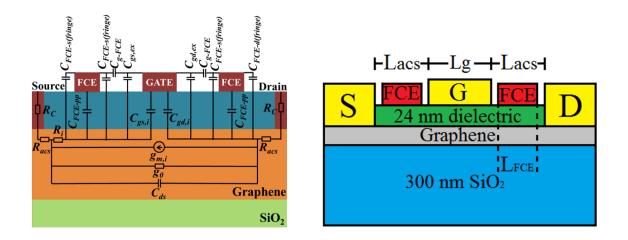

To reduce the GFET access resistance, here we propose a novel device structure consisting of two capacitively coupled FCEs, placed on top of the device, at the ungated access regions as shown in Figure 12 (b). As the transistor action of the device takes place at the gate terminal, the additional DC bias at the FCEs will help supporting the total device current in either of the transportation regimes (electron/hole) by selective population of particular type of carriers at the access regions.

Figure 12: (a) Small signal equivalent circuit overlaid on top of top FCE GFET (b) Schematic of the proposed top FCE GFET (not in scale).

The proposed FCEs independently biased with a DC voltage reduce the source/drain access resistance, as well as, introduce some additional parasitic capacitance. A small signal equivalent circuit overlaid on top of the proposed GFET with two FCEs placed on top of the access regions is shown in Figure 12 (a). The FCEs make a parallel plate capacitance,  $C_{FCE-pp}$  and two fringe capacitances,  $C_{FCE(fringe)}$  with the Graphene channel. As all three of the capacitances are parallel to each other, the total FCE capacitance,  $C_{FCE}$  can be expressed as:

$$C_{FCE} = C_{FCE(pp)} + 2C_{FCE(fringe)}$$

=  $\varepsilon_0 \varepsilon_r \frac{WL_{FCE}}{t_{ox}} + 2C_{FCE(fringe)}$  (17)

Here,  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_r$  is the relative permittivity of air, *W* is the device width,  $L_{FCE}$  is the FCE length, and  $t_{ox}$  is the gate oxide thickness. The gate terminal makes two parallel plate capacitance with FCE on each side and can be expressed as:

$$C_{g-FCE} = \mathcal{E}_0 \mathcal{E}_r \frac{Wt}{L_{g-FCE}}$$

(18)

The total gate to source capacitance,  $C_{gs(total)}$  and  $C_{gd(total)}$  after adding FCEs turn out to be

$$C_{gs(total)} = C_{gs} + \frac{C_{FCE} \times C_{g-FCE}}{C_{FCE} + C_{g-FCE}}$$

$$C_{gd(total)} = C_{gd} + \frac{C_{FCE} \times C_{g-FCE}}{C_{FCE} + C_{g-FCE}}$$

(19)

If an FCE of length  $L_{FCE}$  is placed at the access region of length  $L_{acs}$ , then the new expression for  $R_S$  and  $R_D$  becomes

$$R_{D} = R_{S} = R_{C} + \frac{\left(L_{acs} - L_{FCE}\right)}{W\mu e n_{0}} + \frac{L_{FCE}}{W\mu e \left(n_{0}^{2} + n_{FCE}^{2}\right)^{1/2}}$$

(20)

The induced carriers  $n_{FCE}$  caused by FCE modulation effectively reduces the resistance of the ungated access regions and thus results in a decrement of  $\tau_{par}$  and increment of  $f_T$ .

### 2.2.4 Small Signal Circuit Analysis of Bottom FCE GFET

In this part of this report, we study the theory of the proposed device consisting of two independently biased capacitively coupled contacts placed at the access regions on bottom of the GFET as shown in Figure 13. As like as the top FCE GFET, the FCEs on the bottom of the device are independently biased and capacitively coupled to the channel.

Figure 13: Schematic of the proposed GFET with 2 bottom FCEs at the ungated region

The independently biased FCEs induce additional carriers at the access region according to eqn. 16 As proposed, an FCE of length  $L_{FCE}$  placed at the access region of length Lacs making two no-FCE regions on both sides each having a length of  $L_{no_{-}FCE}$  changes the expression of  $R_S$  and  $R_D$  as follows-

$$R_{S} = R_{D} = 2R_{C} + \frac{4L_{no\_FCE}}{\mu e n_{0}W} + \frac{2L_{FCE}}{\mu e (n_{0}^{2} + n_{FCE}^{2})^{1/2}W}$$

(21)

The resistance of the ungated access regions decreases by the induced carriers  $n_{FCE}$  due to FCE modulation which results in a decrement of  $\tau_{par}$  and increment of  $f_T$ . In this device, the key advantage is the ease of fabrication with high tolerance, because the FCEs are to

be patterned on a different layer other than the gate layer. In addition to that, the larger distance between FCEs and gate will result in lower parasitic capacitances.

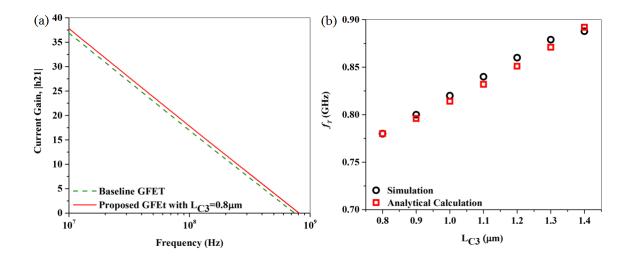

### 2.2.5 Small Signal Circuit Analysis of Hybrid Contact GFET

In this part, we have proposed, studied, and extensively analyze a GFET with hybrid contacts capable to reduce the access resistance and contact resistance of the device, simultaneously.

The hybrid contact consists of a ohmic contact having capacitive extension towards the Gate. The capacitively coupled part of the contact reduces the contact resistance and provides a low resistance path for the high frequency signal. In addition, the extension towards Gate reduces the access region length and the associated resistance—the access resistance. Small signal equivalent circuit of the proposed hybrid contact GFET overlaid on the device schematic is shown in Figure 14.

$$Z_{C} = \frac{R_{C}^{2}R_{C3} + R_{C3}^{2}R_{C} + X_{C3}^{2}R_{C}}{(R_{C} + R_{C3})^{2} + X_{C3}^{2}} - j\frac{X_{C3}R_{C}^{2}}{(R_{C} + R_{C3})^{2} + X_{C3}^{2}} = R_{C}' - jX_{C}'$$

(22)

Assuming the length of C3 is  $L_{C3}$ , the access region length of the hybrid contact GFET comes to be  $L'_{A} = L_{A} - L_{C3}$  and the new expression for Source/Drain impedance and total channel impedance become as follows:

$$Z_{D} = Z_{S} = Z_{C} + R'_{A} = R'_{C} - jX'_{C} + (L'_{A} / \mu q n_{0} W)$$

$$Z_{SD} = 2Z_{D} + R_{CH} = R_{SD} - jX_{SD}$$

(23)

From the equation above, we can see that the total channel resistance has real part as well as an imaginary part. A simple matching network can be designed for matching and eliminating the imaginary part of the input impedance. An impedance matching network is an additional circuit that consists of a reactive element of such a value that can effectively nullify the opposite signed reactive element of the device and thus eliminate the effective reactance of the whole system. It can be achieved with only 2 reactive elements that transform both the real and imaginary part. A common 2 reactive element configuration is referred to as L-section matching network as shown in Figure 3(a).

Figure 15. (a) Matching Network-1 (b) Matching Network-2.

Considering network-1, we can quantify the input impedance as:

$$Z_{in} = jX_{L} + \frac{R_{SD} + jX_{SD}}{1 + jX_{C}R_{SD} - X_{C}X_{SD}}$$

(24)

To match it with a resistance R, we consider  $Z_{in}=R$  and after equating the real and imaginary parts, we get:

$$X_{L} = \frac{1}{X_{CAP}} + \frac{X_{SD}R}{R_{SD}} - \frac{R}{X_{CAP}R_{SD}}$$

$$X_{CAP} = \frac{X_{SD} \pm \sqrt{\frac{R_{SD}}{R}} \sqrt{R_{SD}^{2} + X_{SD}^{2} - RR_{SD}}}{R_{SD}^{2} + X_{SD}^{2}}$$

(25)

By solving these equations, we can determine the capacitor and inductor values required to nullify imaginary part of contact impedance. These two relations are derived for network-1 and are valid if  $R_{SD}$ >R. On the other hand, if  $R_{SD}$ <R, network-2 as shown in Figure 3(b) needs to be used and after following the same procedure, we can estimate  $X_L$ and  $X_{CAP}$  as follows:

$$X_{L} = \pm \sqrt{R_{SOURCE-DRAIN} (R - R_{SOURCE-DRAIN}) - X_{L}}$$

$$X_{CAP} = \pm \frac{\sqrt{(R - R_{SOURCE-DRAIN})} / R_{SOURCE-DRAIN}}{R}$$

(26)

For devices working on a wide frequency range, a very common technique in RF/mobile communication named "frequency transformation technique" needs to be used, as reported in [37].

Once the matching network has been used, only the real part of contact resistance  $R'_c$  remains and the new expression of source/drain resistance comes out to be:

$$R_{D} = R_{S} = R_{C}' + (L_{A}' / \mu q n_{0} W)$$

<sup>(27)</sup>

One can easily get the relation between  $f_T$  and  $Z_C$  by plugging this new  $R_S$  and  $R_D$  into the  $f_T$  equation in (5).

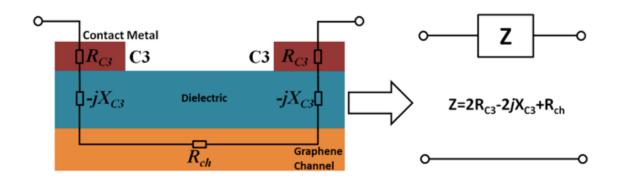

The C3 can be considered as a RC transmission line and its impedance can be analytically calculated [38]. If a C3 is placed on top of Gate dielectric, the contact metal and Graphene channel with in-between dielectric material form a RC transmission line. The propagation constant  $\gamma$  and characteristics impedance  $Z_0$  of this transmission line can be estimated by the following equations:

$$\gamma = \sqrt{i2\pi R_{sh}C}, Z_0 = \frac{1}{W}\sqrt{\frac{R_{sh}}{i2\pi fC}}$$

(28)

where,  $R_{sh}$  is sheet resistance of Graphene channel, *C* is the metal to Graphene capacitance per unit area, *W* is the width and *f* is the frequency. The C3 impedance can be estimated equal to the input impedance of this open ended transmission line as follows:

$$Z_{in} = Z_0 \operatorname{coth}\left(\gamma L_{C3}\right) \tag{29}$$

Figure 16. Schematic of a RF TLM structure on Graphene with small-signal equivalent circuit overlaid on top and the equivalent 2-port network

In simulation, the impedance of C3s can be calculated by using RF Transmission Line Method (TLM) structures with multiple C3s with various in-between distances. Two C3s and the Graphene channel in-between is a Two-Port network as shown in Figure 4 and its impedance can be estimated by extracting the 2 port S-Parameters and converting them to B-Parameter [39]. The real and imaginary parts of B-parameter are actually the real and imaginary parts of total impedance of the two port network—two C3 impedance in addition to in-between Graphene channel resistance.

### 2.3 Simulation of GFET with FCEs

### 2.3.1 Simulation of Top FCE GFET

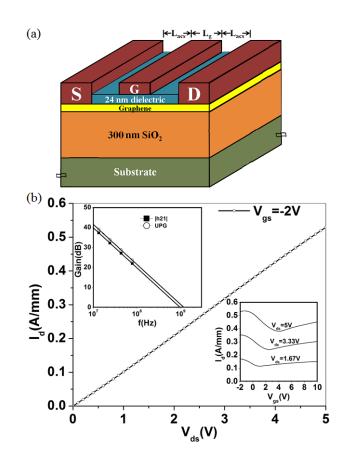

Here we simulate and analytically estimate the performance of the top FCE GFET and compare with the conventional ones. The baseline conventional GFET in this study was chosen similar to the one reported in [10]. We name it as GFET-A. It consists of 3.0 µm long gate and 1.5  $\mu$ m long access region having SiO<sub>2</sub> as substrate and Al<sub>2</sub>O<sub>3</sub> with SiO<sub>2</sub> as gate dielectric as shown in Figure 17 (a). Using the reported characteristics, residual carrier (hole) concentration at the Graphene channel is extracted as 7.02  $\times 10^{12}$  cm<sup>-2</sup> at  $V_{GS}=0$ which results in an access resistance of  $R_{acs}$ =25.2  $\Omega$  for the device width of 100  $\mu$ m. We simulated the DC and RF characteristics of the baseline GFET using physics based numerical device simulation tool with parameters modified for Graphene. This type of simulation approximates the operation and transportation of carriers through the structure by applying a set of differential equations including Poisson's Equation, Carrier Continuity Equations and Drift-Diffusion Equation, derived from Maxwell's laws, onto a 2D grid, consisting of a number of grid points called nodes. This way the electrical performance of a device can be modeled in DC, AC or transient modes of operation [40]. The results presented in Figure 17 (b) are in good agreement with the measured characteristics in [10] which validate our simulation method where the contribution of both the electrons and holes to the drain current is considered. For the baseline GEFT,  $f_T$  and  $f_{MAX}$  are extracted as 1.0 GHz and 1.2 GHz, respectively. Operating regime (electron or hole) of the device can be chosen by biasing the gate on either side of Dirac point to make one type of carriers dominant. The total device current on either regime is still supported by the low density

residual carriers at the ungated access regions causing high source/ drain resistance which adversely affect the RF performance. The simulation decks have been documented in APPENDIX A and APPENDIX B.

Figure 17: (a) Schematic of the baseline GFET-A, (b) DC and RF characteristics (Current Gain, |h<sub>21</sub>| and Unilateral Power Gain, UPG) of the baseline GFET-A from simulation.

In the proposed device, two capacitively coupled FCEs are placed at the ungated access regions as already shown in Figure 12 (b). As the transistor action of the device takes place at the gate terminal, the additional DC bias at the FCEs will help supporting the total device current in either of the transportation regimes by selective population of particular type of carriers at the access regions.

We consider two devices for our analysis: (i) GFET-A; the long channel device with  $L_g$ =3.0 µm,  $L_{acs}$ =1.5 µm,  $\mu_h$ =530 cm<sup>2</sup>/V.s and  $\mu_e$ =336 cm<sup>2</sup>/V.s and (ii) GFET-B; the short channel device with  $L_g$ =0.5 µm,  $L_{acs}$ =1.5 µm,  $\mu_e$ =4900 cm<sup>2</sup>/V.s and  $\mu_h$ =3100 cm<sup>2</sup>/V.s. Analytical calculations using the equations above show that for GFETs with a typical residual carrier (hole) concentration of 4.8×10<sup>12</sup> cm<sup>-2</sup>, the GFET-A, the long channel low mobility device with two 1.3 µm long FCEs each biased at -3 V can lower the  $R_{acs}$  of an initial value of 36.8  $\Omega$  down to 20  $\Omega$ .

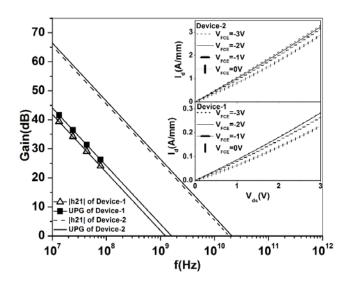

Figure 18: RF characteristics of both GFET-A and GFET-B with  $V_{FCE}$ =-3V and  $V_{gs}$ =-2V. Inset shows the I<sub>d</sub>-V<sub>d</sub> characteristics of GFET-A & B with V<sub>FCE</sub> in hole transportation regime at  $V_{gs}$ =-2V considering concentration dependence of the hole mobility.

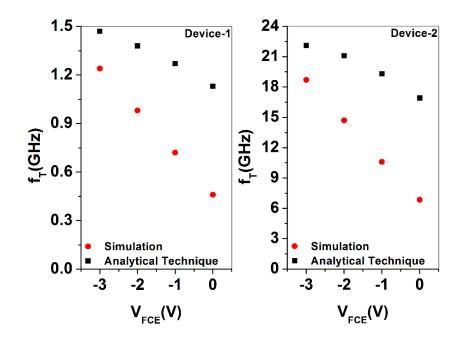

The minimization of  $R_{acs}$  makes the  $f_T$  of Device-1 to be 1.47 GHz whereas the  $f_T$  of this device with  $V_{FCE}=0$  is 1.1 GHz calculated for hole transportation regime. Similar minimization of access resistance due to biased FCE makes the  $f_T$  of GFET-B; the short channel high mobility device to be 22.1 GHz which has a value of 16.9 GHz at  $V_{FCE}=0$  also for hole regime operation.

The numerical device simulation tool was used to simulate the proposed novel GFET with residual carrier (hole) concentration of  $4.8 \times 10^{12}$  cm<sup>-2</sup> same as that used for baseline device simulation and analytical calculations. The RF characteristics at  $V_{gs}$ =-2V (hole regime) and  $V_{FCE}$  = -3V along with the  $I_d$ - $V_{ds}$  characteristics with FCE bias of both GFET-A and GFET-B are shown in Figure 18. The  $I_d$ - $V_{ds}$  characteristic is depicting the decrement of  $R_s$  and  $R_D$  due to the decrement of  $R_{acs}$  by FCE bias.

Figure 19: Improvement of  $f_T$  with  $V_{FCE}$  for both GFET-A and GFET-B in hole regime.

The improvement of RF characteristics with FCE bias estimated using both analytical and numerical techniques for hole regime is shown in Figure 19. It was reported that carrier mobility did not show significant dependence on carrier concentration in the range of concentration we worked [41]. Therefore, the hole mobility for the GFET-A value was kept constant at 530 cm<sup>2</sup>/V.s throughout the entire range of FCE in both analytical and numerical analyses.

Figure 20: Improvement of  $f_T$  with V<sub>FCE</sub> for both GFET-A and GFET-B in electron regime at V<sub>gs</sub>=6.0 V (numerical simulation results).

On the other hand, Graphene hole mobility was considered to be significantly dependent on carrier concentration for the GFET-B, and its values at  $V_{FCE}=0$ , -1, -2, and -3V were estimated using the data in [42] for all analyses. The analytical technique resulted higher cutoff frequency compared to that obtained from numerical simulations because of the limitations to take the additional parasitic capacitances introduced due to the FCE contacts into account.

One can expect similar improvement of  $f_T$  while the GFET is in electron transport regime. Such improvement is estimated using the simulation tool considering similar concentration dependent mobility of electrons for GFET-B and shown in Figure 20.

#### 2.3.2 Simulation of Bottom FCE GFET

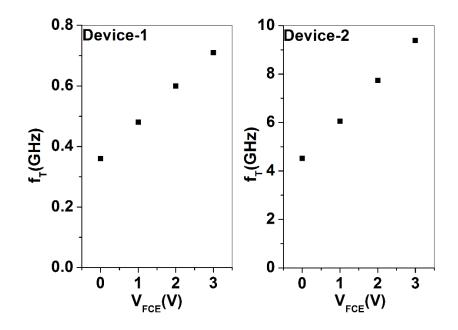

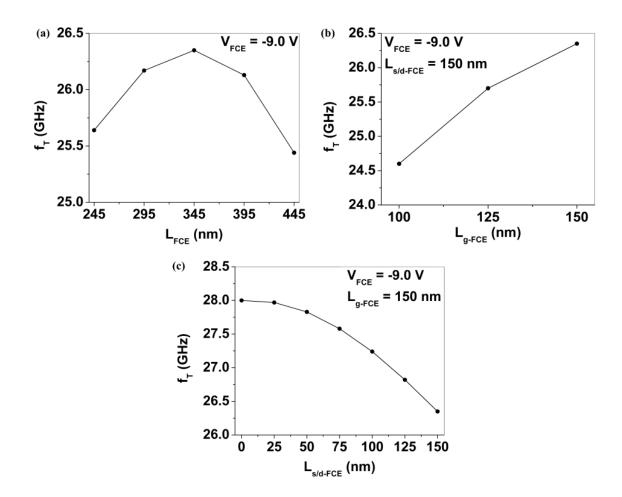

To improve the RF performance we added FCEs at the 1.5  $\mu$ m long ungated regions on bottom of GFET-A as already shown in Figure 13. As we cannot make the gate dielectric so thick that the gate loses good control over the channel, we have a limitation on the gate voltage too not to surpass the gate dielectric breakdown electric field. As the dielectric between FCEs and channel is much thicker compared to the gate dielectric, the FCE voltage was much higher than the gate voltage. To determine the optimum FCE length and position providing maximum  $f_T$  for GFET-A, we placed FCEs of different lengths at the center of the access regions leaving two equal no\_FCE regions both sides and simulated the RF performance at  $V_{FCE}$  -9V which represents an electric field moderately lower than the breakdown electric field of SiO<sub>2</sub> [43]. It was reported that carrier mobility did not show significant dependence on carrier concentration in the range of concentration we consider here [44]. Therefore, the hole and electron mobility was kept constant at 530 cm<sup>2</sup>/V.s and 336 cm<sup>2</sup>/V.s respectively for  $V_{FCE}$  = -9V as well as for rest of the analyses performed on GFET-A throughout the entire range of FCE bias. The dependence of  $f_T$  over  $L_{FCE}$  shown in Figure 21 (a) reveals that two 1.4  $\mu$ m long FCEs at the access regions leaving 50 nm no\_FCE regions on each side is the optimum condition in this case. Keeping the Source/Drain to FCE distance ( $L_{s/d-FCE}$ ) unchanged to 50 nm, we gradually decreased the Gate to FCE distance down to zero (FCE edge aligned to Gate edge) and plotted  $f_T$  against them as shown in Figure 21 (b). The decrement of  $L_{g-FCE}$  showed deterioration of  $f_T$  rather than improvement here. At  $L_{g-FCE} = 50$  nm, we later decreased the  $L_{s/d-FCE}$  from 50 nm down

to zero gradually. This time, the decrement of  $L_{s/d-FCE}$  increased the  $f_T$  as shown in Figure 21 (c).

From Figure 21, the optimum  $L_{FCE}$ ,  $L_{s/d-FCE}$  and  $L_{g-FCE}$  were found 1.45 µm, 0 µm and 50 nm respectively. Using the FCEs with optimum length and position, for hole regime operation of GFET-A ( $V_{gs} = -2.0$  V), the DC simulations showed that the drain current increased with increasing negative FCE bias ( $V_{FCE}$ ) shown in Figure 22, which reveals reduction of access resistance.

Figure 21: At V<sub>FCE</sub> = -9 V (a)  $f_T$  plotted against different L<sub>FCE</sub>. (b) At L<sub>s/d-FCE</sub> =50 nm,  $f_T$  plotted against L<sub>g-FCE</sub>. (c) At L<sub>g-FCE</sub> = 50 nm,  $f_T$  plotted against L<sub>s/d-FCE</sub>.

Analytical calculations based on the equations presented above were used to quantify the reduction and was found that for  $L_{gs}/L_{gd}=1.5 \,\mu m$  with FCEs of optimum size and position, the access resistance  $R_{acc}=36.8 \,\Omega$  of the baseline device went down to 23.0  $\Omega$  at  $V_{FCE} = -9 \,V$ .

Figure 22: Increment of drain current with FCE bias at  $V_{ds}$  = 5.0 V and  $V_{gs}$  = -2.0 V.

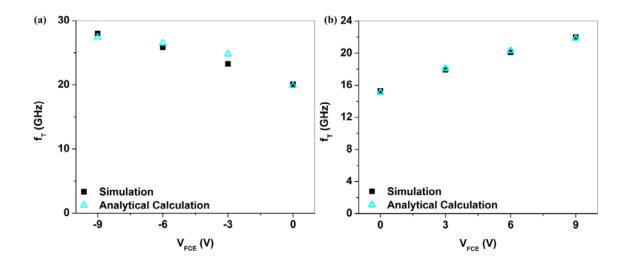

We used analytical and numerical investigation to estimate the RF improvement in both electron and hole regime of operation. Fig. 5 (a) shows the simulated current gain,  $|h_{21}|$  - frequency relationship of the device for the DC biasing conditions of  $V_{gs} = -2 V$ ,  $V_{ds} = 5 V$  which represents hole regime operation of GFET-A and for different FCE biases. The current gain cutoff frequency,  $f_T$  was extracted from the data in Figure 23 (a) and compared to the ones analytically calculated in Figure 23 (b). As the simulation tool estimates the transportation of carriers through the structure by applying differential equations onto the nodes of a 2D grid, it was capable of including the additional capacitances arisen due to the presence of the additional contacts (FCEs) by itself. To include them in the analytical calculation part, we modified the capacitance values of  $C_{gs}$

and  $C_{gd}$  in the RF equations derived for conventional 3-terminal FETs by calculating the FCE capacitances using geometric and material parameters. Considering the device width to be 100 µm, each of  $C_{gs}$  and  $C_{gd}$  valued  $3.90 \times 10^{-13}$  F calculated for conventional 3 terminal GFET and after inclusion of additional capacitances due to FCEs, it became  $4.40 \times 10^{-13}$  F.

Figure 23: (a) Current gain  $|h_{21}|$  - frequency relationship of the GFET-A with FCEs at varying V<sub>FCE</sub> values in hole regime of operation. (b)  $f_T$  vs. V<sub>FCE</sub> where  $f_T$  is calculated using analytical technique and also extracted from (a).

For electron regime of the same device, DC biasing of  $V_{ds} = 5$  V and  $V_{gs} = 6$  V was considered for similar analytical and numerical estimation of the cut off frequency,  $f_T$ . The  $f_T$  of baseline GFET-A in this condition was extracted to be 0.57 GHz. Figure 24 (a) shows the |h21|-frequency relationship of GFET-A with FCEs at different V<sub>FCE</sub> and the extracted  $f_T$  values along with those from analytical technique are plotted against V<sub>FCE</sub> in Figure 24 (b).

We also explored the effect of biased FCEs on RF improvement in short channel high mobility GFETs. The baseline GFET chosen for this analysis is similar to the one reported in [34]. The device has CVD-grown Graphene channel with carrier mobility of  $\mu = 2234$  cm<sup>2</sup>/ V.s on sapphire substrate with L<sub>g</sub> = 210 nm, L<sub>sd</sub> = 1.5  $\mu$ m and named as GFET-B. Considering the device geometry to be symmetrical, access region length is L<sub>gs</sub> = L<sub>gd</sub> = 645 nm.

Figure 24: (a) Current Gain |h21| - Frequency relationship of GFET-A with FCEs at different V<sub>FCE</sub> values in electron regime of operation. (b)  $f_T$  vs. V<sub>FCE</sub> where  $f_T$  is calculated using analytical technique and also extracted from (a).

The simulated RF performance of the baseline device presented in Figure 25 is in good agreement with the reported one after de-embedding.  $f_T$  and  $f_{MAX}$  were extracted as 22.1 GHz and 23.3 GHz, respectively. To improve the RF performance, FCEs are added on bottom of two 645 nm long ungated regions and biased up to ±9.0 V as before not to exceed the breakdown voltage of Al<sub>2</sub>O<sub>3</sub> reported in [45]. Graphene hole and electron mobility was considered to be significantly dependent on carrier concentration and their values at different V<sub>FCE</sub> were estimated using the data in [42] for all analyses.

To determine the optimum FCE length and position for GFET-B, we placed FCEs of different lengths as before and simulated the RF performance. The dependence of  $f_T$  over

$L_{FCE}$ ,  $L_{g-FCE}$  and  $L_{s/d-FCE}$  shown in Figure 26 reveals that the optimum values of  $L_{FCE}$ ,  $L_{s/d-FCE}$  and  $L_{g-FCE}$  are 495 nm, 0 nm and 150 nm respectively.

Figure 25: Current Gain and Unilateral Power Gain vs. frequency of the short channel high mobility baseline GFET.

Using the optimum FCE length and position, we estimated the RF improvement in both electron and hole regime of operation using both simulations and analytical technique. Analytical calculation showed that the access resistance of 645 nm long access region with an initial value of 3.66  $\Omega$  went down to 2.31  $\Omega$  for V<sub>FCE</sub> = -9 V. In frequency domain AC simulations, a biasing condition of V<sub>ds</sub>= -1.6 V, V<sub>gs</sub>= -0.6 V was assumed for hole regime and V<sub>ds</sub> = -1.6 V, V<sub>gs</sub> = 1 V was assumed for electron regime.

Figure 26: At V<sub>FCE</sub> = -9 V (a)  $f_T$  plotted against different L<sub>FCE</sub>. (b) At L<sub>s/d-FCE</sub> =150 nm,  $f_T$  plotted against L<sub>g-FCE</sub>. (c) At L<sub>g-FCE</sub> = 150 nm,  $f_T$  plotted against L<sub>s/d-FCE</sub>.

The extracted  $f_T$  values from the frequency response for hole regime along with those from analytical calculation using modified RF equation for 5-terminal GFET are plotted against  $V_{FCE}$  in Figure 27 (a) whereas that for electron regime in Figure 27 (b).

Figure 27: Extracted  $f_T$  from frequency response and from analytical calculations plotted against V<sub>FCE</sub> for (a) hole regime operation and (b) electron regime operation.

## 2.3.3 Simulation of Hybrid Contact GFET

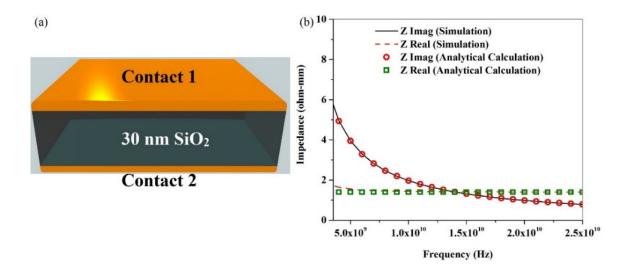

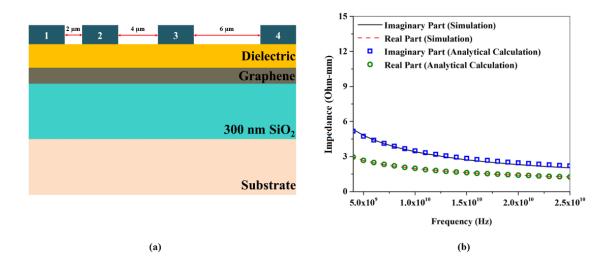

We aim to add two C3s on this device and short them to the ohmic contacts to extensively analyze its effect on the device's high frequency performance. As a starting point of capacitive impedance simulation, we first simulated a simple capacitor-like structure. It consists of 30nm SiO<sub>2</sub> between two metal contacts and each metal contact has a contact resistance of 0.7 ohm-mm, shown in Figure 28 (a).

The real and imaginary parts of this capacitive impedance are estimated using simulation as well as analytical technique. In Figure 28 (b), the real and imaginary part of capacitive impedance estimated from simulation and analytical calculations are plotted with respect to frequency. We can see that the results using both of the methods are in a very good agreement, which validates our simulation technique of estimating capacitive impedance. For further verification, we successfully regenerated the experimental data for III-N RF TLM structures reported in [38]. To estimate the impedance of the capacitance formed between a C3 and Graphene channel with Gate dielectric in-between, we simulated a RF TLM structure on Graphene having two C3s with various in-between distances.

Figure 28: (a) Schematic of the capacitor like structure (b) The real and imaginary part of impedance estimated from simulation and analytical calculation.

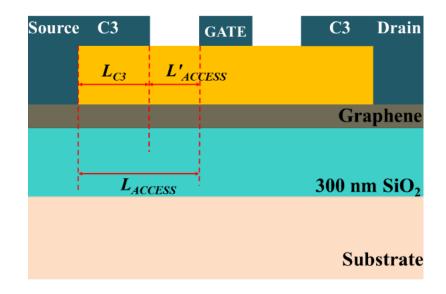

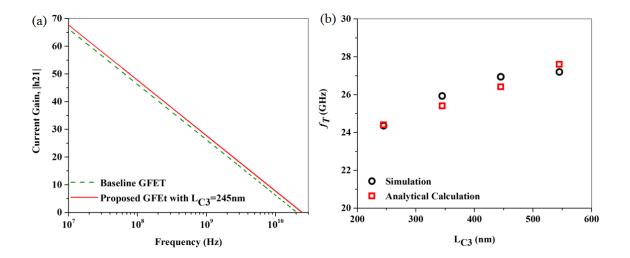

The C3s were placed on exactly the same structure, as in baseline GFET-1, consisting of 9 nm SiO<sub>2</sub> and 15 nm Al<sub>2</sub>O<sub>3</sub> serving as Gate dielectric deposited on CVD Graphene with carrier mobility same as that of baseline GFET-1, shown in Figure 17 (a). The impedance between contact 1 & 2, 2 & 3, and 3 & 4 were calculated at a specific single frequency, plotted with respect to distance, and extrapolated up to zero distance to extract the real and imaginary part of a single C3 impedance at that frequency. This procedure was repeated over the frequency range of 5 GHz to 25 GHz with a step size of 1 GHz. The real and imaginary part of C3 impedance plotted with respect to frequency is shown in Figure 29 (b).

Figure 29: (a) Schematic of RF TLM structure on Graphene. (b) The real and imaginary part of C3 impedance estimated from both simulation and analytical calculations plotted with respect to frequency.