## Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-21-2014

## Real-Time Scheduling of Embedded Applications on Multi-Core Platforms

Ming Fan Florida International University, mfan001@fiu.edu

**DOI:** 10.25148/etd.FI14040815

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the <u>Computer and Systems Architecture Commons</u>, <u>Power and Energy Commons</u>, <u>Systems Architecture Commons</u>, and the <u>Theory and Algorithms Commons</u>

#### Recommended Citation

Fan, Ming, "Real-Time Scheduling of Embedded Applications on Multi-Core Platforms" (2014). FIU Electronic Theses and Dissertations. 1243.

https://digitalcommons.fiu.edu/etd/1243

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

####

A dissertation submitted in partial fulfillment of the requirements for the degree of  ${\color{blue} {\rm DOCTOR~OF~PHILOSOPHY}}$

in

ELECTRICAL ENGINEERING

by

Ming Fan

To: Dean Amir Mirmiran College of Engineering and Computing

This dissertation, written by Ming Fan, and entitled Real-Time Scheduling of Embedded Applications on Multi-Core Platforms, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

| _                                         | Malek Adjouadi                                             |

|-------------------------------------------|------------------------------------------------------------|

|                                           | Jean H. Andrian                                            |

| _                                         | Nezih Pala                                                 |

| _                                         | Deng Pan                                                   |

| _                                         | Gang Quan, Major Professor                                 |

| Date of Defense: March 21, 2014           |                                                            |

| The dissertation of Ming Fan is approved. |                                                            |

|                                           | Dean Amir Mirmiran<br>College of Engineering and Computing |

| _                                         | Dean Lakshmi N. Reddi<br>University Graduate School        |

Florida International University, 2014

© Copyright 2014 by Ming Fan All rights reserved.

#### DEDICATION

I would like to dedicate this Doctoral dissertation to my beloved wife, Rong Rong, and my dearest parents. Without their love, understanding, support, and encouragement, the completion of this endeavor would never have been possible.

#### ACKNOWLEDGMENTS

First, I would like to express my deepest appreciation to my major advisor, Dr. Gang Quan, for his constant guidance and endless encouragement during the last five years of my doctoral study. I truly admire his dedication to science and research.

I would also like to express my gratitude to my Ph.D. committee members, Dr. Jean H. Andrian, Dr. Malek Adjouadi, Dr. Nezih Pala and Dr. Deng Pan, for their helpful insights, comments and suggestions in improving the quality of this dissertation. I am extremely proud to have such a wonderful and knowledgeable people serving on my dissertation committee.

I am thankful to the staff of ECE department at FIU, specially to Mrs. Pat Brammer, Mrs. Maria Benincasa and Mrs. Ana Saenz for their great commitment to student services.

Next, I would like to thank my lab mates, Mr. Shuo Liu, Mr. Qiushi Han, Mr. Tianyi Wang, Mr. Shi Sha, Dr. Vivek Chaturvedi, Dr. Huang Huang and Dr. Guanglei Liu, for creating a wonderfully collaborative work environment.

Further, I want to thank my family for their unlimited love, faith, encouragement, blessings and prayers. I am very grateful to my beloved wife, Mrs. Rong Rong, for accompanying and encouraging me during my entire Ph.D life. I want to give my life-long gratitude to my dearest mother, Mrs. Zhenhuan Dang, and father, Mr. Wei Fan, for all the love and affection they have showered upon their children. I want to thank my sister, Mrs. Xing Fan, for being a great wall of support and inspiration in my life. I am thankful to my mother-in-law, Mrs. Xiaochun Wang, and farther-in-law, Mr. Delun Rong, for their care and encouragement.

Finally, and above all, I would like to thank the National Science Foundation (NSF) for supporting the research described in this dissertation through grants CNS-0969013, CNS-0917021 and CNS-1018108.

# ABSTRACT OF THE DISSERTATION REAL-TIME SCHEDULING OF EMBEDDED APPLICATIONS ON MULTI-CORE PLATFORMS

by

#### Ming Fan

Florida International University, 2014 Miami, Florida

Professor Gang Quan, Major Professor

For the past several decades, we have experienced the tremendous growth, in both scale and scope, of real-time embedded systems, thanks largely to the advances in IC technology. However, the traditional approach to get performance boost by increasing CPU frequency has been a way of past. Researchers from both industry and academia are turning their focus to multi-core architectures for continuous improvement of computing performance. In our research, we seek to develop efficient scheduling algorithms and analysis methods in the design of real-time embedded systems on multi-core platforms. Real-time systems are the ones with the response time as critical as the logical correctness of computational results. In addition, a variety of stringent constraints such as power/energy consumption, peak temperature and reliability are also imposed to these systems. Therefore, real-time scheduling plays a critical role in design of such computing systems at the system level.

We started our research by addressing timing constraints for real-time applications on multi-core platforms, and developed both partitioned and semi-partitioned scheduling algorithms to schedule fixed priority, periodic, and hard real-time tasks on multi-core platforms. Then we extended our research by taking temperature constraints into consideration. We developed a closed-form solution to capture temperature dynamics for a given periodic voltage schedule on multi-core platforms, and also developed three methods to check the feasibility of a periodic real-time schedule under peak temperature constraint. We further extended our research by incorporating the power/energy constraint with thermal awareness into our research problem. We investigated the energy estimation problem on multi-core platforms, and developed a computation efficient method to calculate the energy consumption for a given voltage schedule on a multi-core platform. In this dissertation, we present our research in details and demonstrate the effectiveness and efficiency of our approaches with extensive experimental results.

#### TABLE OF CONTENTS

| CHAPTER                                                                                                                | PAGE     |

|------------------------------------------------------------------------------------------------------------------------|----------|

| 1. INTRODUCTION                                                                                                        | 1        |

| 1.2 The Opportunities And Challenges For Multi-Core Platforms                                                          |          |

| 1.3 The Research Problem And Our Contributions                                                                         |          |

| 1.4 Structure Of The Dissertation                                                                                      | 10       |

| 2. BACKGROUND AND RELATED WORK                                                                                         | 12       |

| 2.1 Real-Time Scheduling                                                                                               | 12       |

| 2.2 Multi-Core Scheduling                                                                                              | 16       |

| 2.3 Power/Thermal Aware Multi-Core Scheduling                                                                          | 17       |

| 2.3.1 Power Aware Multi-Core Scheduling                                                                                | 18       |

| 2.3.2 Thermal Aware Multi-Core Scheduling                                                                              | 21       |

| 2.4 Summary                                                                                                            | 24       |

| 3. PARTITIONED MULTI-CORE SCHEDULING BY EXPLORING HAMONIC RELATIONSHIP AMONG REAL-TIME PERIODIC TASKS 3.1 Related Work | 26<br>26 |

| 3.1.1 Different Utilization Bounds For Single-core Systems                                                             |          |

| 3.1.2 Partitioned Scheduling                                                                                           |          |

| 3.2 Preliminary                                                                                                        |          |

| 3.3 Motivational Examples                                                                                              |          |

| 3.4 Task Partition With An Enhanced RBound                                                                             |          |

| 3.4.1 Task Set Scaling (TSS)                                                                                           |          |

| 3.4.2 Feasibility Relationship Between $\Gamma$ And $\Gamma'$                                                          |          |

| 3.4.3 Enhanced RBound                                                                                                  |          |

| 3.4.4 The Partitioning Algorithm                                                                                       |          |

| 3.5 Harmonic Advantage Exploration With CBound                                                                         |          |

| 3.5.1 Quantifying Harmonic Property                                                                                    |          |

| 3.5.2 Harmonic Aware Partitioned Scheduling                                                                            |          |

| 3.5.3 Schedulability Analysis for HAPS                                                                                 |          |

| 3.6 Experiments And Results                                                                                            |          |

| 3.6.1 Experimental Setup                                                                                               |          |

| 3.6.2 Experiment 1: Efficiency Of Our Enhanced Utilization Bound                                                       |          |

| 3.6.3 Experiment 2: Performance Of Our Partitioned Scheduling Algorithm                                                |          |

| 3.7 Summary                                                                                                            | 60       |

| $4. \ \ {\tt SEMI-PARTITIONED\ MULTI-CORE\ SCHEDULING\ BY\ EXPLORING}$                                                 |          |

| MONIC RELATIONSHIP AMONG REAL-TIME PERIODIC TASKS                                                                      |          |

| 4.1 Related Work                                                                                                       |          |

| 4.2 Preliminary                                                                                                        | 63       |

| 4.2.1 System Models                                                            | 63        |

|--------------------------------------------------------------------------------|-----------|

| 4.2.2 On Semi-Partitioned Scheduling                                           |           |

| 4.2.3 Motivation Examples                                                      | 66        |

| 4.3 The HSP-Light Algorithm                                                    | 67        |

| 4.3.1 Algorithm Details                                                        | 68        |

| 4.3.2 Schedulability Analysis Of HSP-Light                                     | 70        |

| 4.3.3 Fast Schedulability Checking Method For HSP-Light                        | 72        |

| 4.4 The HSP Algorithm                                                          | 78        |

| 4.4.1 Algorithm Details                                                        | 80        |

| 4.4.2 Schedulability Analysis Of HSP                                           |           |

| 4.5 Experiments And Results                                                    |           |

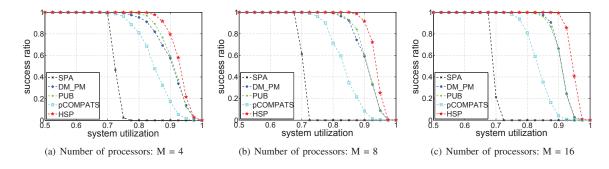

| 4.5.1 Performance VS. Number Of Tasks                                          | 87        |

| 4.5.2 Performance VS. System Utilization                                       | 88        |

| 4.6 Summary                                                                    | 90        |

| 5. TEMPERATURE-CONSTRAINED FEASIBILITY ANALYSIS FO                             | OR MULTI- |

| CORE REAL-TIME SCHEDULING                                                      | 91        |

| 5.1 Related Work                                                               | 91        |

| 5.2 Preliminary                                                                | 93        |

| $5.2.1  \text{System Models}  \dots  \dots  \dots  \dots  \dots  \dots  \dots$ | 93        |

| 5.2.2 Power Model                                                              |           |

| 5.2.3 Thermal Model                                                            | 95        |

| 5.2.4 Problem Description                                                      |           |

| 5.3 Temperature Calculation For Multi-core Scheduling                          |           |

| 5.3.1 Temperature Formulation Within A State Interval                          | 97        |

| 5.3.2 Temperature Formulation For A Periodic Schedule                          |           |

| 5.3.3 Steady-State Temperature Formulation                                     | 102       |

| 5.4 Identifying The Peak Temperature                                           |           |

| 5.4.1 Challenging Problem In Peak Temperature Detection                        |           |

| 5.4.2 Important Properties For Multi-core Temperature Variation .              |           |

| 5.4.3 Peak Temperature Detection Within A State Interval                       |           |

| 5.4.4 $$ Peak Temperature Detection For A Periodic Schedule                    |           |

| 5.5 Feasibility Analysis For Multi-Core Scheduling With Temperature            |           |

| straint                                                                        |           |

| 5.5.1 TmaxCheck: Feasibility Checking With Initial Temperature A               |           |

| 5.5.2 ModeCheck: Feasibility Checking With Temperature Safe Mod                |           |

| 5.5.3 TssCheck: Feasibility Checking With Steady-State Temperature             |           |

| 5.6 Experimental Evaluations                                                   |           |

| 5.6.1 Accuracy Analysis Of Our Analytical Temperature Calculation              |           |

| 5.6.2 Steady-State Peak Temperature Variation Under Different Co               |           |

| Speeds $\dots$                                                                 |           |

| 5.6.3 Threshold Temperature Determined By TmaxCheck $\dots$                    |           |

| 5.6.4 Worst-Case Equilibrium Voltage Determined By ModeCheck .                 | 126       |

| 5.6.5 Performance Comparison For Different Feasibility Checking Methods . 128 |

|-------------------------------------------------------------------------------|

| 5.7 Summary                                                                   |

| 6. LEAKAGE-AWARE ENERGY ESTIMATION FOR MULTI-CORE REAL-                       |

|                                                                               |

| TIME SCHEDULING                                                               |

| 6.1 Related Work                                                              |

| 6.2 Preliminary                                                               |

| 6.2.1 System Models                                                           |

| 6.2.2 Temperature Calculation                                                 |

| 6.3 Energy Calculation For Multi-Core Scheduling With Thermal Awareness 135   |

| 6.4 Experiments And Results                                                   |

|                                                                               |

| 6.4.1 Experimental Setup                                                      |

| 6.4.2 Accuracy Analysis                                                       |

| 6.4.3 Time Efficiency Analysis                                                |

| 6.5 Summary                                                                   |

| 7. CONCLUSIONS AND FUTURE WORK                                                |

| 7.1 Summary                                                                   |

| 7.2 Future Work                                                               |

|                                                                               |

| v v v                                                                         |

| 7.2.2 Preliminary Results                                                     |

| BIBLIOGRAPHY                                                                  |

| VITA                                                                          |

#### LIST OF TABLES

| TAB | ELE                                           | P | AGE   |

|-----|-----------------------------------------------|---|-------|

| 3.1 | A task set with six real-time periodic tasks  |   | . 34  |

| 3.2 | A task set with four real-time periodic tasks |   | . 35  |

| 4.1 | A task set with five real-time tasks          |   | . 66  |

| 4.2 | A task set with four real-time tasks          |   | . 79  |

| 5.1 | HotSpot parameters and floorplan              |   | . 121 |

| 5.2 | Power/thermal parameters                      |   | . 122 |

| 6.1 | HotSpot parameters and floorplan              |   | . 139 |

| 6.2 | Power/thermal parameters                      |   | . 139 |

#### LIST OF FIGURES

| FIGU | JRE                                                                                                                                                                                                                    | PA         | GE |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|

| 1.1  | Embedded system market [114]                                                                                                                                                                                           |            | 2  |

| 1.2  | Demand for multi-core based devices                                                                                                                                                                                    |            | 4  |

| 1.3  | Fraction of chip reachable in one clock cycle [6, 103]                                                                                                                                                                 |            | 5  |

| 1.4  | Time line of multi-core development [117]                                                                                                                                                                              |            | 7  |

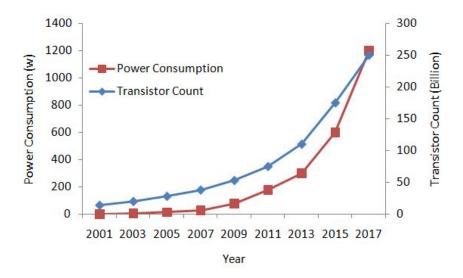

| 1.5  | The trend of power consumption and transistor count for a 300mm die [24]                                                                                                                                               | $n^2$      | 8  |

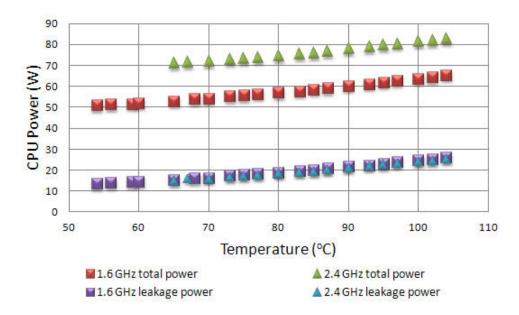

| 2.1  | Power v.s. Temperature [55]: Intel Core i5-2500K (32nm Sandy Bridge voltage 1.26V, frequency at 1.6 GHz and 2.4 GHz, respectively.                                                                                     |            | 18 |

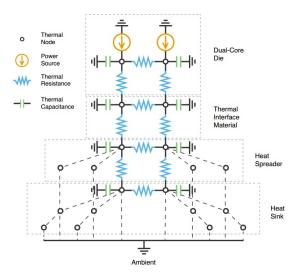

| 2.2  | Illustration for RC thermal circuit on a dual-core system $\ [116]\ $                                                                                                                                                  |            | 22 |

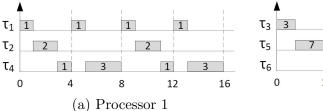

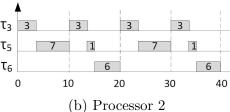

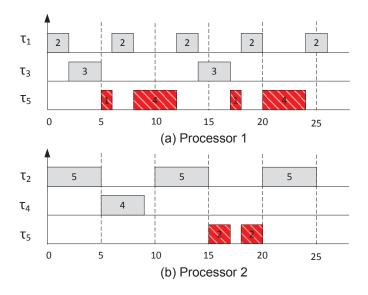

| 3.1  | Assign tasks in Table 3.1 based on ideal harmonic relationship, and a tasks can be scheduled successfully on two processors                                                                                            |            | 34 |

| 3.2  | Assign tasks in Table 3.2 based on pCOMPACTS [66], while $\tau_4$ missin its deadline                                                                                                                                  | g<br>      | 35 |

| 3.3  | Assign tasks in Table 3.2 based on closely harmonic relationship, an all tasks can be scheduled successfully on two processors                                                                                         |            | 36 |

| 3.4  | Proof of Theorem 3.4.1: given a task set $\Gamma$ with $T_1 \leq T_2 \leq T_N$ an $\tau_N = (C_N, T_N)$ , transform $\Gamma$ into $\Gamma^*$ such that $\tau_N^* = (kC_N, kT_N)$ an $\tau_i^* = \tau_i, \forall i < N$ | d<br>d<br> | 39 |

| 3.5  | Efficiency of our enhanced utilization bound on a single core                                                                                                                                                          |            | 54 |

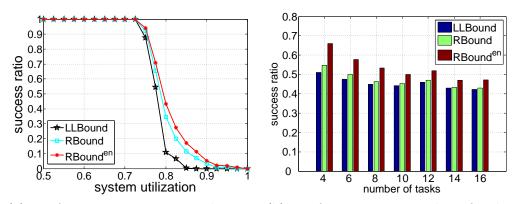

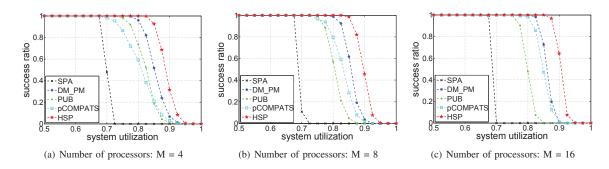

| 3.6  | Experimental results for light task sets $(u_i \in [0, 0.5])$                                                                                                                                                          |            | 55 |

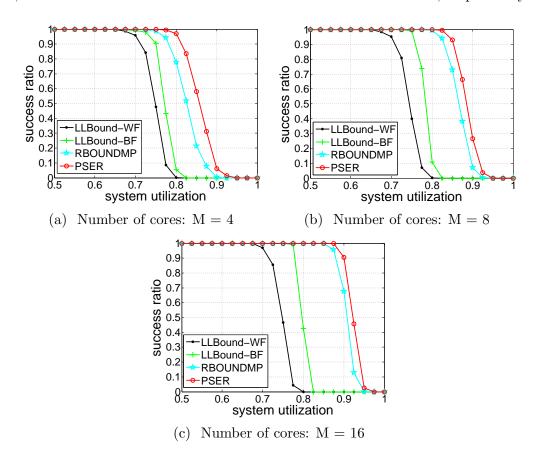

| 3.7  | Experimental results for light task sets $(u_i \in [0, 0.5])$ by different systemutilization                                                                                                                           | n<br>      | 58 |

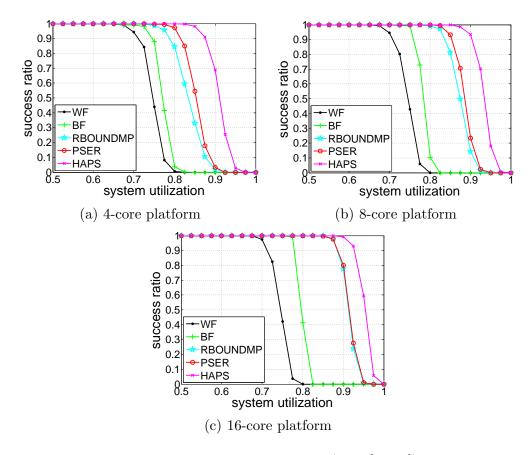

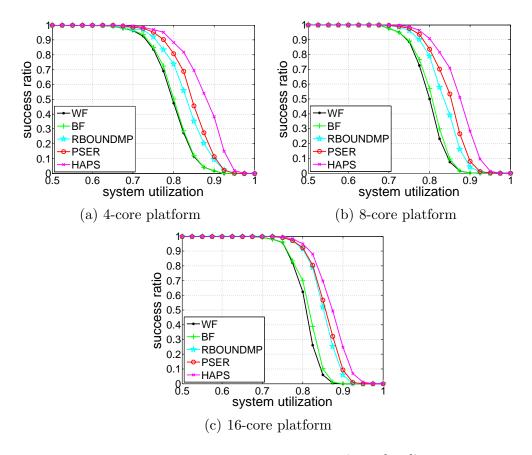

| 3.8  | Experimental results for general task sets $(u_i \in [0,1])$ by different systemutilization                                                                                                                            |            | 59 |

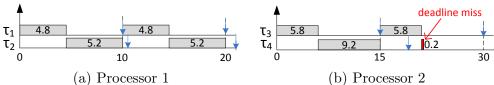

| 4.1  | Allocation fails when simply grouping harmonic tasks and assigning them to the same processor.                                                                                                                         |            | 66 |

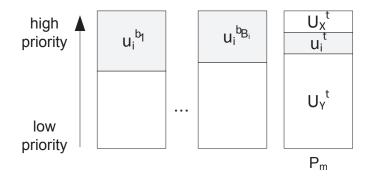

| 4.2  | Illustration of $U_X^t$ and $U_Y^t$                                                                                                                                                                                    |            | 76 |

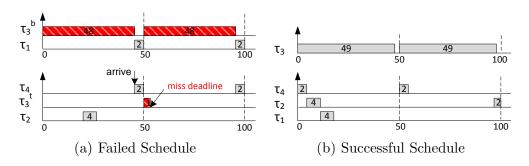

| 4.3  | (a) The task set is failed to be scheduled according to HSP-light; (by The task set is schedulable if the heavy task $\tau_2$ is pre-assigned.                                                                         | o)<br>· ·  | 79 |

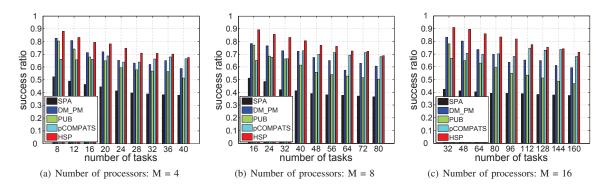

| 4.4  | Experimental results for general task sets by different number of tasks                                                                                                                                                | S          | 87 |

| 4.5  | Experimental results for light task sets, $u \in [0, 0.5]$                                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.6  | Experimental results for general task sets, $u \in [0,1]$ 89                                                                                                                                                                  |

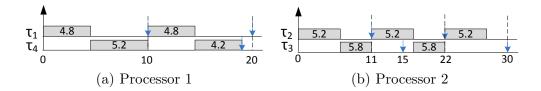

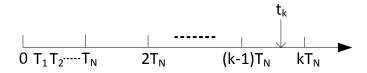

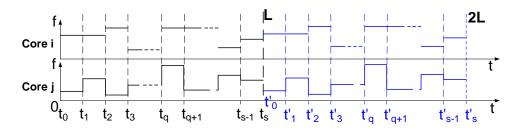

| 5.1  | A speed schedule within 2 scheduling periods                                                                                                                                                                                  |

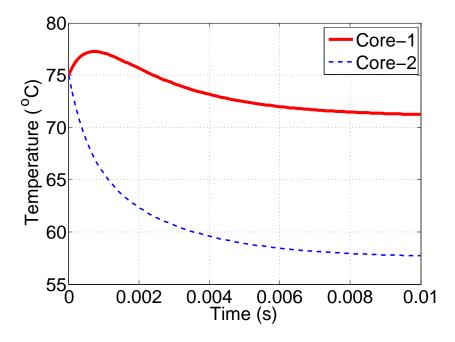

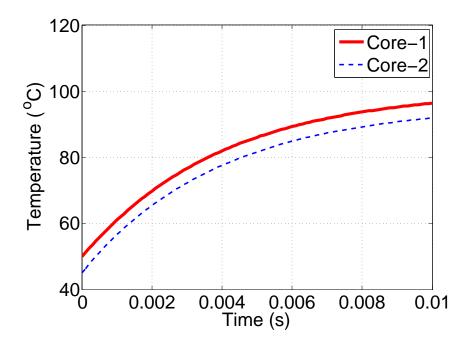

| 5.2  | Negative interaction on temperature variation between two cores. $C_1 = C_2 = 0.00035$ , $G_{11} = G_{22} = 0.4$ , $G_{12} = G_{21} = -0.1$ , $v_1 = 0.8V$ , $v_2 = 0V$ , $T_1(0) = T_2(0) = 75^{\circ}C$                     |

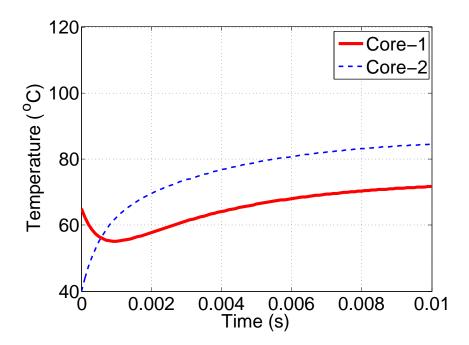

| 5.3  | $T_i(t)$ increases at both time $t_0$ and $t_1$                                                                                                                                                                               |

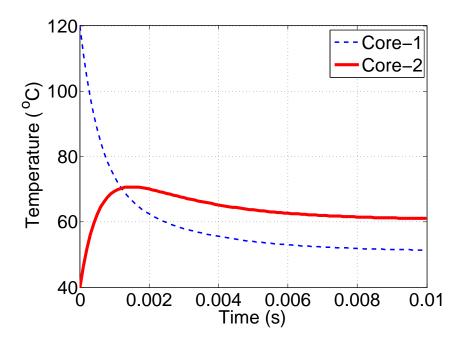

| 5.4  | $T_i(t)$ decreases at time $t_0$ and increases at time $t_1$                                                                                                                                                                  |

| 5.5  | $T_i(t)$ increases at time $t_0$ and decreases at time $t_1$                                                                                                                                                                  |

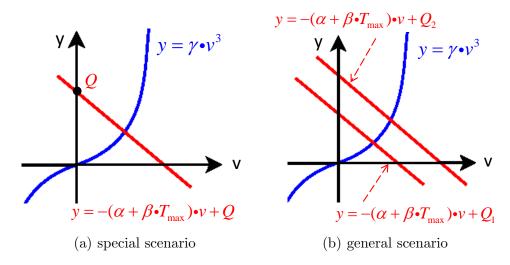

| 5.6  | Equilibrium voltage of core $C_i$ under processing mode $k_i$ . a) all other cores except $C_i$ are under fixed constant processing modes; b) all other cores except $C_i$ are under any arbitrary available processing modes |

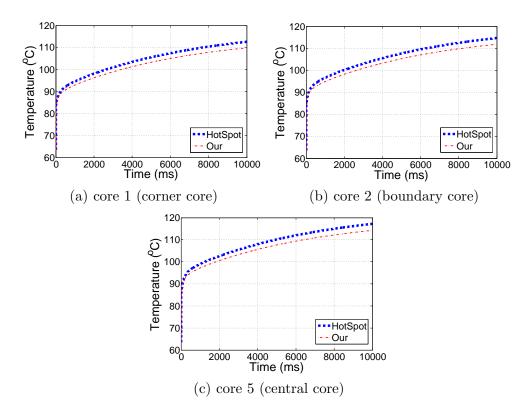

| 5.7  | Accuracy analysis of our proposed temperature calculation method 123                                                                                                                                                          |

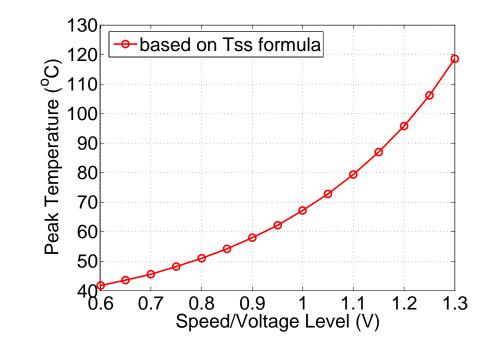

| 5.8  | Steady-state temperature under different constant speeds with our analytical steady-state temperature formula                                                                                                                 |

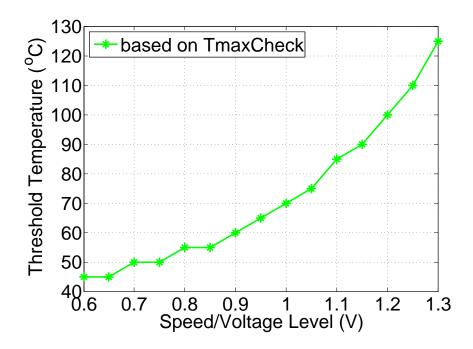

| 5.9  | Threshold temperature determined by TmaxCheck under different voltages                                                                                                                                                        |

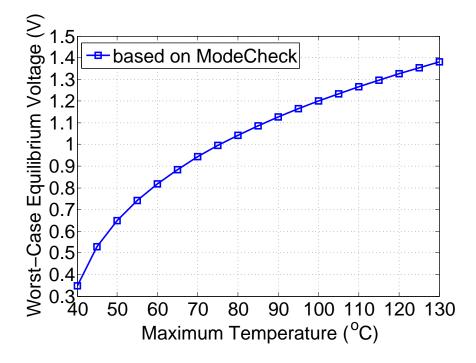

| 5.10 | Worst-case equilibrium voltage determined by ModeCheck under different maximum temperature constraints                                                                                                                        |

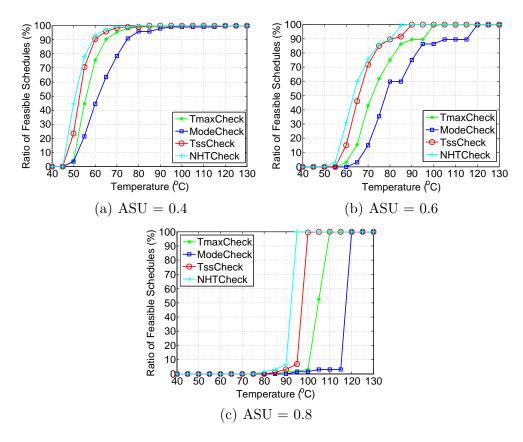

| 5.11 | Feasibility ratios under different maximum temperatures                                                                                                                                                                       |

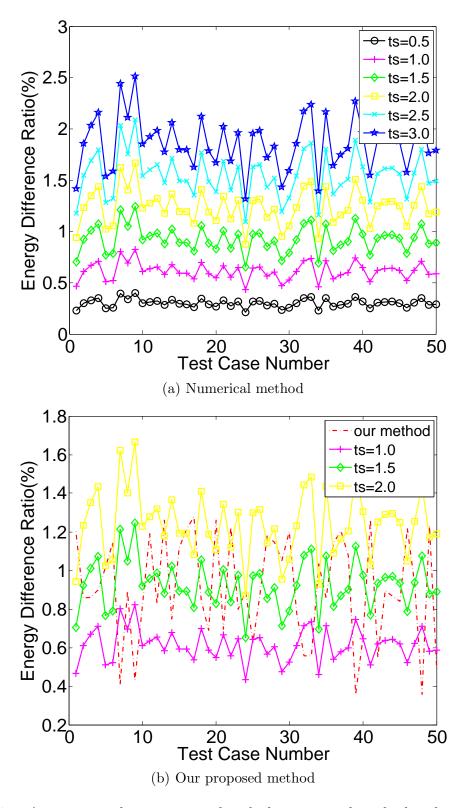

| 6.1  | Accuracy analysis, compared with the numerical method under $t_s = 0.01 \ 141$                                                                                                                                                |

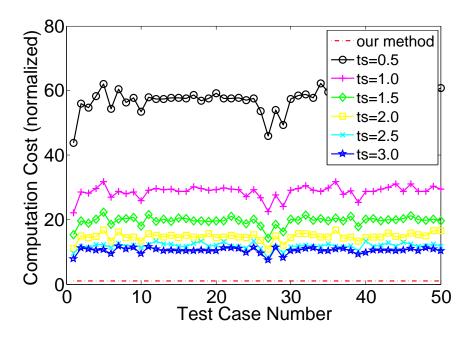

| 6.2  | Time efficiency analysis, normalized with our method                                                                                                                                                                          |

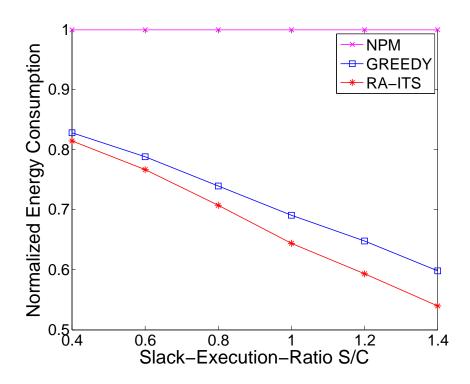

| 7.1  | Impact of slack on energy consumption                                                                                                                                                                                         |

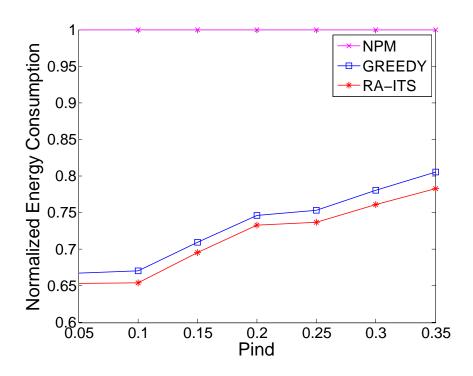

| 7.2  | Impact of $P_{ind}$ on energy consumption                                                                                                                                                                                     |

#### CHAPTER 1

#### INTRODUCTION

Real-time embedded systems have been ubiquitous. From cell phones to digital cameras, from transportation to industry controls, from medical instruments to home entertainment systems, such systems affect almost every aspects of our daily life. In the meantime, to cater to the growing demand of high computing performance for these systems, the traditional approach of increasing speed for single processor has been a way of past. Instead, multi-core architecture is becoming mainstream.

In this chapter, we first introduce the basics on real-time embedded systems. Then we discuss the opportunities and critical challenges in design of real-time systems on multi-core platforms. Next, we define our research problem and briefly summarize our contributions. Finally, we present the structure of this dissertation.

#### 1.1 Real-Time Embedded Systems

Real-time embedded systems are systems dedicated to special applications with real-time constraints in an embedded mechanical or electrical environment [54]. In a real-time embedded system, the timing constraints can be critical and need to be guaranteed, for reasons such as safety and usability. A late response, even coming with a logical correct result, can cause a degraded quality of service (QoS), or even a catastrophical accident [106].

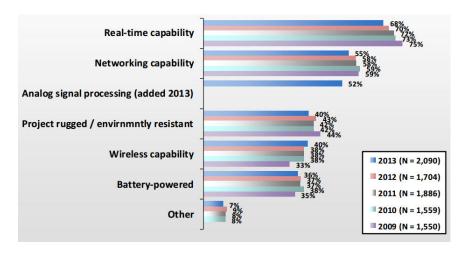

Real-time embedded systems have been widely used in a variety of devices across a wide range of applications such as mobile phones, electronic game devices, motor vehicles, medical equipments, avionic products, etc. The embedded system market was valued at 121 billion dollars in 2011, and is expected to reach 194 billion dollars by 2018 [3]. Among all these systems/applications, it is reported in 2013 up to 68%

of all embedded system devices have the real-time capability [114] (see Figure 1.1). Real-time embedded systems have become indispensable in our daily life.

Figure 1.1: Embedded system market [114]

Due to the application nature, there are a large variety of different real-time embedded systems. In general, real-time embedded systems can be classified along different criteria. From the perspective of the nature of deadlines, real-time embedded systems can be hard or soft. Hard real-time systems require deterministic guarantee to meet all deadlines for every instance, and the failure to meet even a single deadline can be catastrophic. For example, aviation control system and automobile's ABS system are hard real-time systems. On the other hand, soft real-time systems are the systems that allow for a statistical bound on the number of deadline misses, which are neither desirable nor fatal. Examples of such systems include media streaming in distributed systems and non-mission-critical tasks in control systems. Despite large variations of real-time embedded systems, one unique common feature of real-time embedded systems is that they are usually tightly resource constrained. For instance, beside timing, real-time embedded systems are also constrained by size, weight, power/energy, temperature, reliability, etc. Due to limited resources in most of embedded devices, the problem of how to improve the perfor-

mance meanwhile satisfying other resource constraints becomes important. Take the mobile phones as an example, they have essential restrictions on size, weight, thermal and power. Power is particularly important, as these portable devices largely depend upon the battery-life to deliver high performance [107, 127]. To achieve high computational performance within limited and constrained resources, an appropriate real-time scheduling strategy for such embedded systems is desired.

The real-time scheduling is concerned with the allocation and management of the resources to complete the assigned workload within timing constraints. In a real-time embedded system, the scheduling strategy directly affects the application's execution and thus further affects the computing performance. Moreover, the scheduling strategy also brings significant impact on other system performances, i.e. power/energy, thermal, reliability, etc. There is no doubt that real-time scheduling plays a critical role in embedded systems. Thus, it is important to design effective and efficient scheduling techniques for real-time embedded systems.

From the processor architecture point of view, real-time embedded systems can be categorized as either single-core or multi-core systems. The single-core system is built by integrating only one processing core into a single chip, while the multi-core system integrates multiple processing cores into the same chip. Over two decades, it has been a common strategy to increase the computing performance by building more complex single-core architecture and increasing working frequency. Such kind of advancement has been largely driven by the continuous scaling of the transistor feature size that facilitates exponential transistor integration capacity (doubling every 2 years, Moore's law). However, under current technology, the power issue has become a critical bottleneck for further increasing the computing performance on single-core systems. Fortunately, multi-core systems can mitigate the power issue and thus provides capability to further increase the computing performance.

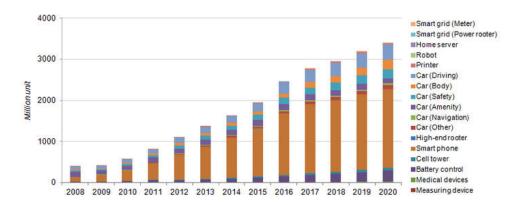

Figure 1.2: Demand for multi-core based devices

Today, multi-core systems have been the mainstream of microprocessor market in various fields. For example, multi-core platforms are widely used from personal electronic devices (e.g. smart phones, PCs, tablets and tablets) to system servers and data centers. Moreover, there is a quick increase of multi-core devices in the commercial market. The data shown in Figure 1.2 was gathered by one research company [2], and shows the annual increase in the number of multi-core processors delivered in select industries. Based on this research, starting from 2012, there is approximately a 40% annual increment in the shipment of multi-core microprocessors. As multi-core architecture is becoming more and more popular, there is a quick emerging towards multi-core for real-time embedded systems. In the following section, we discuss the opportunities as well as challenges coming with the multi-core technology.

### 1.2 The Opportunities And Challenges For Multi-Core Platforms

Since early 2000, industry has begun to change its focus from single-core to multicore platforms. One major reason for this platform shift is that, in 2002, the classical

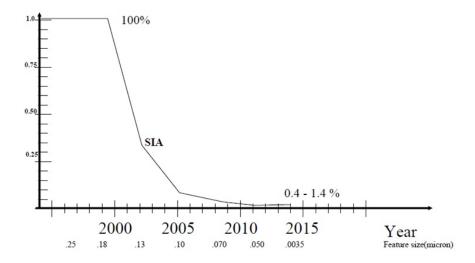

Figure 1.3: Fraction of chip reachable in one clock cycle [6, 103]

approach for increasing computing performance (by scaling the transistor size and increasing the clock frequency) reached a physical limit, i.e. the entire chip could not be reached in one clock cycle. This means that the performance could not be continuously increased under the traditional way of transistor technology scaling. Figure 1.3 shows the fraction of chip reachable in one clock cycle with respect to year and technology. From Figure 1.3, we can see that starting from 2000, there is an exponential drop in the percentage of chip achieved in one clock cycle. In fact, the trend of increasing the speed of processor to increase the computing performance is a way of past.

Multi-core platforms bring innovative solutions to overcome the limitations of single-core platforms, such as power/thermal limitation and instruction level parallelism limitation [15]. First, the power and thermal issues have become a crucial limitation in single-core design. The extremely high power consumption and excessive heat dissipation have posed critical challenges for continuously pursing high computing performance on a single-core chip [112]. However, multi-core platforms, compared with single-core platforms, can alleviate the power and thermal issues

with the same performance achievement. Instead of continuously scaling transistor size or increasing clock frequency only on a single core, multi-core platforms can increase the computing performance by increasing the number of processing cores on the same chip with lower transistor integration density and/or clock frequency. Secondly, single-core platforms confront with instruction level parallelism limitation. Single-core architectures attempting to gain performance from techniques such as wide issue and speculative execution achieve modest increase in performance at the cost of significant overhead in area and energy [15]. Nevertheless, multi-core platforms improve the computing performance by exploiting the "thread/data level parallelism". For instance, in a multi-core system, if all tasks are highly parallelized among all cores, it would come out with high parallel executions. Therefore, multi-core technology bring promising opportunities to further improve the computing performance.

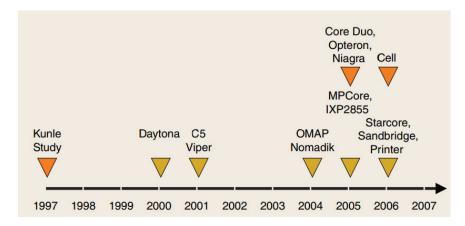

The study on multi-core platforms is long and rich, while the history of manufactured multi-cores has only a few decades. Figure 1.4 shows some significant time line for the development of multi-core systems [117]. In 1972, one of the most early studies on multi-cores, called Illiac IV [25] consisting of 64 arithmetic logic units (ALUs), was proposed to perform parallel computing for vector and array operations. The first significant study on general purpose multi-core was performed by Hammond [46] in 1997 (shown in the figure as the Kunle study). However, the first manufactured multi-core appeared in the marketplace was in 2000 by AT&T Daytona [5]. Most of other major manufacturers followed successively to launch their multi-core chips: the C-5 by C-Port Corp. for networking, the viper by Phillips for multimedia, the OMAP by Texas Instruments for baseband processing, the MPCore by ARM for configurable design, the IXP2855 by Intel for network communication, and the Starcore by Sandbridge Technologies for signal processing. Today, multi-

core platforms have been broadly supported by most of chip vendors, including Intel, AMD, ARM, IBM, Nvidia, Freescale Semiconductor, Sum microsystems, etc.

Figure 1.4: Time line of multi-core development [117]

When moving to multi-core platforms, it comes with new critical challenges in design of real-time systems. First, in a multi-core system, the scheduler needs to determine not only when a given application executes but also where it executes such that the system resources can be effectively and efficiently utilized. This problem, so called *partitioning* problem, is an NP-hard problem in nature [106]. Second, by taking the timing constraints of real-time applications into consideration, the problem of multi-core real-time computing becomes even more complicated. For example, with consideration of the dependency among different applications, the benefit coming from parallel executions of a multi-core system could be seriously suffered from guaranteeing real-time constraints [10]. There are critical challenges in design of real-time multi-core scheduling.

Secondly, the extremely high power consumption and excessive heat dissipation have also become the critical challenges in design of multi-core systems [112]. As shown in Figure 1.5<sup>1</sup>, more than 100 billion transistors are being integrated in a  $300mm^2$  die today, which results in a power consumption up to 300 watts. These

<sup>&</sup>lt;sup>1</sup>Figure 1.5 is plotted based on the data reported in [24].

Figure 1.5: The trend of power consumption and transistor count for a  $300mm^2$  die [24]

amount of power consumption has posed significant challenges in both portable devices and power-rich systems. The soaring power consumption makes the heat dissipation and the temperature control even more challenging, e.g. the severity of the thermal problem has been highlighted by Intel's acknowledgement that it has hit a "thermal wall" [91].

Moreover, techniques and analysis methods for single-core platforms cannot be readily applicable for multi-core platforms. The traditional solutions on power, thermal and energy problems associated with single-core platforms could become ineffective without taking the multi-core characteristics (e.g. heat transform, hot spot and thermal gradient) into consideration [97]. Therefore, in order to take the opportunities and advantages of multi-core technology, it is necessary and important to appropriately consider and address the new emerging challenges.

From the above discussion, we can see that the design of multi-core systems faces new opportunities as well as various challenges. In what follows, we describe our research problem in this dissertation, and briefly summarize our contributions.

#### 1.3 The Research Problem And Our Contributions

We are interested in the research problem on how to develop advanced techniques for real-time embedded systems on multi-core platforms. Researchers and engineers from both academia and industry have been working on this problem at different design abstraction levels, i.e. from gate level, circuit level, architecture level, to system level. Our research focuses on attacking this problem from the system level. Specifically, we are interested in developing real-time scheduling techniques and analysis methods to guarantee timing and other design constraints, and in the meantime, to optimize design criteria such as system utilization, peak temperature, power and energy consumption. Toward this problem, we have made the following contributions:

- 1. First, we studied the classical problem of partitioned scheduling of real-time periodic tasks on multi-core platforms, with each task executed on a dedicated core. By taking the relationship among task periods into consideration, we developed several novel partitioned scheduling approaches for scheduling fixed-priority periodic real-time tasks on multi-core systems. Our proposed algorithms can greatly improve the schedulability of real-time tasks, and thus improve the system utilization. Compared with the related work, we found that our proposed algorithms could achieve an improvement at least of 14.5% in terms of task set schedulability under high system utilizations.

- 2. Then, we targeted at the problem of semi-partitioned multi-core real-time scheduling, in which most of tasks were executed on dedicated cores, while some tasks could be split and executed on different cores. We developed two new semi-partitioned scheduling strategies for hard periodic real-time tasks on multi-core systems. We also developed a deterministic worst-case utilization

bound for the proposed approaches. Simulation studies showed that our approaches could outperform the related work by 15% from the perspective of task set schedulability when systems were heavy loaded.

- 3. Next, we incorporated the temperature constraint into the problem of multicore real-time scheduling. We developed a closed-form solution for temperature calculation for periodic speed scheduling on multi-core platforms. We

further developed an effective method that can quickly obtain the maximum

temperature for a periodic multi-core schedule. To our best knowledge, this

is the first work that analytically solves the temperature calculation and peak

temperature detection on multi-core platforms with consideration of a linear

dependency model of leakage and temperature. Based on our proposed techniques, we proposed three feasibility testing approaches for multi-core scheduling with maximum temperature constraint.

- 4. Finally, we studied the energy estimation problem in multi-core scheduling. We developed a fast and accurate solution of energy calculation on multi-core systems with consideration of the interdependency of leakage, temperature and supply voltage. Our solution provides a fundamental for design of energy aware multi-core systems, and can be directly used for energy efficient multi-core scheduling. The experimental results showed that our proposed method can achieve an average speedup of 15X over the existing related work, with a relative error no more than 1.5%.

#### 1.4 Structure Of The Dissertation

The rest of this dissertation is organized as follows. In Chapter 2, we introduce some pertinent background to this dissertation, and discuss the existing work closely re-

lated to our research. In Chapter 3, we study the problem of partitioned multi-core scheduling for periodic real-time tasks, and present a new partitioned scheduling strategy by exploring the "harmonic" characteristic. In Chapter 4, we focus our research in semi-partitioned multi-core scheduling, and propose an efficient scheduling algorithm with bounded worst-case system utilization and limited count of split tasks. In Chapter 5, we study the feasibility checking problem for temperature-constrained multi-core scheduling, and propose three feasibility checking conditions for multi-core scheduling with maximum temperature constraint. In Chapter 6, we present an energy estimation approach for multi-core systems with consideration of the interdependency between leakage power and temperature. Finally, in Chapter 7, we conclude this dissertation and discuss the possible future work.

#### CHAPTER 2

#### BACKGROUND AND RELATED WORK

This chapter presents the pertinent research background and related work. We first introduce several important concepts related to real-time scheduling. Then, we introduce some preliminaries for multi-core scheduling. Next, we discuss the research problems and related work on power/thermal aware multi-core scheduling. Finally, we summarize the contents of this chapter.

#### 2.1 Real-Time Scheduling

In a real-time system, the correctness of an execution result depends not only on the correctness of the logical computational results, but also on the time instant at which that result is finished. We can describe a real-time system as a system that has deadlines. The violations of timing constraints in real-time systems degrade the quality of service, and in some cases result in catastrophical accidents [83, 106]. To guarantee the timing constraints, one effective way is to design an appropriate scheduling algorithm.

In general, the real-time scheduling studies the problem of how to determine when and where a given set of tasks need to be executed such that all real-time constraints (e.g. deadlines) can be guaranteed, and meanwhile some other design metrics (e.g. temperature, power/energy consumption and reliability) can be optimized.

There are different ways to categorize the real-time scheduling. From the perspective of job characteristics, real-time scheduling can be categorized into hard/soft [28, 69], periodic/non-periodic [30, 49], etc. From the perspective of scheduling mechanisms, real-time scheduling can be categorized into static/dynamic [68, 76], priority-driven/non-priority-driven [98, 27], preemptive/non-preemptive [45, 35], etc. From

the perspective of underlying architectures, real-time scheduling can be categorized into single-core/multi-core [81, 38]. From the perspective of design objectives, real-time scheduling can be categorized into single-objective/multiple-objective (e.g. timing constraints only or more other design objectives such as power/energy, thermal, reliability) [71, 37]. In what follows, we discuss the details of the above categorizations to clearly understand the behaviors of real-time scheduling.

Hard Real-Time vs. Soft Real-Time: A hard real-time scheduling requires deterministic guarantee to meet all deadlines for every instance, and the failure to meet even a single deadline can be catastrophic. Examples of hard real-time scheduling can be found in aviation control system and automobile's ABS. In contrast, a soft real-time scheduling allows for a statistical bound on the number of deadline misses, which are neither desirable nor fatal. Examples of soft real-time scheduling can be found in multimedia player systems, in which occasionally missing of deadlines does not effect the normal operations of the system, however, the quality of service may degrade.

Periodic vs. Non-Periodic: In a periodic scheduling, jobs/instances coming from the same task are released periodically with a minimum length of inter-arrival time between any two consecutive jobs. In other words, tasks are invoked at regular intervals following a determinate pattern of time intervals. For example, in air traffic control(ATC) system, the status of each aircraft is monitored using active radars. These radars check the status periodically and update the ATC controller [83]. In an aperiodic scheduling, each task is modeled as a sequence of jobs with unknown/indeterminate release time, thus all tasks are invoked in irregular pattern and the inter-arrival time between consecutive jobs in such a task may vary widely. For instance, in a setting of radar surveillance system, the system should be responsive to operator's commands but not on the expense of task with hard deadline.

Static vs. Dynamic: Static scheduling determines the priorities of tasks only based on the off-line available information. In other words, priorities of tasks are assigned before compile time and remain unchanged throughout the execution [81], e.g. rate monotonic scheduling (RMS). Dynamic scheduling makes scheduling decisions based on the run-time information, thus the priority of each job/task becomes known to the scheduler only after that job is released during on-line execution, e.g. earliest deadline first (EDF).

Priority-Driven vs. Non-Priority-Driven: In priority driven real-time scheduling, at any scheduling decision time instant, the jobs with the highest priorities are scheduled and executed on the available processors. Other commonly used names for this approach are greedy scheduling, list scheduling and work-conserving scheduling [83]. Some examples of priority-driven scheduling include EDF, RMS [81], etc. On the other hand, in non-priority driven scheduling, decisions are made based on, instead of priority criteria, some other criteria or policy (e.g. the round-robin policy) to determines if a task should start executing or not [113].

**Preemptive vs. Non-Preemptive**: If the execution of lower priority task is stopped or preempt for a higher priority task then the scheduling scheme is called as preemptive scheduling and otherwise non-preemptive scheduling [12, 27].

Single-Core vs. Multi-Core: Based on type of underlying architectures, real-time scheduling can be categorized into single-core scheduling [81] and multi-core scheduling [106]. One major difference of multi-core over single-core scheduling is that, in multi-core scheduling, we need to decide not only when but also where a task should be executed. Multi-core scheduling, known as a NP-hard problem [106], is more complicated compared with single-core scheduling.

Timing-Constrained vs. Multiple-Constrained: The classical timing-constrained real-time scheduling exclusively focus on timing constraints, while the multiple-

constrained real-time scheduling incorporates other design objectives such as power/energy[56], thermal [82] and reliability [49].

Two single-core priority-based preemptive scheduling policies, i.e. Earliest Deadline First(EDF) and Rate Monotonic Scheduling (RMS), are of special interest and great importance [81]. These two scheduling policies play a fundamental role in design of real-time scheduling.

Earliest Deadline First (EDF): The EDF is a preemptive, dynamic-priority scheduling algorithm. Task's priorities are assigned dynamically during run time. The task with the least time remaining before its deadline acquires the highest priority and thus executed before others. In fact, it is proved in [81] that if a task set is schedulable, then EDF algorithm can schedule it. Due to its 100% utilization bound, EDF becomes the underlying scheduling algorithm for a number of other scheduling techniques with different design objective, such as the "low power EDF" algorithm proposed in [119].

Rate Monotonic Scheduling (RMS): Under the fixed-priority RMS policy, tasks' priorities are assigned based on their periods. It is shown by Liu and Layland [81] that RMS is the optimal among all fixed-priority scheduling policies. They have proved that a feasible schedule can be found by using RMS if the total utilization is less than or equal to ln(2) (69.3%).

Both EDF and RMS have been used extensively in the research domain as the underlying scheduling policy for other design metrics optimization like energy minimization ([98, 133, 99]), schedulability/feasibility analysis ([4, 97]), etc.

#### 2.2 Multi-Core Scheduling

Multi-core architecture has been widely accepted as the most important technology in the future industrial market. By providing multiple processing cores on a single chip, multi-core systems, compared with the traditional single-core systems, can significantly increase the computing performance while relaxing the power requirement. Most of the major chip manufactures have already launched 16-core chips into the market, i.e. AMD Opteron<sup>TM</sup> 6300 Series [7]. It is not surprising that in the coming future, hundreds or even thousands of cores will be integrated into a single chip [121]. The quickly emerging trend towards multi-core platforms brings urgent needs for effective and efficient techniques for the design of multi-core scheduling.

Multi-core scheduling can be categorized into different classes based on different criteria, i.e. homogeneous/heterogeneous (from the perspective of underlying architectures) [40, 105], global/partitioned/semi-partitioned (from the perspective of scheduling mechanisms) [9, 10, 39], timing-constrained/multiple-constrained (from the perspective of design constraints) [8, 115], etc.

Homogeneous vs. Heterogeneous: On a homogeneous platform, all processing cores are identical, hence the rate of execution of all tasks is the same among all cores. Thus, the scheduling strategy only needs to concern the execution time of each task. While on a heterogeneous platform, since the processing cores are different, hence the rate of execution of a task depends on both the core and the task. Indeed, not all tasks may be able to execute on all processors. Thus, the design of multi-core scheduling for heterogeneous platforms becomes more complicated.

Global vs. Partitioned vs. Semi-Partitioned: In the global scheduling approach, all jobs first enter a global queue, and thus each task can be potentially executed on any processor [9, 40]. In the partitioned scheduling approach, each

real-time task is assigned to a dedicated processor. All instances from the same task will be executed solely on that particular processor [10, 38]. The semi-partitioned scheduling approach is a combination of previous two approaches, i.e. some tasks are assigned to a dedicated processor, while rest can migrate among available resources [69, 72, 43, 39].

Timing-Constrained vs. Multiple-Constrained: Traditional approaches focus exclusively on timing constraints [10, 8, 34, 39], and many recent work takes other design objectives (e.g. power/energy, thermal and reliability) into considerations, which makes the scheduling problem more complicated [61, 51, 58, 57, 49].

One of the most common and useful performance metrics used to compare the effectiveness of different multi-core scheduling algorithms and schedulability analysis is the utilization bound. The utilization bound for a scheduling algorithm is defined as the minimum utilization of any taskset that is only just schedulable according to that algorithm. The best known utilization bound for either global or partitioned schedule under RMS is no more than 50% [10, 13, 9], while the utilization bound can reach up to 69.3% for semi-partitioned scheduling under RMS [43, 44, 39]. There are also other metrics to evaluate performances for different multi-core scheduling algorithms, i.e. approximation ratio (the ratio of the number of required processors of a multi-core scheduling algorithm over that of the optimal algorithm), and empirical system schedulability (the percentage of tasksets that are found to be schedulable).

#### 2.3 Power/Thermal Aware Multi-Core Scheduling

The continuously increased power consumption has resulted in a soaring chip temperature. Moreover, as design paradigm shifts to deep sub-micron domain, high chip temperature leads to a substantial increase in leakage power consumption [60],

Figure 2.1: Power v.s. Temperature [55]: Intel Core i5-2500K (32nm Sandy Bridge), voltage 1.26V, frequency at 1.6 GHz and 2.4 GHz, respectively.

which in turn further deteriorates the power situation due to the interdependency between temperature and leakage power. For instance, with Intel core i5-2500K (32nm Sandy Bridge), the leakage power roughly grows up to 2X from  $55^{\circ}C$  (13W) to  $105^{\circ}C$  (26W), see Figure 2.1. Further more, the soaring chip temperature adversely impacts the performance, reliability, and packaging/cooling costs [97]. As a result, power and thermal issues have become critical and significant for advanced multi-core system design. In this section, we introduce some necessary backgrounds of multi-core scheduling with power and thermal awareness, respectively.

#### 2.3.1 Power Aware Multi-Core Scheduling

Catalyzed by continuous transistor scaling, hundred of billions of transistors have been integrated on a single chip [60]. One of the immediate consequence caused by the tremendous increase of transistor density is the soaring power consumption [18], which further results in severe challenges in energy and temperature [57, 97]. Today,

power has become a critical and challenging design objective in front of system designers. In this subsection, we first describe our research problem on power aware multi-core scheduling, next introduce the general power model, and then discuss the related work.

#### Research Problem of Power Aware Scheduling

Power aware scheduling studies the problem on how to apply the *dynamic voltage* and frequency scaling (DVFS) mechanism to adjust the clock frequency and supply voltage of a processor to execute a set of tasks such that the time constraints (e.g. deadlines) can be guaranteed and meanwhile the power and/or energy consumption can be optimized.

#### Power Consumption

The overall power consumption of an IC chip can be divided into two categories: dynamic power and leakage power [102]. The dynamic power consumption is associated with the switching of the logic value of a gate, and thus is essential to performing useful logic operation by charging and discharging the circuit load capacitance. In general, the dynamic power is modeled as function in proportion to working frequency and square of supply voltage [102]. The leakage power, also known as static power, is consumed due to the leakage mechanism of a CMOS transistor and it does not contribute to any useful computation. Traditionally, the leakage power is modeled as a constant, and is dominated by the dynamic power. However, as the technology entering the deep sub-micron region, leakage power becomes more significant in the total amount of power consumption, and has distinct interdependency with temperature (i.e. leakage power can be approximated as a linear function of temperature and voltage [97]). This signifies the need for incorporating leakage/temperature dependency into the design and analysis of power efficiency systems.

#### Related Work On Power Aware Scheduling

Early research work on the problem of power aware multi-core scheduling is mainly focused on minimizing the dynamic power and its corresponding energy consumption (since dynamic power plays a dominant role over leakage power in the overall power consumption). By taking advantage of the convex relationship between the dynamic power and supply voltage, a number of methods (e.g. [76, 119]) were proposed to lower down the processor speed (i.e. supply voltage and working frequency) such that the power and/or energy consumption can be reduced meanwhile all tasks can be finished just before their "deadlines".

As the leakage power becomes more prominent, it is no longer optimal in the power/energy reduction by only considering the characteristics regarding the dynamic consumption. This is because the saved dynamic energy might be overweighed by the increased leakage part. Moreover, by taking leakage/temperature dependency into consideration, the power aware multi-core scheduling problem becomes even more complicated.

A great number of literature are published on solving the power aware multicore scheduling problems with consideration of leakage/power dependency [50, 52,

85, 129, 29, 125, 123, 90, 58, 126, 30, 118]. Based on different criteria, these existing

work can be classified into different categories. For example, based on the target

platforms, we have techniques proposed for 2-dimension multi-core platforms [50,

52], or 3-dimension multi-core platforms [85, 129]. Based on the task models, we have

tasks with stochastic [84] or deterministic workload [29, 125]. Based on the timing

requirement, we have soft real-time [123] or hard real-time scheduling [30, 118].

Based on the stages during which the scheduling decisions are made, we also have

on-line approaches [123, 90] and off-line approaches [58, 126].

#### 2.3.2 Thermal Aware Multi-Core Scheduling

After introducing the problem of power aware scheduling in the above section, now we introduce the problem of thermal aware multi-core scheduling. The aggressive semiconductor technology scaling has pushed the chip power density doubled every two to three years [92, 109], which immediately results in an exponential increasing in heat density. As introduced in Chapter 1, high temperature can degrade the performance of systems in various ways. Therefore, there is a great need of advanced techniques for thermal/temperature aware design of multi-core systems. In this subsection, we first introduce our research problem on thermal aware multi-core scheduling, then describe the thermal impact, and later discuss the related work.

#### Research Problem of Thermal Aware Scheduling

Thermal aware scheduling studies the scheduling problem in the system level with thermal/temperature awareness. Specifically, it studies the problem of how to develop effective and efficient scheduling algorithms such that the temperature requirement as well as the real-time requirement can be met, and at the same time other design metrics (i.e. peak temperature, throughput, energy consumption, etc.) can be optimized.

#### Thermal Modeling of Multi-Core Platforms

From the circuit-level aspect, the multi-core thermal model can be represented by an equivalent RC thermal circuit [105, 116]. Figure 2.2 shows an example of such thermal model on a dual-core platform. Basically, there are four abstraction layers in this RC-thermal model, namely die layer, thermal interface material(TIM) layer, heat spreader layer, and heat sink layer. Thermal nodes on the die layer are called active nodes, since they represent the actual processing cores of the system and consume non-zero power. In contrast, thermal nodes on the thermal package

Figure 2.2: Illustration for RC thermal circuit on a dual-core system [116]

(i.e. three cooling layers) are called inactive nodes, since their power dissipation is assumed to be zero regardless of the system processing modes.

Based on the circuit-level RC thermal model, the thermal phenomena of the entire chip can be formulated as

$$\mathbf{C}\frac{d\mathbf{T}(t)}{dt} + \mathbf{G}\mathbf{T}(t) = \mathbf{P}(t) \tag{2.1}$$

where **C**, **G**, **T** and **P** are thermal capacitance matrix, thermal conductance matrix, temperature vector and power vector, respectively. From the above equation, we can see that the higher the temperature is, the larger the power will be. Moreover, as mentioned in previous subsection, the power **P**, which is comprised of dynamic power and leakage power, also depends on temperature. Thus, we see there is an inter-dependency between power and temperature.

#### Related Work On Thermal Aware Scheduling

An increasing number of researches have been published on peak temperature minimization for thermal aware multi-core scheduling [70, 40, 41, 63, 124, 16, 101]. Chantem et al. [28] proposed an MILP-based solution to minimize the peak tem-

perature when executing a task graph. Lars et al. [104] proposed an approach to estimate the worst-case temperature for a core by searching for the worst case task/workload allocations among different cores. Ukhov et al. [116] presented a method to estimate the peak temperature by keeping track of temperature dynamics of a multi-core system until it reached the system steady state. Kumar et. al. [70] proposed a stop-n-go approach to reduce the peak temperature for task with data dependencies. They distributed the slack time between jobs such that the peak temperature could be minimized and there was no make-span violation.

There are many researchers studied the thermal aware multi-core scheduling from the aspect of throughput maximization [29, 58, 82, 52]. Chantem et al. [29] proposed a method to run real-time tasks by frequently switching between the two speeds which are neighboring to an ideal constant speed whose stable temperature was equal to the given peak temperature. Fisher et al. [40] presented a method to minimize the peak temperature in a homogeneous multi-core system by deriving an ideally preferred speed for each core in a global task scheduling environment. Huang et al. [58] proposed two approaches to maximize the throughput for a periodic real-time system under the given peak temperature constraint, one for processor with simple active and sleep mode and the other for more complicated processors with DVFS capabilities. Hanumaiah et al. [53] also focused on the problem of throughput maximization, and they addressed task-to-core allocation over migration intervals and voltage speed scaling within migration intervals as a separate problem and translated task-to-core allocation into a *MILP* formulation.

Many researchers have focused on the energy minimization problem for multicore scheduling with maximal temperature constraint [57, 118, 19, 51, 86]. Huang et al. [57] derived a closed-form energy calculation equation based on which they further proposed an energy minimization scheduling method for periodic task sets. In [118], Yang et al. presented a procedure to find the optimal pattern of schedule with the minimum energy consumption at the steady state. Hanumaiah et al. [51] formulated energy minimization as a quasi-concave optimization problem and employed DVFS, task migration and cooling methods to optimize the objective function on a multi-processor system. Liu et.al [86] developed a thermal-constrained energy optimization procedure to minimize system energy consumption under peak temperature constraint.

Recently, significant amount of work targeted on 3D architectures for thermal aware multi-core scheduling has been published [33, 129, 78, 85, 90, 115]. In [78], the authors proposed a scheduling algorithm to reduce peak temperature in a 3D multi-core system by dynamically rotating tasks among different cores. Liu et al. [85] proposed a 3D thermal aware job allocation technique to reduce the peak temperature, through which hot jobs were always assigned to the cores near heat sink such that the heat could be quickly dissipated. Zhu et al. [130] presented a run-time thermal management technique that exploited the heterogeneity of processing cores in a 3D system. Coskun et al. [33] proposed an adaptive approach to balance the temperature among all cores in a 3D architecture. They adopted a second order polynomial temperature/leakage dependency model and developed a thermal aware scheduling algorithm that made the partitioning decision based on a thermal history of each core and that of its neighboring cores.

## 2.4 Summary

In this chapter, we discussed the essential background of our research and introduced some closely related work. We first presented a general introduction of the basic concepts and critical techniques in real-time scheduling. Particularly, we introduced several different categorizations of real-time scheduling, and two important policies (e.g. RMS and EDF) in single-core scheduling. Next, we presented some preliminaries for multi-core scheduling, including categorizations from different perspectives, and several metrics used for evaluate the performance of multi-core scheduling. Then we discussed the multi-core scheduling problems with consideration of power/thermal awareness. We respectively introduced the research problems regarding to power and thermal, and discussed the related work.

In this dissertation, our goal is to develop effective scheduling methods for multicore real-time systems to satisfy timing and other constraints, and also to optimize various objectives (e.g. system utilization, power/energy, temperature and reliability). In the flowing four chapters, i.e. Chapters 3, 4, 5 and 6, we present our contributions. Then we conclude this dissertation in Chapter 7.

#### CHAPTER 3

# PARTITIONED MULTI-CORE SCHEDULING BY EXPLORING HARMONIC RELATIONSHIP AMONG REAL-TIME PERIODIC TASKS

We first present our research on classical real-time multi-core scheduling with timing as the only constraint. Specifically, in this chapter, we focus on partitioned scheduling for periodic real-time tasks on multi-core platforms under the *Rate Monotonic Scheduling (RMS)* policy. One common approach for partitioned multi-core scheduling problem is to transform this problem into a traditional bin-packing problem, with the utilization of a task being the "size" of the object and the utilization bound of a processor being the "capacity" of the bin. However, this approach ignores the fact that some implicit relations among tasks may significantly affect the feasibility of the tasks allocated to each local processor. To improve the system schedulability, we seek to exploit the fact that the utilization bound of a task set increases as task periods are closer to harmonic on single-core platforms. The challenge here, however, is how to take advantage of this fact on multi-core processor platforms while guarantee the schedulability of the real-time tasks.

#### 3.1 Related Work

In partitioned multi-core scheduling problem, the schedulability for tasks allocated on each processor can be determined based on feasibility conditions on single processors. To search for the optimal task partition for multiple processors is essentially a design space exploration problem, with complexity increasing rapidly with the size of the problem (e.g. the numbers of tasks or processors). How to quickly and accurately evaluate the schedulability of a design alternative (i.e. task partition) is key to the success of the partitioned multi-core scheduling problem. As a result, while there

exists exact timing analysis method for feasibility checking for tasks on a single core platform ([81, 71, 73]), they are not commonly for partitioned multi-core scheduling problem due to their large computational complexity. In stead, many other timing efficient feasibility checking methods, such as the utilization-bound based feasibility checking methods, are commonly used in the search for task partitions for multi-core scheduling problem.

#### 3.1.1 Different Utilization Bounds For Single-core Systems

A utilization bound  $f(\Gamma)$  for a task set  $\Gamma$  is a function of the parameters of  $\Gamma$ , and can be used to determine the schedulability of  $\Gamma$  under certain specific scheduling policy (e.g. RMS). By applying the parameters of  $\Gamma$  into  $f(\Gamma)$ , all tasks in  $\Gamma$  can be guaranteed to meet their deadlines if the task set utilization (denoted as  $U(\Gamma)$ ) is no more than that parametric utilization bound, i.e.  $U(\Gamma) \leq f(\Gamma)$ . Note that  $U(\Gamma)$  can be calculated by summing up the task utilizations of all tasks in  $U(\Gamma)$ , where a task utilization is the ratio of its execution time over its period.

For single-core systems, there are several utilization bounds proposed under RMS policy [26, 81, 71, 73, 48].

• *LLBound* [81]: The *LLBound* is a function with respect to the number of tasks, and is formulated as

$$LLBound(\Gamma) = N(2^{1/N} - 1), \tag{3.1}$$

where N is the number of tasks in the task set  $\Gamma$ . When N goes to infinity, the *LLBound* achieves its worst-case as 69%.

• KBound [71]: The KBound has a similar form as the LLBound, and is formulated as

$$KBound(\Gamma) = K(2^{1/K} - 1), \tag{3.2}$$

where K, instead of being the number of all tasks as that used by *LLBound*, is the minimum number of pseudo tasks (a pseudo task is a non-empty harmonic task set in which any two tasks are period dividable).

• RBound [73]: The RBound is proposed for tasks with special characteristics, i.e. the ratio between the maximum and minimum periods needs to be less than 2. The RBound takes not only the number of tasks but also the relationship among periods into consideration.

$$RBound(\Gamma) = (N-1)(r^{1/N-1} - 1) + 2/r - 1 \tag{3.3}$$

where N is the number of tasks in the task set, and r is the ratio between the maximum and minimum periods and needs to satisfy  $1 \le r < 2$ .

• CBound [48]: The CBound is the utilization bound proposed for a special type of task sets, called "harmonic" task sets<sup>1</sup>, and can be formulated as.

$$CBound(\Gamma) = 1$$

(3.4)

where  $\Gamma$  is a harmonic task set.

Among all four utilization bounds shown in the above, it has been proved that for RMS-based single-core scheduling, the RBound and CBound higher than the other two (i.e. the LLBound and the KBound) [73, 48]. However, these two utilization bounds (RBound or CBound) have critical limitations. The RBound can only be applied when a given task set satisfies the period constraint (i.e.  $1 \le r < 2$ ), while the CBound can only be used directly to harmonic task sets. Hence, in order to use the RBound or CBound for checking the schedulability of an arbitrary task set, we need to first transform the task set appropriately such that it satisfies the required condition.

<sup>&</sup>lt;sup>1</sup>A harmonic task set is a task set in which any two tasks are period dividable.

For RBound, there are a few methods proposed to transform a task set to satisfy the condition of  $1 \le r < 2$ , such as [73, 66]. In particular, Lauzac et~al. [73] proposed a task set scaling method by scaling all tasks with respect to the maximum period. Specifically, given a task set  $\Gamma$ ,  $\forall \tau_i \in \Gamma$ , the period as well as the execution time of  $\tau_i$  was scaled by

$$\begin{cases}

C_i' = C_i \cdot 2^{\lfloor \log \frac{T_{max}}{T_i} \rfloor} \\

T_i' = T_i \cdot 2^{\lfloor \log \frac{T_{max}}{T_i} \rfloor}

\end{cases}$$

(3.5)

where  $T_{max}$  represents the maximum period among all tasks. Their method scaled all task periods with respect to, but no larger than  $T_{max}$ . They formally proved that as long as the scaled task set was feasible then the original task set was also feasible.

Kandhalu *et al.* [66] presented another method by scaling the task set with respect to the minimum period. Specifically, given a task set  $\Gamma$ ,  $\forall \tau_i \in \Gamma$ , the period and the execution time of  $\tau_i$  was scaled by

$$\begin{cases}

C_i' = C_i / \lfloor \frac{T_i}{T_{min}} \rfloor \\

T_i' = T_i / \lfloor \frac{T_i}{T_{min}} \rfloor

\end{cases}$$

(3.6)

where  $T_{min}$  is the minimum period among all tasks. This method scaled all task periods with respect to, but no smaller than  $T_{min}$ . However, this approach cannot always guarantee the schedulability of the original task set once the scaled task set is schedulable. For example, consider a task set  $\Gamma$  consisting of four tasks with execution time and periods as  $\{(3, 24), (32, 100), (40, 135)\}$  and (15, 140). According to the scaling method introduced in [66], we can transform the task set to a new task set  $\Gamma'$  as  $\{(3, 24), (8, 25), (8, 27), (3, 28)\}$ . It is not difficult to verify that the new task set  $\Gamma'$  is schedulable while the original task set  $\Gamma$  is not schedulable.

For *CBound*, there are also a few methods proposed to transform a task set to satisfy the harmonic condition. Han *et al.* [47, 48] proposed two methods, i.e. *Sr*

and DCT, to transform a task set into a harmonic one. Since both methods result in the same harmonic task set, we only introduce the DCT method (which has a complexity equal to  $N^2$ ) as below:

- Sort  $\Gamma$  by T with non-increasing order.

- For each  $\tau_i \in \Gamma$ , transform  $\Gamma$  to  $\Gamma'_i$  by

$$T'_{j} = \begin{cases} T'_{j+1}/(\lfloor T'_{j+1}/T_{j} \rfloor), & \text{if } j < i \\ T_{j}, & \text{if } j = i \\ T'_{j-1} \cdot \lfloor T_{j}/T'_{j-1} \rfloor, & \text{if } j > i \end{cases}$$

(3.7)

• Find the optimal primary harmonic task  $\Gamma'$  that minimizes the total task set utilization among all  $\Gamma_i$  where i=1,2,...,N. In other word,  $U(\Gamma')=\min_{i=1}^N U(\Gamma'_i)$ .

The *RBound* and *CBound* indicate that on a single-core processor, the system utilization as well as the task set schedulability, can be greatly improved if the relationship between task periods can be appropriately exploited.

Existing work (i.e. [73, 66, 47, 48]) has shown that, with appropriate task transformation, using *RBound* and *CBound* can significantly improve the schedulability checking accuracy.

## 3.1.2 Partitioned Scheduling