## Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-26-2013

# Leakage Temperature Dependency Aware Real-Time Scheduling for Power and Thermal Optimization

Vivek Chaturvedi Florida International University, vchaturv@fiu.edu

DOI: 10.25148/etd.FI13042337

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Chaturvedi, Vivek, "Leakage Temperature Dependency Aware Real-Time Scheduling for Power and Thermal Optimization" (2013). *FIU Electronic Theses and Dissertations*. 870. https://digitalcommons.fiu.edu/etd/870

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## LEAKAGE TEMPERATURE DEPENDENCY AWARE REAL-TIME SCHEDULING FOR POWER AND THERMAL OPTIMIZATION

A dissertation submitted in partial fulfillment of the

requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

ELECTRICAL ENGINEERING

by

Vivek Chaturvedi

2013

To: Dean Amir Mirmiran College of Engineering and Computing

This dissertation, written by Vivek Chaturvedi, and entitled Leakage Temperature Dependency Aware Real-Time Scheduling for Power and Thermal Optimization, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Raju Rangaswami

Jean H. Andrian

Cheng-Xian Lin

Nezih Pala

Gang Quan, Major Professor

Date of Defense: March 26, 2013

The dissertation of Vivek Chaturvedi is approved.

Dean Amir Mirmiran College of Engineering and Computing

> Dean Lakshmi N. Reddi University Graduate School

Florida Internatinal University, 2013

© Copyright 2013 Vivek Chaturvedi.

All Rights Reserved.

#### DEDICATION

I would like to dedicate this Doctoral dissertation to my dearest mother Mrs. Sharda Chaturvedi and loving father Late Mr. J.P. Chaturvedi. Without their love, understanding, support, and encouragement, the completion of this endeavor would never have been possible.

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank God Almighty for giving me the strength and patience to accomplish my dream of getting a Ph.D degree.

Next, I would like to express my deepest gratitude to my advisor Dr. Gang Quan. I feel fortunate and blessed to have an advisor like Dr. Quan, who gave me constant guidance, personal attention, suggestions and endless encouragement during the last four years of my doctoral study. I truly admire his perseverance, depth of knowledge and strong dedication to students and quality research. Dr. Quan's thoughts and suggestions have not only helped me to complete this dissertation successfully, but have also helped me to overcome several personal problems. I am thankful to him for his patience and support.

I also want to take this opportunity to thank Dr. Quan's family for being warm and welcoming.

I am very grateful to my Ph.D. committee members: Dr. Jean H. Andrian, Dr. Nezih Pala, Dr. Cheng-Xian Lin and Dr. Raju Rangaswami for their thoughtful insights and suggestions in improving my dissertation. I am extremely proud to have such a wonderful and knowledgeable people serving on my dissertation committee.

I want to give my heartfelt thanks to Dr. Adrian Nunez-Aldana, Dr. Nazanin Mansouri, Dr. Shangping Ren and Mr. Soroush Shakib for their endless encouragement and support in accomplishing my career objectives.

I am thankful to the staff of ECE department at FIU, specially to Mrs. Maria Benincasa, Mrs. Pat Brammer and Mrs. Ana Saenz for their great commitment to student services.

Next, I would like to thank my lab mates at ARCS lab for creating a wonderfully collaborative and enriching work environment filled with fun and laughter. I am confident that our friendship and cooperation will go a long way. God blessed me with some wonderful friends, who are my solid support system. I am very thankful to them for providing me with unconditional love, support and care. I greatly value your friendship and I deeply appreciate your faith in me.

Finally, and above all, I want to thank my family for their unlimited love, faith, encouragement, blessings and prayers. My life-long gratitude go to my dearest mother Mrs. Sharda Chaturvedi and my loving father late Mr. J.P. Chaturvedi for all the love and affection they have showered upon their children. My parents are my true inspiration. I want to thank my brother Mr. Rajeev Chaturvedi and sister Mrs. Mamta Tripathi for being a great wall of support and motivation in my life. I am thankful to my brother-in-law Mr. Satish Tripathi and sister-in law Mrs. Megha Chaturvedi for their care and encouragement. Lastly, I want to express my deepest love for my nieces Vilina and Manavi for filling my life with their angelic presence.

## ABSTRACT OF THE DISSERTATION LEAKAGE TEMPERATURE DEPENDENCY AWARE REAL-TIME SCHEDULING FOR POWER AND THERMAL OPTIMIZATION

Vivek Chaturvedi

Florida International University, 2013

Miami, Florida

Professor Gang Quan, Major Professor

Catering to society's demand for high performance computing, billions of transistors are now integrated on IC chips to deliver unprecedented performances. With increasing transistor density, the power consumption/density is growing exponentially. The increasing power consumption directly translates to the high chip temperature, which not only raises the packaging/cooling costs, but also degrades the performance/reliability and life span of the computing systems. Moreover, high chip temperature also greatly increases the leakage power consumption, which is becoming more and more significant with the continuous scaling of the transistor size. As the semiconductor industry continues to evolve, power and thermal challenges have become the most critical challenges in the design of new generations of computing systems.

In this dissertation, we addressed the power/thermal issues from the system-level perspective. Specifically, we sought to employ real-time scheduling methods to optimize the power/thermal efficiency of the real-time computing systems, with leak-age/temperature dependency taken into consideration. In our research, we first explored the fundamental principles on how to employ dynamic voltage scaling (DVS) techniques to reduce the peak operating temperature when running a real-time application on a single core platform. We further proposed a novel real-time scheduling method, "M-Oscillations" to reduce the peak temperature when scheduling a hard

real-time periodic task set. We also developed three checking methods to guarantee the feasibility of a periodic real-time schedule under peak temperature constraint. We further extended our research from single core platform to multi-core platform. We investigated the energy estimation problem on the multi-core platforms and developed a light weight and accurate method to calculate the energy consumption for a given voltage schedule on a multi-core platform. Finally, we concluded the dissertation with elaborated discussions of future extensions of our research.

## TABLE OF CONTENTS

| CI | CHAPTER PAG                                                                                                                                                                                        |                                                                       |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1  | Introduction1.1Semiconductor Industry and Moore's Law1.2The Rising Power Consumption and Its Challenges1.3The Temperature Issues1.4Research Goal and Contributions1.5Structure of the Dissertation | 4<br>5<br>9                                                           |

| 2  | <ul> <li>Background and Related Work</li> <li>2.1 Real-Time Systems and Computing</li></ul>                                                                                                        | 13<br>14<br>16<br>20<br>24<br>27<br>27<br>kage 28<br>29<br>tive<br>30 |

| 3  | <ul> <li>2.5 Conclusions</li></ul>                                                                                                                                                                 | em-<br>33<br>34<br>36<br>36<br>36<br>37<br>38<br>39<br>47<br>54       |

| 4  | <ul> <li>M-Oscillations : A Scheduling Technique for Peak Temperature Minimiz</li> <li>4.1 Related Work</li></ul>                                                                                  | 62<br>64                                                              |

|      | 4.4  | Experiments and Results                                              | 73       |

|------|------|----------------------------------------------------------------------|----------|

|      |      | 4.4.1 Performance Evaluation                                         | 73       |

|      | 45   | 4.4.2 Performance Evaluation on a Practical Simulation Platform .    | 76<br>81 |

|      | 4.5  | Summary                                                              | 81       |

| 5    | Feas | sibility Analysis for Temperature-Constraint Hard Real-Time Periodic |          |

|      | Tasl | άS                                                                   | 83       |

|      | 5.1  | Related Work                                                         | 84       |

|      | 5.2  | Preliminary                                                          | 86       |

|      | 5.3  | The Leakage Oblivious Feasibility Analysis                           | 89       |

|      | 5.4  | The Leakage Conscious Feasibility Analysis                           | 92       |

|      |      | 5.4.1 Simplifying the leakage/temperature dependency                 | 93       |

|      |      | 5.4.2 Checking the Temperature at the End of First Hyperperiod .     | 94       |

|      |      | 5.4.3 Checking the Temperature Safe Modes                            | 95       |

|      |      | 5.4.4 The Necessary and Sufficient Condition                         | 98       |

|      |      | 5.4.5 Further Discussions                                            | 103      |

|      | 5.5  | Experiment                                                           | 105      |

|      |      | 5.5.1 Leakage Model Validation                                       | 105      |

|      |      | 5.5.2 The Performance of Feasibility Conditions                      | 108      |

|      |      | 5.5.3 The Impacts of Different Leakage Models                        | 113      |

|      | 5.6  | Conclusion                                                           | 114      |

| 0    | F    |                                                                      | 110      |

| 6    |      | rgy Minimization in Multi-Core Processor Systems                     | 116      |

|      | 6.1  | Related Work                                                         | 117      |

|      | 6.2  | Preliminary                                                          | 119      |

|      |      | 6.2.1 Processor and Task Model                                       | 119      |

|      |      | 6.2.2 Power Model                                                    | 120      |

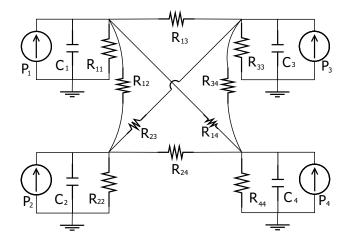

|      | 0.0  | 6.2.3 Thermal Model                                                  | 121      |

|      | 6.3  | Energy Formulation for Multi-Core Systems                            | 122      |

|      | 6.4  | Experimental validation                                              | 126      |

|      |      | 6.4.1 Experimental Set-Up                                            | 126      |

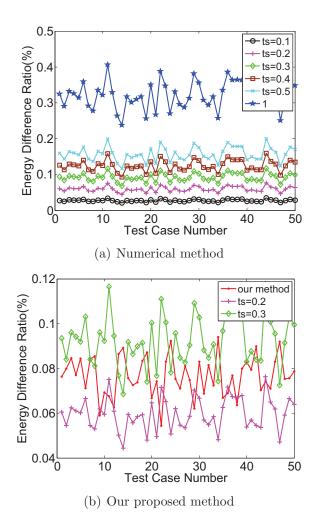

|      |      | 6.4.2 Accuracy Analysis                                              | 127      |

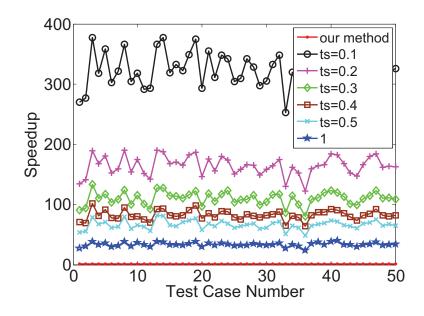

|      |      | 6.4.3 Time Efficiency Analysis                                       | 130      |

|      | 6.5  | Energy-Minimization Scheduling Methods                               | 131      |

|      | 6.6  | Conclusions                                                          | 135      |

| 7    | Con  | clusions and Future Works                                            | 136      |

|      | 7.1  | Summary                                                              | 136      |

|      | 7.2  | Future Work                                                          | 138      |

|      | BEF  | FERENCES                                                             | 145      |

|      | TUL  |                                                                      | 140      |

| VITA |      |                                                                      | 157      |

### LIST OF FIGURES

| FIGURE     | PA                                                                                                                                                             | GE |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

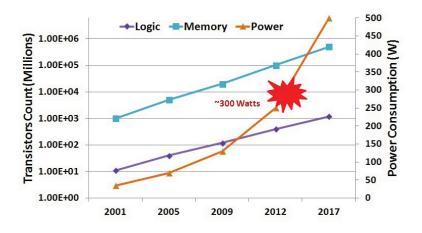

| Figure 1.1 | Trend Predicting Transistor Counts and Uncontrolled Power<br>Consumption [24]                                                                                  | 3  |

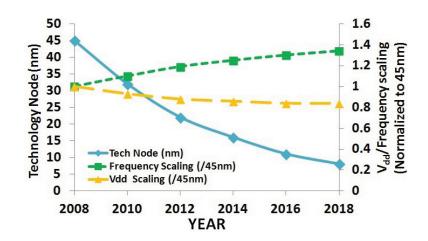

| Figure 1.2 | Technology Scaling Trends [24]                                                                                                                                 | 3  |

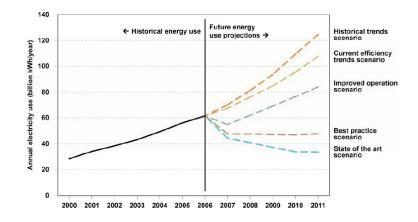

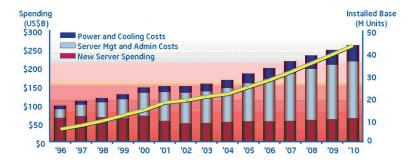

| Figure 1.3 | Projected Electricity in Data centers [7]                                                                                                                      | 5  |

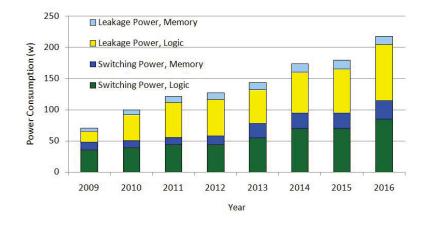

| Figure 1.4 | Power Consumption Trend [65]                                                                                                                                   | 8  |

| Figure 1.5 | Projected Electricity in Data centers [7]                                                                                                                      | 8  |

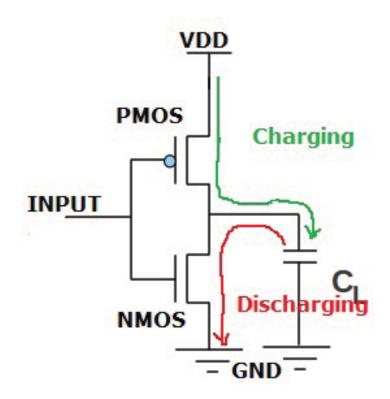

| Figure 2.1 | A CMOS Inverter Circuit [95]                                                                                                                                   | 17 |

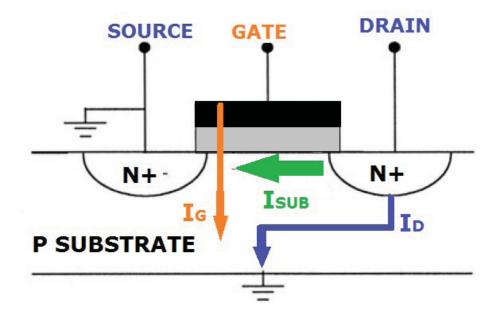

| Figure 2.2 | Types of Leakage Current in MOS [95]                                                                                                                           | 19 |

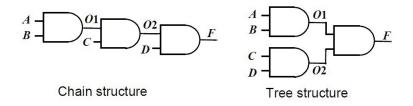

| Figure 2.3 | A Logic Restructuring Example [95]                                                                                                                             | 22 |

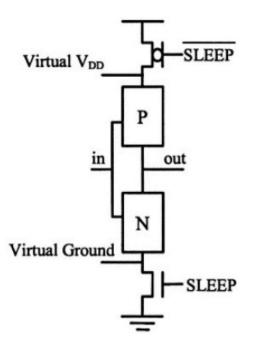

| Figure 2.4 | Power Gating Circuit [95]                                                                                                                                      | 23 |

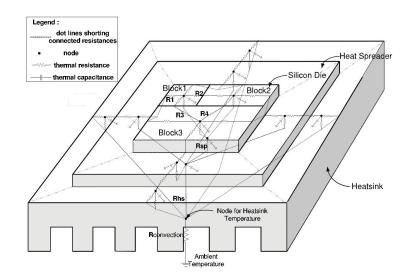

| Figure 2.5 | Using RC Network to Model a Processor's Heat Transfer [119]                                                                                                    | 25 |

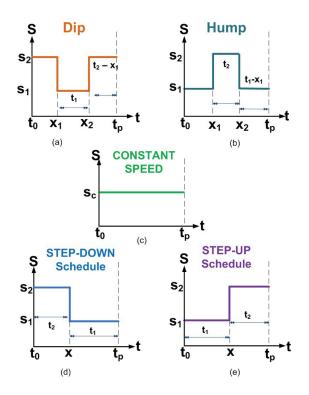

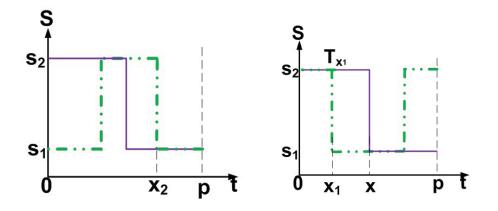

| Figure 3.1 | Different Speed Schedules: (a) The Dip Schedule; (b) The<br>Hump Schedule; (c) The Constant Schedule; (d) The Step-<br>Down Schedule; (e) The Step-Up Schedule | 40 |

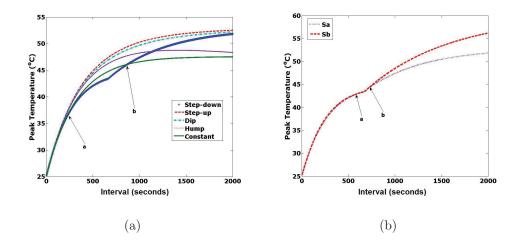

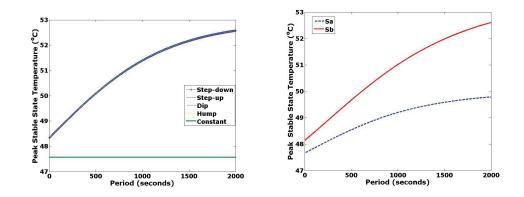

| Figure 3.2 | The Peak Temperatures by Different Schedules Within a Given Interval                                                                                           | 41 |

| Figure 3.3 | Peak Temperatures at the Stable Status by Different Schedules                                                                                                  | 44 |

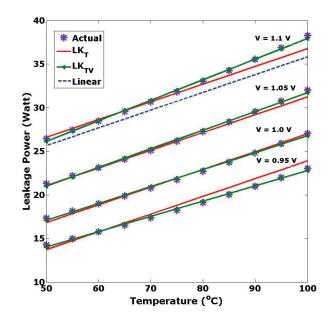

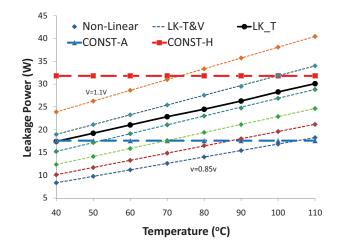

| Figure 3.4 | Leakage Power Consumptions Calculated using Different Leak-<br>age Models under Different Temperatures and Supply Voltages                                     | 46 |

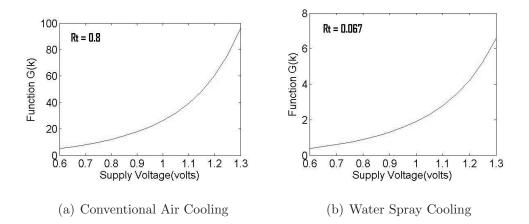

| Figure 3.5 | Peak Temperature                                                                                                                                               | 50 |

| Figure 3.6 | Peak Temperature                                                                                                                                               | 52 |

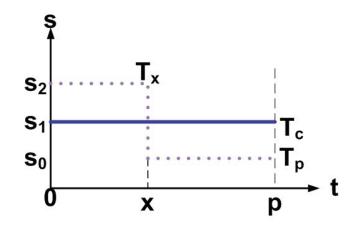

| Figure 3.7  | The Constant-Speed Schedule and a Step-Down Schedule within a Given Interval                                                                                                                                         | 53 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

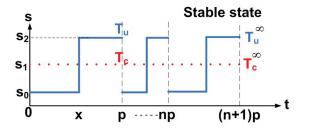

| Figure 3.8  | Stable Temperature for Step-Down and Step-Up Schedule                                                                                                                                                                | 57 |

| Figure 3.9  | Stable Temperature for Step-Up and Constant-Speed Schedule                                                                                                                                                           | 57 |

| Figure 3.10 | Step-Up Schedules $\hat{S}_2(s_2, s_3)$ and $\hat{S}_3(s_2, s_4)$ for a Real-Time Periodic Task.                                                                                                                     | 60 |

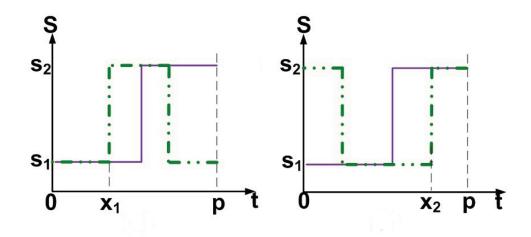

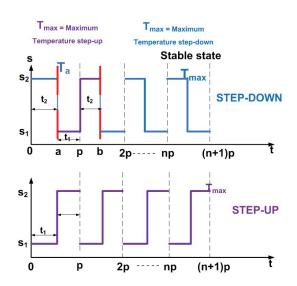

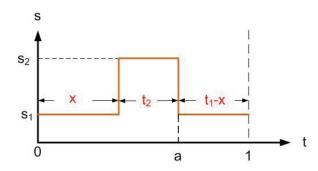

| Figure 4.1  | A Two-Speed Schedule that Uses Speed $s_1$ for $t_1$ Time Units<br>and Speed $s_2$ for $t_2$ Time Units. $t_1 + t_2 = 1$                                                                                             | 67 |

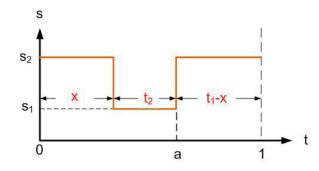

| Figure 4.2  | A Two-Speed Schedule that Uses Speed $s_2$ for $t_1$ Time Units<br>and Speed $s_1$ for $t_2$ Time Units. $t_1 + t_2 = 1$                                                                                             | 68 |

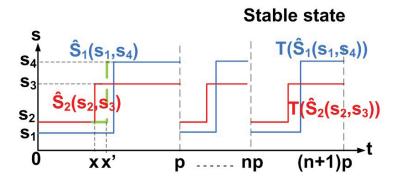

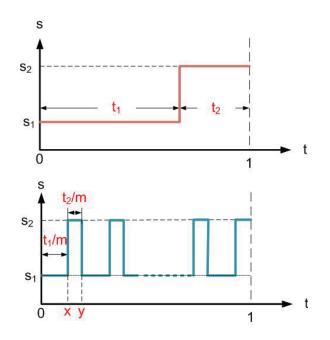

| Figure 4.3  | A Two-Speed Schedule and Its Corresponding <i>M-Oscillations</i> Schedule.                                                                                                                                           | 70 |

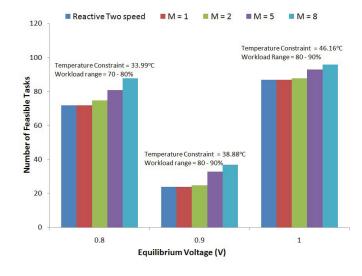

| Figure 4.4  | Feasibility Comparison Between the <i>M</i> -Oscillations Scheme<br>and the Reactive Two-Speed Scheme under Different Maxi-<br>mum Temperature Constraints                                                           | 74 |

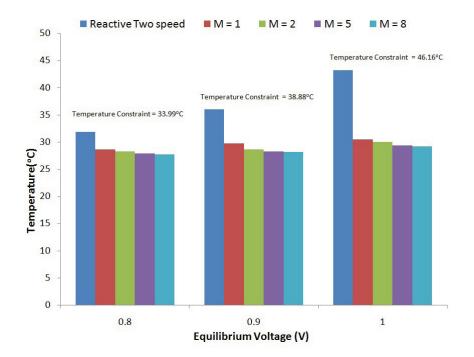

| Figure 4.5  | Average Maximum Temperature Comparison Between the $M\!\!-\!Oscillations$ Scheme and the Reactive Two-Speed Scheme $$ .                                                                                              | 76 |

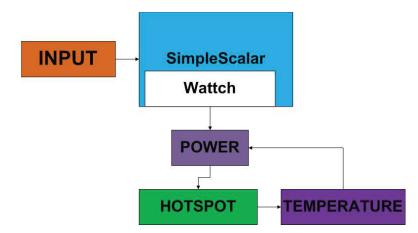

| Figure 4.6  | Conceptual Flow Diagram of the Simulator Platform Set-Up                                                                                                                                                             | 78 |

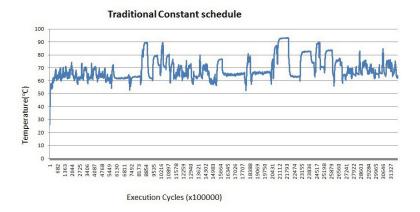

| Figure 4.7  | Temperature Pattern Running a Traditional Constant Speed         Schedule                                                                                                                                            | 79 |

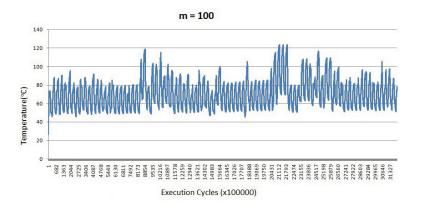

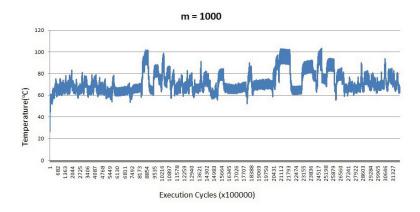

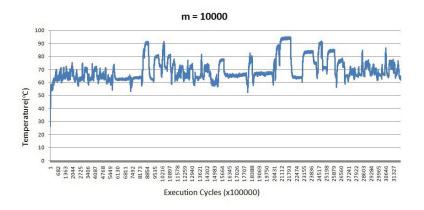

| Figure 4.8  | Temperature Pattern Running a $M$ -Oscillations with $m = 100$                                                                                                                                                       | 80 |

| Figure 4.9  | Temperature Pattern Running a $M$ -Oscillations with $m = 1000$                                                                                                                                                      | 80 |

| Figure 4.10 | Temperature Pattern Running a $M$ -Oscillations with $m = 10000$                                                                                                                                                     | 80 |

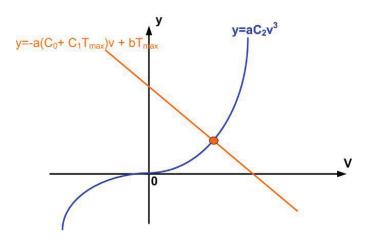

| Figure 5.1  | Since the slope for the linear function $y = -a((C_0 + C_1 T_{max})) \cdot v + bT_{max}$ is less than zero, there is only one cross point for function $y = -a((C_0 + C_1 T_{max})) \cdot V + bT_{max}$ and function |    |

$y = aC_2V^3$ . So Equation 5.27 has only one *real* root. [104] . 97

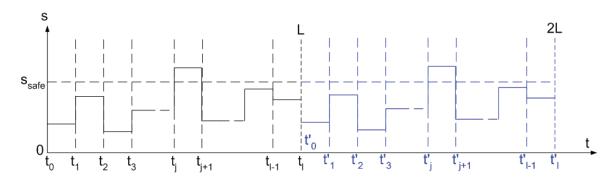

| Figure 5.2 | A speed schedule within 2 hyperperiods                                                                                                   | 98  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

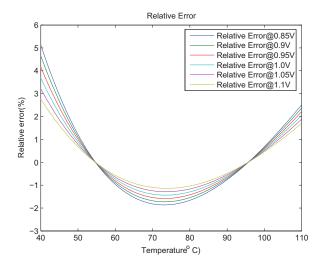

| Figure 5.3 | The Leakage Power Consumptions Based on Different Leakage Models                                                                         | 107 |

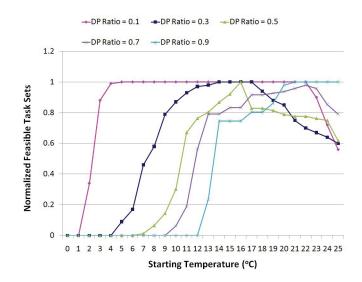

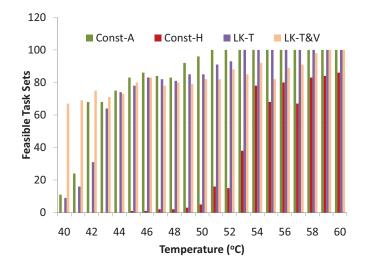

| Figure 5.4 | Success Rate Under Different Maximal Temperature (deadline-<br>period ratio = $0.3$ )                                                    | 110 |

| Figure 5.5 | Success Rate Under Different Deadline-Period Ratio. $(T_{max} = 50^{\circ}C)$                                                            | 110 |

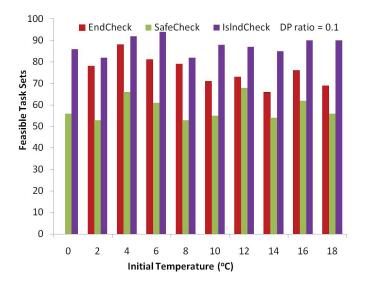

| Figure 5.6 | Success Rate Under Different Initial Temperature(above ambient temperature). $(T_{max} = 50^{\circ}C$ and deadline-period ratio $= 0.1)$ | 111 |

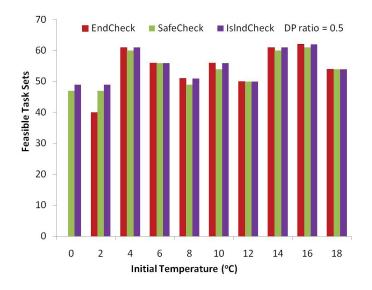

| Figure 5.7 | Success Rate Under Different Initial Temperature(above ambient temperature). $(T_{max} = 50^{\circ}C$ and deadline-period ratio $= 0.5)$ | 112 |

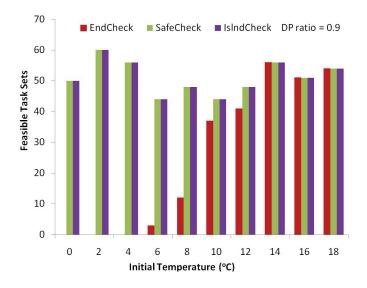

| Figure 5.8 | Success Rate Under Different Initial Temperature(above ambient temperature). $(T_{max} = 50^{\circ}C$ and deadline-period ratio $= 0.9)$ | 113 |

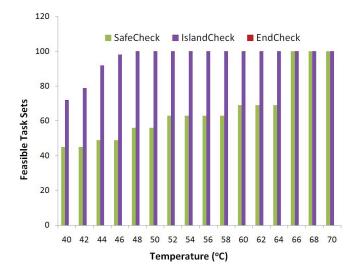

| Figure 5.9 | Feasible Task Sets Based on Different Leakage Models Under Different Temperature (deadline-period ratio=0.3)                             | 115 |

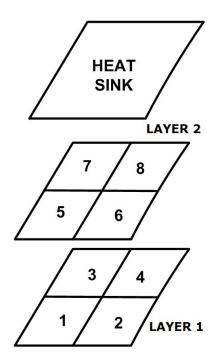

| Figure 6.1 | Illustration for thermal phenomena on multi-core system $\ . \ .$                                                                        | 121 |

| Figure 6.2 | Experimental Parameters                                                                                                                  | 126 |

| Figure 6.3 | Accuracy Analysis, Compared with the Numerical Method Under $t_s = 0.01$                                                                 | 128 |

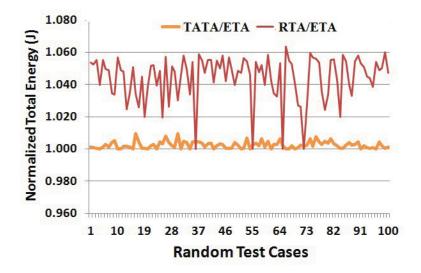

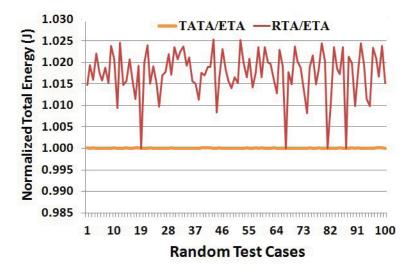

| Figure 6.4 | Time Efficiency Analysis, Normalized with Our Method                                                                                     | 130 |

| Figure 6.5 | Thermal Aware Task Allocation on 3X3 Platform                                                                                            | 131 |

| Figure 6.6 | Normalized System Energy (J) on 3x3 Multi-Core Platform $% \mathcal{A}$ .                                                                | 133 |

| Figure 6.7 | Normalized System Energy (J) on 2x3 Multi-Core Platform $% \mathcal{A}$ .                                                                | 133 |

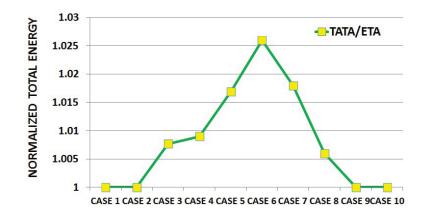

| Figure 6.8 | ETA- $EM$ vs $TATA$ - $EM$ on 3x3 Multi-Core Platform                                                                                    | 134 |

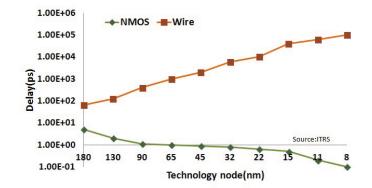

| Figure 7.1 | source [65]                                                  | 139 |

|------------|--------------------------------------------------------------|-----|

| Figure 7.2 | A 3D Stacked Multi-core Architecture                         | 142 |

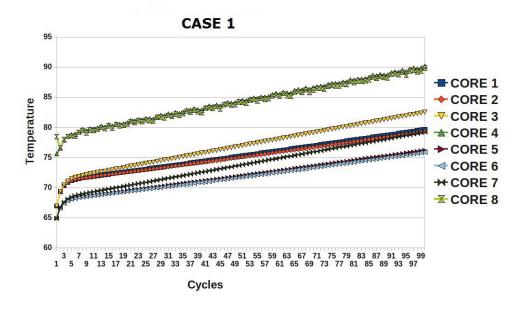

| Figure 7.3 | Peak Temperature Dynamics on each Core, CASE 1 $\ . \ . \ .$ | 143 |

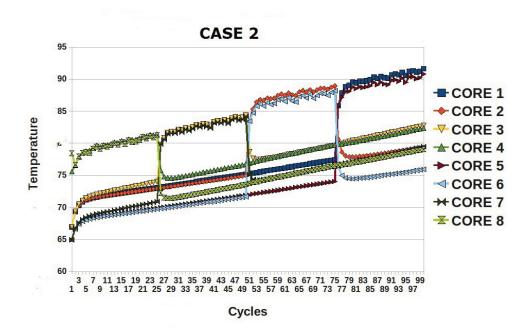

| Figure 7.4 | Peak Temperature Dynamics on each Core, CASE 2 $\ . \ . \ .$ | 144 |

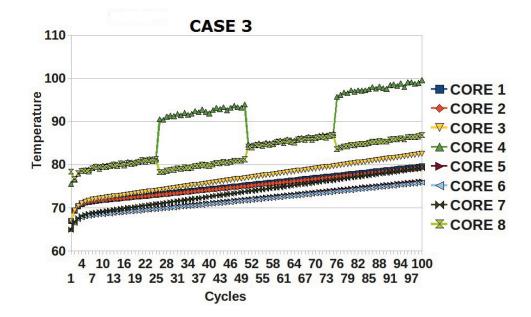

| Figure 7.5 | Peak Temperature Dynamics on each Core, CASE 3               | 144 |

## LIST OF TABLES

| TABLE     | PAGE                                                           | £ |

|-----------|----------------------------------------------------------------|---|

| Table 2.1 | Duality Between Thermal and Electrical Quantities 24           | 1 |

| Table 4.1 | Equilibrium Speeds & Corresponding Maximum Temperatures 74     | 1 |

| Table 4.2 | The Different Supply Levels and Corresponding Frequencies . 77 | 7 |

| Table 5.1 | Processor parameters and constants for Model $LK_{T\&V}$ 107   | 7 |

| Table 7.1 | HotSpot Parameters and Floorplan 142                           | 1 |

#### CHAPTER 1

#### Introduction

In merely past two decades, microprocessor performance has grown 1000-fold delivering unprecedented computing capabilities [24]. The advancement in microprocessor performance has largely be driven by the continuous scaling of the transistor feature size that facilitates exponential transistor integration capacity (doubling every 2 years, Moore's law). However, with increasing transistor density, the power density in the microprocessors has also grown exponentially, doubling every three years [118, 22]. Moreover, the exponentially increasing power consumption results in a dramatic increase in the chip operating temperature [118].

The exponential increase in the power consumption and the soaring chip temperature creates enormous challenges put hurdles not only to the design of the future computing systems but also to the associated economic (low cost computing) and green computing (environment protection) goals. New power/thermal aware methodologies and techniques to combat the power/thermal issues becomes essential. In this chapter, we first present the overview on the current technology trends, emphasizing on the motivation behind our research work. Next, we define our research problem and our contributions. Finally, we present the structure of this dissertation.

#### 1.1 Semiconductor Industry and Moore's Law

The semiconductor industry has shown an evolutionary expansion in terms of sophisticated computing technologies and economic growth. Today, its a \$2 trillion industry in US, impacting socioeconomic growth of human population around the world [88]. The remarkable growth of electronic systems has largely driven by so called "Moore's law" [91]. According to Moore's law, the number of transistors integrated on a single chip will double approximately every 18 months [91, 88, 46], delivering exponentially improved performance in new generations of computing systems. Moore's prediction of exponential increase in transistor density with every generation will continue to be so, atleast in the near future [88]. The attainment of integration density objective has been catalyzed by the foundation of transistor scaling laid by Dennard et al. in 1974 [43, 24]. For the past 50 years, with other technological advances (e.g. fabrication, architecture, micro-architecture, testing etc.), Moore's law coupled with transistor size scaling has resulted in consistent exponential performance gains [46].

Transistor scaling would not cause power consumption problem if the supply voltage could be scaled down accordingly. The idealistic theory of transistor size scaling rules that with every generation transistor dimensions should be reduced by 30% (0.7X) keeping electric fields constant, shrinking area by 50%, doubling transistor density and increasing performance by 40% (0.7X delay reduction, or 1.4X frequency increase). The electric field is kept constant by reducing supply voltage by 30% resulting in 50% power reduction per transistor [43, 24]. However, with the transistor design paradigm shifting to the deep sub-micron domain (DSM), the idealistic scaling theory ceases to hold valid anymore. Though the density of transistors' continues to increase exponentially for performance gains, the slow scaling of the supply voltage due to stringent threshold voltage constraint has resulted in the exponential increase in the power density of microprocessor systems.

As an example, in Figure 1.2, we can see the projected exponential scaling of the feature size from 45nm to 8nm during the course of 8 years. The frequency and supply voltage scaling  $(V_{dd})$  on the other hand is expected to scale with slower pace in the future, particularly  $V_{dd}$  scaling getting flat after 2014 (node < 20nm) [24, 46]. As a result, the power consumption has been increasingly exponentially with transistor density as illustrated in Figure 1.1.

Figure 1.1: Trend Predicting Transistor Counts and Uncontrolled Power Consumption [24]

Figure 1.2: Technology Scaling Trends [24]

#### **1.2** The Rising Power Consumption and Its Challenges

The tremendous increase in the transistor integration density has contributed to an exponential increase in power demands. As depicted in Figure 1.1, on a  $300mm^2$  die, more than 100 billion transistors (logics + memory) are integrated today, seeking tremenodus power consumption demands (300 watts) in the near future [23]. The exponential increase of the power consumption brings two significant challenges in front of the designers of the electronic systems: (1) how to provide the enough supply, and (2) how to deal with the heat dissipated by the systems. These issues are critical for both battery-operated portable devices and high performance power-rich systems.

For the first challenge, computation devices with limited power sources have stringent constraints on power consumption. Recently times, there has been a tremendous shift in the market for personal computing, with a rapid and widespread demand for highly sophisticated portable/mobile devices like laptops, mobile phones, music players etc. For example, every four in ten Americans owns a portable MP3 player [116, 1] and mobile phones are the fastest growing electronic product ever [116, 45]. Portability in these devices put essential restrictions on the size, weight and power. Power is particulary important, as these portable devices largely depend upon the battery-life to deliver high performance. As the computation complexity is growing with a rapid rate demanding higher power/energy supply, the much slower growth in battery capacity (3 - 7%/year) poses a critical limitation in front of the designers [107, 118]. As the mobile devices are growing pervasive, energy efficiency is a critical design metric for these these energy-constrained architectures [116, 141].

Power consumption has also become increasingly critical for power-rich platforms such as data centers. Data centers and server systems play an important role in today's cyber infrastructure. Government organizations, hospitals, share markets, IT companies etc., all depend upon data centers for their daily business activities.

Figure 1.3: Projected Electricity in Data centers [7]

Data center power consumption accounts for 1.5 - 2% of the total electricity usage in the USA, costing nearly \$4.5 billion [7]. The U.S. Environmental Protection Agency (EPA) predicts that energy consumption in data centers will exceed 100 billion kWh in 2011 [7](depicted in Figure 1.3), causing the federal governments electricity cost for servers and data centers to be nearly \$740 million annually by 2011. Evidently, the need for power/energy efficient methods are of critical importance in contemporary and futuristic computing environment.

#### **1.3** The Temperature Issues

A significant part of the power consumption consumed by the system is converted to heat. Therefore, the exponentially increasing power consumption results in the dramatic increase in chip temperature. Managing temperature in advanced microprocessors has become a severe challenge for computing system architects and designers.

The escalating heat has directly led to high cooling/packaging costs in microprocessors (1-3 dollar/watt [119]). With more compact devices and non-uniform heat distribution (hotspots) on the chips' surface, traditional air-cooling methods have become inadequate [98]. New cooling solutions like liquid cooling, micro-channel cooling etc [120, 110] are studied for cost-effective heat removal. The severity of thermal problems is highlighted by Intel's acknowledgement of hitting a "thermal wall" [90]. When studying the temperature management in data centers, the numbers are striking. As shown in Figure 1.5, the cooling cost in data centers has grown 400% in the last 10 years, and this is expected to rise with the same rate in the future. Moreover, it is also reported that for 1 watt of computing, half to one watt has to be consumed just for cooling [18, 25]. The expensive cooling methods in data centers are now a serious threat to economic problems, leading to the "economic meltdown of Moore's Law" [25].

High chip temperature not only increases the cooling/packaging costs, but also adversely affects the life-span and reliability of a device. The increase in chip temperature increases the rate of life-time fault processes, like electromigration, timedependent dielectric breakdown, stress migration and thermal cycling [21, 20, 142]. Though there are several formulations of different type of fault processes, in general reliability can be modeled by using the Arrhenius equation [61, 136, 21], i.e.  $MTF = MTF_0 e^{\frac{E_0}{K_b T}}$ , where MTF is the mean-time-to-failure of a system, and Tis the operating temperature. From this equation we can see that a device's meantime-to-failure decreases exponentially with increasing operating temperature. Based on this, Yeh et.al [135] observed that a 10°C rise in the temperature can result in 50% reduction of the system life span. Moreover, rising temperature has a negative impact on system reliability. For instance each 15°C rise in the temperature can add approximately 10 -15% circuit delay [111]. This causes various timing anomalies and spurious transitions in digital systems.

High temperature also increases leakage power consumption substantially. With continuous scaling of semiconductor technology, the transistor device size has already entered the deep sub-micron era (feature size < 90nm). As transistor size becomes smaller and smaller, the temperature leakage dependency becomes stronger and stronger. High temperature increases the leakage power consumption, which further contributes to the overall power consumption. This positive feedback loop between the overall power consumption and the temperature is a serious threat to design of modern computing systems. This is particularly true as the leakage power consumption has now become a significant contributor to the overall power consumption of the system. As shown in Figure 1.4, the leakage power consumption will increase dramatically in the near future. It is catching up and even surpassing the dynamic power consumption [65]. It is shown by Liao et al. [77] that when changing the temperature from  $65^{\circ}C$  to  $110^{\circ}C$ , the leakage power can increase as much as 38% for processors using the 65nm technology. Moreover, a  $10^{\circ}C$  rise in temperature above  $35^{\circ}C$  can result in an increase of 126% in the leakage current [111].

Furthermore, driven by the performance demands and energy constraints, processor architectures are evolving from 2D integration to 3D stacked integrated chips. In 3D designs multiple 2D chips are stacked vertically to achieve higher performance and energy efficiency due to reduced interconnects' lengths [19, 86]. However, in 3D stacked chips, the impact of increased temperature grows many folds due to strong thermal relation between vertically aligned neighbors. This strong thermal correlation elevates the thermal issues by creating more hot spots [147]. Particularly, as increasing temperature has strong relation with leakage power and reliability, it is shown that 30% variation in process parameters can result up to 20X increased leakage power [28].

From the above discussion, it is evident that there is an urgent need to develop new and efficient methodologies to address power/thermal issues in computing systems. In the next section, we present the problem which we address in this dissertation, followed by a brief description of our contributions.

Figure 1.4: Power Consumption Trend [65]

Figure 1.5: Projected Electricity in Data centers [7]

#### **1.4** Research Goal and Contributions

The power/thermal challenges have grown critical and imposed severe threats to the realization of new generations of computing systems. The severity of the challenges requires development of new power/thermal aware design solutions at every design abstraction level, i.e. architecture, system, logic, circuit, device etc. In this dissertation, we address these issues from the system-level perspective. We want to study the real-time scheduling techniques coupled with resource management capabilities available in modern processors to optimize the power and the thermal efficiency of the real-time computing systems.

Through our research, we have developed several solutions to address the power/thermal issues, which are summarized as following:

- 1. We first explored fundamental principles on how to employ dynamic voltage scaling (DVS) to reduce the peak operating temperature. We find that, for a specific interval, a real-time schedule using the lowest constant speed is not necessarily the optimal choice any more in minimizing the peak temperature. We identify the scenarios when a schedule using two different speeds can outperform the one using the lowest constant speed. In addition, we find that, when scheduling a periodic task set, the constant speed schedule is still the optimal solution for minimizing the peak temperature when the temperature is at its stable status. We formulate our conclusions into several theorems with formal proofs.

- 2. Next, we studied the problem on how to minimize the peak temperature of a processor when executing a periodic task set. In our research, we developed a novel real-time scheduling method, "*M-Oscillations*" that can reduce the peak temperature when scheduling a hard real-time periodic tasks set. We formally proved the correctness of the proposed algorithm based on a processor model

that can effectively account for the leakage/temperature relationship. The proposed *M-Oscillations* scheduling method can reduce peak-temperature of the system up to  $14^{\circ}C$ , improving feasibility of given tasks set by maximum 20%.

- 3. We also studied feasibility checking problem for real-time periodic task sets under the peak temperature constraint. We showed that the traditional scheduling approach, i.e. to repeat the schedule that is feasible through the range of one hyper-period, does not apply any more. We then developed new necessary and sufficient conditions to check the feasibility of real-time schedules.

- 4. We further extended our research from single-core processor to a multi-core platform. Different from the traditional numerical approach, we developed an analytical method to calculate the overall energy consumption rapidly and accurately. Our experiments show that the proposed method can achieve a speedup of two orders of magnitude compared with the numerical method, with a relative error of no more than 0.1%. Based on our light weight energy estimation method, we presented new energy minimization techniques based on different task allocation methods and compared their efficiency in minimizing the overall energy consumption of a multi-core system.

#### 1.5 Structure of the Dissertation

This dissertation is organized as follows: We start by presenting pertinent background of our research work and related work in Chapter 2. Chapter 3 presents several fundamental theorems and properties in reducing peak temperature of a processor system. A novel real-time scheduling method, "M-Oscillations" that can reduce the peak temperature when scheduling a hard real-time periodic tasks set is introduced in Chapter 4. In Chapter 5, we present a set of feasibility checking methods for a hard real-time periodic tasks set to guarantee real-time constraints under maximum temperature constraints. In Chapter 6, we present a novel method to calculate the energy consumption efficiently and effectively for a given voltage schedule on a multicore platform, with the leakage/temperature dependency taken into consideration. Finally, in Chapter 7, we conclude this dissertation and discuss the possible future work of this research.

#### CHAPTER 2

#### Background and Related Work

In this chapter, we present pertinent background of our research and related work. We begin our discussion with a general introduction to the basic concepts related to the real-time systems and computing. Next, we discuss the power consumption sources in the CMOS circuits, followed by a survey on power and thermal management techniques at different design abstraction levels. Then, we present a literature review on the existing power/thermal aware scheduling methods that are closely related to this dissertation.

#### 2.1 Real-Time Systems and Computing

Real-time systems are pervasive. They are adapted and implemented in several domains of computing, like defense and space systems, communication systems, automotive systems, multimedia etc. Mostly hidden, real-time systems work in the heart of various computing platforms and perform important services for humankind. They reside in our cars controlling engine and brakes, in our TVs/games maintaining undisrupted entertainment, in health monitoring devices like blood pressure machine evaluating our fitness level, etc. With real-time systems finding utility in almost every electronic device around us and performing some very crucial tasks, the reliability and correctness of real-time systems becomes very important. It will be no exaggeration in identifying real-time computing and associated issues as the most important research area in the development of computing systems. In this section, we discuss some of the key concepts of real-time systems. We further discuss different problem areas and published solutions related to real-time scheduling.

#### 2.1.1 Real-Time Systems

In a real-time system the correctness of the system behavior depends not only on the logical result of the computations, but also on the physical instant at which these results are produced. A real-time system has to respond to an externally generated stimuli within a specified time [81, 114]. In simple words, we can describe a real-time system as a system that has a deadline. The violation of timing constraints in real-time systems degrade the quality of service and in some cases may also result in catastrophical accidents [81, 114]. Real-time systems can be broadly categorized into hard real-time systems with hard timing constraint and soft real-time systems that have some tolerance for timing lateness and may respond with decreased service quality.

In general, a unit of work that is scheduled and completed by a computing system is called a job, and a set of related jobs jointly executing some specific system function is called as a task [81]. The job/task models used in real-time systems are very important in characterizing the type of real-time computing system. A task can be periodic or aperiodic.

Periodic vs Aperiodic: A periodic task is a sequence of jobs, with a minimum length intervals between release times of two consecutive jobs. The tasks are invoked at regular intervals following a deterministic pattern of time intervals. For example, in air traffic control(ATC) system, the status of each aircraft is monitored using active radars. These radars check the status periodically and update the ATC controller [81]. On the other hand, an aperiodic or sporadic task is a sequence of jobs with unknown release times. These tasks are invoked in irregular pattern and the inter-arrival times between consecutive jobs in such a task may vary widely. For instance, in a setting of radar surveillance system, the system should be responsive to operators command but not on the expense of task with hard deadline.

#### 2.1.2 Real-Time Scheduling

In a real-time system the execution of every task requires computational and data resources. The real-time scheduling is concerned with the allocation and management of the resources to complete the assigned workload within the timing constraints. Given a task set with necessary timing information, available system resource and design constraints, the real-time scheduling answer the questions of when and where the task should be executed in order to satisfy timing constraints, at the same time other design metrics are optimized and never violated, e.g. energy, peak temperature etc.

Over the past several decades real-time scheduling has been studied extensively to address issues related to feasibility of task sets, performance optimization etc. for a span of combinations of processor architectures and task models. Based on different characteristics of applications, resource availability and system requirements, realtime scheduling methods can be classified in several ways:

Priority-driven vs Non-Priority : In priority driven real-time scheduling methods at any scheduling decision time, the jobs with the highest priorities are scheduled and executed on the available processors. Other commonly used names for this approach are greedy scheduling, list scheduling and work-conserving scheduling [81]. Some examples of priority-driven scheduling includes earliest deadline first (EDF) scheduling, rate monotonic scheduling(RMS) etc [79]. On the other hand in non-priority driven methods some policies like round-robin are used to determine if the task should start executing or not [121].

Moreover, priority-driven algorithms can be further divided into fixed/static priority algorithms and dynamic priority algorithms. In fixed priority algorithms, priorities of tasks are assigned during compile time and they remain unchanged throughout the execution, e.g. RMS. A fixed-priority algorithm assigns the same priority to all the jobs in each task. In contrast, a dynamic-priority algorithm assigns different priorities to the individual jobs in each task. Hence the priority of the task with respect to that of the other tasks changes as jobs are released and completed [81], e.g. EDF algorithms.

- 2. Preemptive vs Non-Preemptive : If the execution of lower priority task is stopped or preempt for a higher priority task then the scheduling scheme is called as preemptive scheduling and non-preemptive otherwise. Preemptive or non-preemptive scheduling of tasks is possible with static and dynamic scheduling [10].

- 3. On-line vs Off-line : On-line algorithms makes scheduling decisions during runtime. The parameters of each job become known to the on-line scheduler only after the job is released. All priority-driven algorithms are considered on-line scheduling techniques. In off-line scheduling, scheduling decisions are made statically during compile time. This assumes parameters of all the tasks is known a priori and builds a static schedule based on this [79].

Furthermore, real-time scheduling methods can be classified based on type of underlying architecture, i.e. uniprocessor scheduling and multiprocessor scheduling. When addressing scheduling problems on uniprocessors, a scheduler needs to deal with when the task should be executed such that the entire workload is feasible. On uniprocessor scheduling, work done by Liu and Layland [79] is of special interest and great importance. In [79], Liu and layland proposed two priority-driven scheduling algorithms i.e. a dynamic-priority scheduling named earliest deadline first(EDF) and a fixed priority algorithm called rate monotonic scheduling (RMS). Both EDF and RMS have been used extensively in the research domain as the underlying scheduling policy for other design metrics optimization like energy minimization ([101, 149, 103]), schedulability/feasibility analysis( [5, 100]) etc. In multiprocessor scheduling, the problem is not only to determine when a given task executes but also where it executes. There are also issues related to availability of necessary resources at the processor at which a task is scheduled to execute, contention for communication across a network, etc. These issues make the problem substantially harder to solve. There have been extensive researches published on real-time scheduling for homogeneous/heterogenous multi-core systems [9, 8, 69, 74, 51, 47]. These scheduling algorithms can be largely categorized into three classes: the partitioned approach (e.g. [9]), the global (or non-partitioned) approach (e.g. [8]) and the semi-partitioned approach (e.g. [69, 74, 51, 47].

In the partitioned scheduling, each real-time task is assigned to a dedicated processor. All instances from the same task will be executed solely on that particular processor. In global scheduling, all jobs first enter a global queue, and thus each task can be potentially executed on any processor. The semi-partitioned algorithms are combination of previous two approaches, i.e. some tasks are assigned to a dedicated processor, while rest can migrate among available resources.

#### 2.2 Power Minimization

The CMOS technology has served as the leading solution and will continue to be the primary solution for the foreseeable future in the design/fabrication of integrated circuits. As the goal of this dissertation is to address power/thermal issues in CMOS ICs, it is important to understand the basics of power dissipation in CMOS circuits.

#### 2.2.1 Power Dissipation in CMOS ICs

There are mainly two sources of power consumption in a CMOS circuit, i.e. dynamic power consumption and static/leakage power consumption.

Dynamic Power: The dynamic power dissipation is associated with the switch-

Figure 2.1: A CMOS Inverter Circuit [95]

ing of logic values in the circuit. This power component is essential to performing useful logic operations and occurs during the charging/discharging of the load capacitor in MOS transistors, as in Figure 2.1 [95, 107]. It can be formulated as [107]:

$$P_{dyn} = \alpha_{0->1} * C_L * V_{dd}^2 * f \tag{2.1}$$

Where  $\alpha_{0->1}$  is the switching factor,  $V_{dd}$  represents the supply voltage,  $C_L$  is the load capacitance and f represents the clock frequency. Equation (2.1), implies the methods and underlying fundamental principles in dynamic power reduction, such as reducing activity ( $\alpha_{0->1}$ ), reducing the circuit complexity ( $C_L$ ), scaling the supply voltage( $V_{dd}$ ) and/or adjusting the circuit speed (f). We can also notice that the impact of scaling supply voltage to dynamic power can be significant as they share a quadratic relation. Leakage power: The static power is associated with maintaining the logic values of internal circuit nodes between the switching events. This type of power consumption mostly comes from leakage power which occurs when the leakage current flows through diodes or transistors. Such a power dissipation does not contribute to any useful computation. Leakage power can be formulated as [107]:

$$P_{leak} = I_{leak} * V_{dd} \tag{2.2}$$

Where  $I_{leak}$  is the leakage current and  $V_{dd}$  is the supply voltage. In MOS transistors (PMOS/NMOS), there are three main sources of leakage current, as shown in Figure 2.2

- 1. Source/Drain Junction Leakage Current  $(I_D)$ : The junction leakage occurs from the source or drain to the substrate through the reverse-biased diodes when a transistor is OFF. The magnitude of the junction leakage current depends on the area of the drain diffusion and the leakage current density, which is in turn determined by the process technology [95, 107].

- 2. Gate Direct Tunneling Leakage Current  $(I_G)$ : The gate direct tunneling leakage flows from the gate through the leaky oxide insulation to the substrate. Its magnitude increases exponentially with the gate oxide thickness and supply voltage [95, 107].

- 3. Sub-Threshold Leakage Current  $(I_{SUB})$ : The sub-threshold current is the drainsource current of an OFF transistor. This is due to the diffusion current of the minority carriers in the channel for a MOS device operating in the weak inversion mode (i.e., the sub-threshold region). The magnitude of the subthreshold current is a function of the temperature, supply voltage, device size, and the process parameters out of which the threshold voltage plays a dominant

Figure 2.2: Types of Leakage Current in MOS [95]

role [95, 107].

It has been studied that the leakage current due to subthreshold conduction ( $I_{SUB}$  and gate leakage current ( $I_G$ ) (see Figure 2.2) are the dominating component among different types of leakage current [107, 95]. Following what, Liao et al. established a complex relationship between the leakage current and the temperature and formulated the leakage current as: [77],

$$I_{leak} = I_s \cdot (\mathcal{A} \cdot T^2 \cdot e^{((\alpha \cdot V_{dd} + \beta)/T)} + \mathcal{B} \cdot e^{(\gamma \cdot V_{dd} + \delta)}), \tag{2.3}$$

where  $I_s$  is the leakage current at certain reference temperature and supply voltage, T is the operating temperature,  $V_{dd}$  is the supply voltage,  $\mathcal{A}, \mathcal{B}, \alpha, \beta, \gamma, \delta$  are empirically determined technology constants. This model is used extensively in several research work in developing theoretical framework for system level analysis [35, 30, 66, 140, 106, 100]. This micro-architecture level modeling is very complex and unwieldily to be implemented for system level analysis. Following which, Liu et al. [84] demonstrated that within a temperature range using a piece-wise linear model can accurately estimate leakage power consumption (within 1% relative error). Moreover, for a tighter temperature range linear models can be fairly accurate. Based on this observation, a number of researches (such as [35, 48, 30]) adopted a simple temperature/leakage dependency model that assumes the leakage current changes linearly only with temperature. Quan et al. [104] introduced a more accurate and practical linear model that is sensitive to both temperature and supply voltage (with 5% relative error). A detailed comparative study of different leakage models is presented in [59].

#### 2.2.2 Power Minimization Methodologies

As power consumption becoming more and more critical, research has been conducted at various design abstraction levels, i.e. architecture level, system level, logic level, circuit level and device level, targeting both dynamic power and leakage power consumptions.

**Dynamic Power Minimization**: To reduce the dynamic power, techniques that can help to reduce the factors formulated in Equation 2.1, namely capacitance, supply voltage, frequency, and switching activity, have been developed at different design abstraction levels:

• Dynamic Voltage and Frequency Scaling (DVFS/DVS): In general real-time systems are usually designed under the assumption of worst case execution time (WCET). Since tasks rarely execute up to their WCETs, there are good opportunities for power and energy savings. DVFS (or DVS) is a method to provide variable amount of energy for a task by scaling the operating voltage/frequency at run-time ( $V_{dd}$  and f in Equation 2.1). With dynamic power having convex relationship with supply voltage, this technique is one of the most effective

dynamic power reduction methodology [125]. Most modern processors today are augmented with hardware blocks that allow changing the supply voltage dynamically [134, 107, 95, 101].

- Clock Gating : Clock-gating is a well known High level (architecture/ RTL) technique for reducing dynamic power consumption of the synchronous designs. Clock power is a major component of total power consumption (about 40%), which makes clock-gating a very important power saving technique. Several work on low power design using different variation of clock gating are available in literature [129, 89, 44]

- Logic Gate Restructuring : This is a logic-level strategy to attack the switching activity factor (α<sub>0->1</sub> in Equation 2.1) by improving the topology of the logic network. The topology of a logic network can severely affect the power dissipation. For example, in Figure 2.3, both chain and tree structure give same output. However, the switching activity factor of chain structure is observed to be less than the tree structure for random inputs [107]. Besides logic gate restructuring, there are some other techniques like input reordering, path balancing methods etc. which are used for reducing the switching activity by either removing spurious transitions due to glitching/jitter or reducing delay in intermediate nodes through reordering the input signals [107].

- Transistor Sizing : Transistor sizing is a circuit level technique that target load capacitance ( $C_L$  in Equation 2.1) of CMOS gates to minimize dynamic power consumption. The rationale behind transistor sizing is that not every transistor is required to be large (fast) for performance. This is a complex method that involves caution and is implemented based on peformance/power tradeoff factors [107]. Several research work on developing algorithms for better

Figure 2.3: A Logic Restructuring Example [95]

transistor sizing decisions are available in the literature [108, 37].

Leakage Power Minimization: Leakage power dissipation is becoming substantial in the modern CMOS VLSI circuits. It severely impact the design of the future computing systems and is of vital importance. Due to the continuous scaling of device sizes (Moore's law), the voltage supply levels and threshold voltage of MOS transistors are also scaling. Based on the leakage model discussed above, we now present some of the effective leakage power minimization techniques

- Body Biasing: The leakage current can be reduced by reverse body biasing that increases the threshold voltage of transistors in STANDBY modes [112, 95]. Due to reverse biasing, a transistor increases its threshold voltage. This results in a decrease in the leakage current of the transistor. Because the threshold voltage changes with the square root of the reverse bias voltage [107], a large voltage may be necessary to get a small increase in the threshold voltage. As a result, this method becomes less effective as the supply voltage is scaled down.

- Power Gating : Power gating is an intuitive method to address leakage power dissipation during device off-mode. It is implemented using one PMOS transistor and one NMOS transistor in series with the transistors of each logic block to create a virtual ground and a virtual power supply as depicted in Figure 2.4. During the STANDBY state of the circuit, the extra transistor disconnect the gate from the ground, hence increasing threshold voltage. In

Figure 2.4: Power Gating Circuit [95]

practice, Dual CMOS or Multi-Threshold CMOS (MTCMOS) is used for power gating [95, 70, 12]. The implementation of this technique is non-trivial, specially for sequential circuits.

• Minimum Leakage Vector Method : The leakage current of a circuit is a strong function of its input values. In [6], Abdollahi et al. leveraged on this fact to reduce leakage current. They formulate the problem of finding the minimum leakage vector (MLV) using a series of Boolean Satisfiability problems. The solution vector was used to reduce leakage power by driving the circuit using calculated input vector during STANDBY mode [95, 49]. This method is inferior to power gating in terms of magnitude of leakage reduction, but is free from any implementation difficulties [95, 49].

As previously discussed, controlling chip temperature is also an effective method to reduce leakage power consumption.

#### 2.3 Temperature Minimization

In managing thermal problems, thermal modeling is of critical importance to explore the large design space without expensive silicon prototypes [60]. Thermal models facilitate accurate characterization of thermal stress, temporal and spatial non-uniformities and application dependent behavior [119].

To study thermal-aware design techniques at the architectural-level, Skadron et al. [4, 119] proposed an accurate and fast architectural-level thermal model called "Hotspot". The thermal modeling is based on the well known duality between the heat transfer and the electrical current flow (as shown in Table 2.1),

| Table 2.1. Duanty Detween Thermai and Dicethear Quantities |                                    |

|------------------------------------------------------------|------------------------------------|

| Thermal Quantity                                           | Electrical Quantity                |

| Power consumption: $P(W)$                                  | Current flow: $I(A)$               |

| Temperature: $T(^{o}C)$                                    | Voltage: $V(V)$                    |

| Thermal resistance: $R (^{o}C/W)$                          | Electrical resistance: $R(\Omega)$ |

| Thermal capacitance: $C(J/^{o}C)$                          | Electrical capacitance: $C(F)$     |

Table 2.1: Duality Between Thermal and Electrical Quantities

HotSpot models every power consuming smallest micro-architecture block of processor as a node in an RC network. In this way, each functional unit on the chip is represented by one or more nodes within the RC network 2.5. The HotSpot model includes active layer, thermal interface layer, heat spreader layer and heat sink layer, resulting in a three dimensional RC network. Based on this RC network and basic circuit laws, a system of differential equation is established.

HotSpot uses fourth order Runge-Kutta method to solve this set of differential equations to capture the thermal dynamics of microprocessors. The model has been validated using finite element simulation. HotSpot has a simple set of interfaces and hence can be integrated with most power-performance simulators [119]. The chief advantage of HotSpot is that it is compatible with the kinds of power/performance models used in the computer-architecture community, requiring no detailed design or synthesis description.

Figure 2.5: Using RC Network to Model a Processor's Heat Transfer [119]

# **Temperature Minimization Methodologies**

Developing solutions for thermal related issues is not a straight forward effort, like what we see in the power minimization techniques. One interesting fundamental of the thermal issues is that even though technically temperature is a byproduct of power consumption, but thermal management problems are distinctly different from the power management issues [118]. In modern integrated circuits, heat dissipation is not uniform on the chip creating several hot spots or high power density points. This non-uniformity gets worse with increasing transistors density, non-uniform scaling of supply voltage and increasing leakage power consumption.

As a result, an effective low-power technique may have little or no effect on operating temperature of the chip [118, 77, 106]. In fact, sometimes low power techniques could result in the higher temperature due to smaller structures and limiting activity to a smaller area [60]. There is another one important difference between power management and thermal management solutions, i.e. power management techniques usually seek to reduce total chip power ignoring localized power densities, on the other hand temperature management methods control local hot spots [60].

The traditional way to protect ICs from worst case heat dissipation is to depend heavily on the rather expensive thermal package solutions (e.g. heat sink, fan, cold plates etc.). However, with rising packaging costs and meagre chances of worst case temperature to happen, this solution can be costly. Moreover, with processors evolving from single core to multi-core, conventional back-side heat removal strategies such as air-cooled heat sink etc. are insufficient to provide better cooling.

Therefore, better cooling solutions like inter-tier liquid cooling, micro-channel liquid cooling etc. are gaining lot of attentions for efficient heat removal. For instance, in [120], an energy efficient dynamic inter-tier liquid cooling method is proposed, that can achieve as much as 30% reduction in system level energy consumption. In addition, any applications that dissipate more heat than package capacity, should engage an alternative dynamic thermal management technique (DTM) [118].

**Dynamic Thermal Management Approaches**: In the recent years, dynamic thermal management(DTM) has emerged as an interesting and very effective thermal management scheme [119]. DTM allows an adaptive control on chip temperature by dynamically applying forced (e.g. clock throttling) heat reduction when the chip reaches a thermal emergency situation. It addresses the problem of higher thermal packaging costs by allowing designers to use thermal packaging for some lower temperature instead of high temperature due to peak power consumption.

A number of DTM approaches are proposed recently, such as task migration [78], global clock gating [52], fetch toggling [26] and decode throttling [119]. Out of which, task migration and clock gating are widely used in the temperature minimization.

#### 2.4 Power/Thermal Aware Scheduling

The system-level scheduling techniques are very effective in addressing power/thermal issues in microprocessors. In past two decades power/thermal aware scheduling methods have been studied extensively for both single core (e.g. [134, 64, 97, 127] etc.) and multi-core architectures (e.g. [124, 36]etc).

#### 2.4.1 Scheduling Solutions for Dynamic Power reduction

The early efforts in the real-time scheduling were focused on using DVS for reducing the then dominant dynamic power consumption (e.g. [134, 64, 97] etc.). For instance, addressing single processor architectures, Yao et al. [134] proposed an energy-optimal off-line scheduling method with continuous speed levels. Employing this greedy algorithm, Yao et al. proved that using lowest constant speed to complete the task results in the minimum energy consumption. Ishihara et al. [64] extended this work to discrete speed levels and proved that if this constant speed is not available then using the two neighboring speeds will be the next optimal solution. Pillai et.al [97] proposed a couple of on-line real-time DVS scheduling schemes that can guarantee deadlines of tasks saving significant energy consumption. Several other related approaches were proposed in [71, 101, 102, 115]. For example, Kim et al. [71] proposed an energy reduction technique for periodic tasks with EDF priority by improving slack time estimation. On the other hand, authors in [101, 102, 115], addressed fixedpriority scheduling exploiting slack time for power reduction using power down mode and DVS.

The energy-efficient scheduling in multi-core systems are often NP-hard, as a result several heuristics and approximation techniques are studied to minimize dynamic energy consumption on multi-core platforms [143, 33, 50, 148]. In [50] Gruian used simulated annealing algorithm for task to core allocation and developed two-stage energy minimization method when scheduling tasks with inter-dependencies. Zhang et al. [143] proposed a technique that finds the optimal task allocation for energy minimization by exhaustively checking all possible permutations of task allocation running on the minimum speed that could guarantee real-time constraints for each task. A heuristic algorithm with largest task first strategy is proposed in [33]. Moreover, exploiting slack time sharing on multiple processors, Zhu et al. [148] developed a power-aware scheduling method for energy minimization such that timeliness of the schedule is never violated.

#### 2.4.2 Scheduling for Overall Power Reduction with Constant Leakage

Reducing dynamic power consumption is important in solving energy efficiency problems, however, ignoring leakage power consumption leaves the above mentioned scheduling techniques ineffective in contemporary and modern integrated circuits. Acknowledging the growing dominance of leakage power dissipation in overall energy consumption, several research works are published addressing overall energy minimization in both single core (e.g. [63, 67, 94, 103] etc.) and multi-core platforms(e.g. [131, 34, 42] etc). For example, Irani et al. [63] proposed an off-line approximation algorithm with a competitive ratio of 3 on a DVS processor with continuous speed levels. The approach is based on energy-optimal greedy algorithm in [134]. They also proposed an on-line algorithm with constant approximation factor.

In a separate approach, authors in [94] and [103] proposed efficient method that merge idle intervals due in a DVS schedule by delaying the execution of task instances, so that the processor shutdown overhead can be reduced and the overall energy performance can be improved. When addressing overall energy minimization on multi-core systems, Langen et al. [42] presented leakage-aware heuristics to determine tradeoff between DVS, shut down and optimal number of active processors. In a related work, Xu et al. [131] proposed an algorithm to estimate the system load and corresponding optimal number of processing nodes for energy efficiency in cluster systems. Unlike [42], processors in this work are assumed to have discrete speed levels. However, all these techniques for overall energy reduction modeled leakage power as a constant value and therefore their efficiency in energy reduction is strictly limited, abandoning energy-efficiency to continue as a grave challenge.

# 2.4.3 Thermal Aware Scheduling

In addition, along with technology scaling thermal challenges are growing aggressively, making temperature a critical constraint to achieve desirable performance. Moreover, as previously mentioned that power/energy aware solutions are incompetent to address thermal issues single handedly, an increasing number of researches have been published on thermal-aware scheduling for both single and multiple processor platforms(e.g. [14, 105, 139, 127, 109] etc). For example, in [14] and [32] authors try to identify the upper bound of the maximal temperature when executing realtime tasks on a single processor. These techniques cannot guarantee that real-time tasks can still meet deadlines when the maximal temperature is given. Some others (e.g. [14, 38, 29, 109]) intend to minimize the peak temperature or guarantee the given maximal temperature constraints when scheduling a job set or a single copy of a task graph. For example, Chantem et al. [29] proposed an MILP-based solution to minimize the peak temperature when executing a task graph.

Recently, significant amount of 3D thermal-conscious OS-level work has been published [40, 146, 76, 83, 87, 122]. In [146], an online thermal-aware task scheduling technique for high performance with reduced peak temperature is proposed. The methodology involves temperature-balance among 'super-cores' combined with DVFS to avoid thermal emergencies. An online rotation task scheduling policy to reduce peak temperature on the 3D multi-core system is proposed in [76]. Liu et al. [83] proposed a thermal-aware job allocation technique, which always assigns hot jobs to core near heat sink, for fast heat removal so that the peak temperature of the system can be reduced.

# 2.4.4 Power/Thermal Aware Scheduling with Temperature Sensitive Leakage Power

Several power/thermal aware scheduling methods have been proposed addressing various design metrics for both single core and multi-core systems incorporating leakage/temperature dependency into system models. For example, in [104, 100], authors formulated several feasibility checking methods when scheduling a periodic tasks set on a uniprocessor. In [31, 73, 139, 66, 29, 48] etc. several thermal-aware scheduling techniques were proposed to reduce peak temperature on both single core and multicore processors. In [66] Jayaseelan et al. proposed different iterative job sequencing techniques to identify the peak temperature and to reduce the peak temperature of the system. Kumar et. al [73] proposed a stop-n-go approach to reduce the peak temperature for task with data dependencies. They distribute the slack time between jobs such that temperature can be minimized and there is no make-span violation. In [35], Chen et al. proposed proactive scheduling methods to minimize response time under the thermal constraint, and also the reduction of the peak temperature under timing constraints. Fisher et al. [48] proposed method to minimize the peak temperature in a homogeneous multi-core system, by deriving an ideally preferred speed for each core in a global task scheduling environment.

As we know escalating energy consumption is a serious problem, that worsen with leakage and temperature interplay, authors in [57, 132, 17, 53, 85] proposed techniques to minimize energy consumption under peak temperature constraints. For instance, Huang et al. [57] derived a closed-form energy calculation equation based on which they further proposed an energy minimization scheduling method for periodic task sets. In [132], Yang et al. presented a procedure to find the optimal pattern of schedule with the minimum energy consumption at the steady state. Hanumaiah et al. [53] formulated energy minimization as a quasiconcave optimization problem and employed DVFS, task migration and cooling methods to optimize the objective function on a multi-processor system. On the other hand, Liu et.al [85] developed a thermal-constrained energy optimization procedure to minimize system energy consumption under peak temperature constraint.

Performance optimization has always been the first class design objective specially with temperature constraints. In [30, 58, 80, 54] and [55] authors proposed techniques to improve processor performance by maximizing the throughput or minimizing the makespan time under peak temperature limitations. Chantem et al. [30] proposed to run real-time tasks by frequently switching between the two speeds which are neighboring to the constant speed whose stable temperature is the given peak temperature. In [58], Huang et al. proposed two approaches to maximize the throughput for a periodic real-time system under the given peak temperature constraint, one for processor with simple active and sleep mode and the other for more complicated processors with DVFS capabilities. When maximizing throughput on multi-core platforms, authors in [55] address task-to-core allocation over migration intervals and voltage speed scaling within migration intervals as a separate problem and translated task-to-core allocation in *MILP*-formulation. To reduce the non-linearity of the function several assumptions were made to solve the optimization functions.

Including leakage power model, Zhu et al. [147] proposed a run-time thermal management technique that exploits the heterogeneity of execution cores and workload. They proposed a proactive hardware-OS assisted technique to achieve efficient thermal management. A closely related adaptive approach that balances the temperature on the cores,' Adapt3D' was proposed by Coskun et al. [40]. Coskun et al. used a second order polynomial temperature dependence leakage model in their method and proposed a thermal-aware job scheduling technique that uses a thermal history of neighbors in job allocation decisions.

#### 2.5 Conclusions

In this chapter, we discussed several relevant background of our research and related work. We presented a general introduction to the basics of real-time systems, task models and real-time scheduling. Next, we discussed power/thermal modeling and several effective ways to address power/thermal challenges from different design abstraction levels. We then, presented a literature review on the existing power/thermal aware scheduling methods that are closely related to this dissertation.

In this dissertation, our goal is to develop power/thermal aware scheduling solutions for both single core and multi-core, hard real-time system with deterministic workload under various design constraints. In the next four chapters, i.e. Chapters 3, 4, 5 and 6 we present our contributions. We will conclude this dissertation in Chapter 7.

#### CHAPTER 3

# Fundamentals of Leakage Aware Real-Time DVS Scheduling for Peak Temperature Minimization

In the previous chapter, we discussed some of the background information that is closely related to our research work. We now present a detail discussion on our first contribution. In this chapter, we study the fundamental principles on how to employ dynamic voltage scaling (DVS) to reduce the peak operating temperature. Our goal is to formulate guidelines and principles that can be used to make effective decisions when applying DVS for thermal management.

Since the thermal management problem is closely related to the power reduction problem, we started our research by investigating how effective the basic principles for energy reduction can be, when applied for dynamic thermal management. We began with the two well-known principles ([134, 64]), for dynamic energy reduction,

- *Principle 1*: Using the lowest constant speed leads to the schedule that consumes the minimum dynamic energy;

- *Principle 2*: If a single lowest constant speed is not available, then using two closest neighboring speeds is the optimal solution in dynamic energy reduction.

The question then becomes: when considering the complex relationship among the leakage power, the temperature, and the supply voltage, is it still true that a real-time schedule employing the lowest constant speed will lead to the lowest peak temperature within the scheduling interval? We find that, for a specific workload and interval, the schedule that uses the lowest constant speed is not necessarily optimal anymore in reducing the peak temperature. We identify the scenarios when a schedule that uses two different speeds may in fact lead to lower peak temperature. We also find that principles similar to the two listed above do exist to minimize the peak temperature

during the temperature *stable status* when scheduling a periodic task. We formulate our observations into several theorems with formal proofs. The significance of this chapter is that it uncovers a number of fundamental principles in the development of effective DVS techniques for thermal aware computing.

The rest of the Chapter is organized as follows. Section 3.1 introduces the related work. System models used in this chapter are defined in Section 3.2. Section 3.3 presents our empirical results to motivate our research. Fundamental principles are formulated and proved in Section 3.4 and 3.5. Section 3.6 concludes the chapter.