# Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

7-24-2012

# Improving Caches in Consolidated Environments

Ricardo Koller Florida International University, rkoll001@fiu.edu

**DOI:** 10.25148/etd.FI12080801 Follow this and additional works at: https://digitalcommons.fiu.edu/etd

## **Recommended** Citation

Koller, Ricardo, "Improving Caches in Consolidated Environments" (2012). *FIU Electronic Theses and Dissertations*. 708. https://digitalcommons.fu.edu/etd/708

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

# FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# IMPROVING CACHES IN CONSOLIDATED ENVIRONMENTS

A dissertation submitted in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

# COMPUTER SCIENCE

by

Ricardo Koller

2012

To: Dean Amir Mirmiran College of Engineering and Computing

This dissertation, written by Ricardo Koller, and entitled Improving Caches in Consolidated Environments, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Giri Narasimhan

Ming Zhao

Chen Liu

Murali Vilayannur

Raju Rangaswami, Major Professor

Date of Defense: July 24, 2012

The dissertation of Ricardo Koller is approved.

Dean Amir Mirmiran College of Engineering and Computing

> Dean Lakshmi N. Reddi University Graduate School

Florida International University, 2012

© Copyright 2012 by Ricardo Koller All rights reserved.

## ACKNOWLEDGMENTS

Muchas gracias a mis padres: Silvia, James, Norma y Ludvik. Many thanks to my collaborators: Raju Rangaswami, Akshat Verma, Ali Mashtizadeh and Murali Vilayannur. Akshat contributed to formulating the ERSS tree model. Ali and Murali helped in designing and coding the SSD cache for virtual machines. And Prof. Raju who, besides being my advisor and a great friend, contributed to imagining, designing, and evaluating all the systems presented in this thesis.

# DEDICATION

Para la princesa y mi gorda.

# ABSTRACT OF THE DISSERTATION IMPROVING CACHES IN CONSOLIDATED ENVIRONMENTS

by

Ricardo Koller

Florida International University, 2012

Miami, Florida

Professor Raju Rangaswami, Major Professor

Memory (cache, DRAM, and disk) is in charge of providing data and instructions to a computer's processor. In order to maximize performance, the speeds of the memory and the processor should be equal. However, using memory that always match the speed of the processor is prohibitively expensive. Computer hardware designers have managed to drastically lower the cost of the system with the use of memory caches by sacrificing some performance. A cache is a small piece of fast memory that stores popular data so it can be accessed faster. Modern computers have evolved into a hierarchy of caches, where a memory level is the cache for a larger and slower memory level immediately below it. Thus, by using caches, manufacturers are able to store terabytes of data at the cost of cheapest memory while achieving speeds close to the speed of the fastest one.

The most important decision about managing a cache is what data to store in it. Failing to make good decisions can lead to performance overheads and overprovisioning. Surprisingly, caches choose data to store based on policies that have not changed in principle for decades. However, computing paradigms have changed radically leading to two noticeably different trends. First, caches are now consolidated across hundreds to even thousands of processes. And second, caching is being employed at new levels of the storage hierarchy due to the availability of high-performance flash-based persistent media. This brings four problems. First, as the workloads sharing a cache increase, it is more likely that they contain duplicated data. Second, consolidation creates contention for caches, and if not managed carefully, it translates to wasted space and sub-optimal performance. Third, as contented caches are shared by more workloads, administrators need to carefully estimate specific per-workload requirements across the entire memory hierarchy in order to meet per-workload performance goals. And finally, current cache write policies are unable to simultaneously provide performance and consistency guarantees for the new levels of the storage hierarchy.

We addressed these problems by modeling their impact and by proposing solutions for each of them. First, we measured and modeled the amount of duplication at the buffer cache level and contention in real production systems. Second, we created a unified model of workload cache usage under contention to be used by administrators for provisioning, or by process schedulers to decide what processes to run together. Third, we proposed methods for removing cache duplication and to eliminate wasted space because of contention for space. And finally, we proposed a technique to improve the consistency guarantees of write-back caches while preserving their performance benefits.

# TABLE OF CONTENTS

| CHAPTER F                                                                                                | PAGE |

|----------------------------------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                                                          | . 1  |

| 2. THESIS OVERVIEW                                                                                       | . 5  |

| 2.1 Thesis Statement                                                                                     |      |

| 2.2 Thesis Contributions                                                                                 |      |

| 2.3 Thesis Significance                                                                                  |      |

| 2.3.1 Using data de-duplication to improve caching efficiency                                            |      |

| 2.3.2 Modeling cache usage                                                                               |      |

| 2.3.3 Reducing cache contention                                                                          |      |

| 2.3.4 Guaranteeing consistency in write-back policies                                                    |      |

|                                                                                                          |      |

| 3. CONTENT ADDRESSED CACHING                                                                             | . 10 |

| 3.1 Motivation $\ldots$ | . 12 |

| 3.2 Design                                                                                               | . 16 |

| 3.2.1 Architectural Overview                                                                             | . 16 |

| 3.2.2 Content addressed caching                                                                          |      |

| 3.2.3 Persistence of metadata                                                                            | . 21 |

| 3.3 Experimental Evaluation                                                                              | . 22 |

| 3.3.1 Evaluating performance                                                                             | . 23 |

| 3.3.2 Evaluating Overhead                                                                                |      |

| 3.4 Related work                                                                                         | . 27 |

| 3.5 Summary                                                                                              | . 29 |

| 4. MODELING CACHE REQUIREMENTS AND CONTENTION                                                            | . 30 |

| 4.1 Gaps in Existing Models and Characterization                                                         |      |

| 4.2 The Generalized ERSS Tree Model                                                                      |      |

| 4.2.1 Capacity Related Parameters                                                                        |      |

| 4.2.2 Generalized ERSS Tree                                                                              |      |

| 4.2.3 Wastage                                                                                            |      |

| 4.2.4 Using the Generalized ERSS Tree Model for Provisioning                                             |      |

| 4.3 Building the Generalized ERSS Tree Model                                                             |      |

| 4.3.1 Methodology Overview                                                                               |      |

| 4.3.2 Refinement Level Identification                                                                    |      |

| 4.3.3 Resource Limited Execution                                                                         |      |

| 4.3.4 Atomic Refinement                                                                                  | . 49 |

| 4.4 Experimental Validation of the Model                                                                 |      |

| 4.4.1 Experimental Setup                                                                                 |      |

| 4.4.2 The need for the Generalized ERSS Tree Model                                                       |      |

| 4.5 Related work                                                                                         |      |

| 4.5.1 Mechanisms to build memory usage models                                                            |      |

| 4.6 Summary 59                                       |

|------------------------------------------------------|

| 5. PARTITIONING FOR EXTERNAL MEMORY CACHES           |

| 5.1 Background on cache partitioning                 |

| 5.2 Solution overview                                |

| 5.3 The Partitioning Algorithm                       |

| 5.3.1 Partitioning for latency minimization          |

| 5.3.2 Partitioning for all other performance goals   |

| 5.4 Implementation                                   |

| 5.4.1 Cache management                               |

| 5.4.2 Data consistency                               |

| 5.5 Experimental validation                          |

| 5.5.1 Experimental Setup                             |

| 5.5.2 Partitioned SSD cache                          |

| 5.5.3 Overheads                                      |

| 5.5.4 Adaptation to specific storage characteristics |

| 5.6 Related work                                     |

| 5.7 Summary                                          |

| v                                                    |

| 6. CONSISTENCY IN WRITE-BACK CACHES 80               |

| 6.1 Background                                       |

| 6.1.1 Consistency and staleness                      |

| 6.1.2 Write-through and write-back policies          |

| 6.2 Motivation                                       |

| 6.3 Consistency-preserving Write-back Caching        |

| 6.3.1 Ordered write-back                             |

| 6.3.2 Journalined write-back                         |

| 6.4 Consistency analysis                             |

| 6.5 Performance evaluation                           |

| 6.5.1 Experimental Setup 94                          |

| 6.5.2 Performance evaluation                         |

| 6.6 Related work                                     |

| 6.7 Summary                                          |

| 7. CONCLUSIONS                                       |

| BIBLIOGRAPHY                                         |

| VITA                                                 |

# LIST OF FIGURES

| FIG | URE PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AGE |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

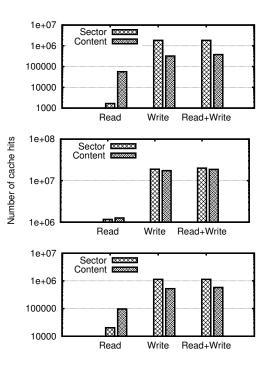

| 3.1 | Page cache hits for the web-vm (top), mail (middle), and homes (bot-<br>tom) workloads. A single day trace was used with an infinite cache<br>assumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14  |

| 3.2 | Contrasting content and sector reuse distances for the web-vm (top),<br>mail (middle), and homes (bottom) workloads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15  |

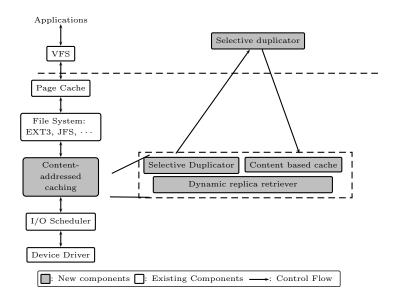

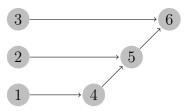

| 3.3 | System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17  |

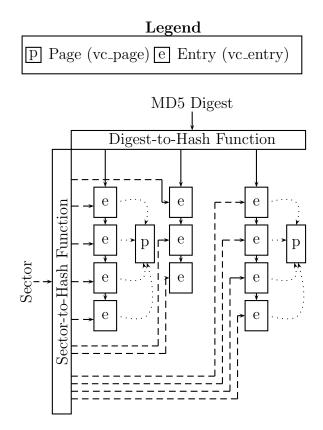

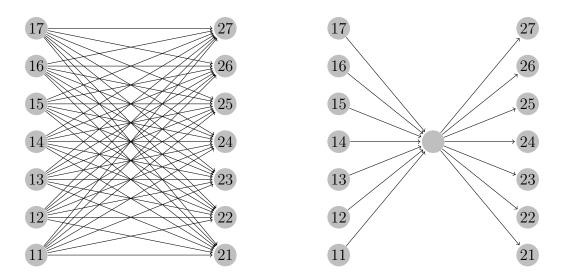

| 3.4 | Data structure for the content-addressed cache. The cache is address-<br>able by both sector and content-hash. vc_entries are unique per<br>sector. Solid lines between vc_entries indicate that they may have<br>the same content (they may not in case of hash function collisions.)<br>Dotted lines form a link between a sector (vc_entry) and a given<br>page (vc_page.) Note that some vc_entries do not point to any page<br>– there is no cached content for these entries. However, this indicates<br>that the linked vc_entries have the same data on disk. This happens<br>when some of the pages are evicted from the cache. Additionally,<br>pages form an LRU list. | 18  |

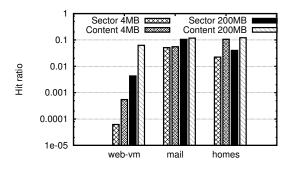

| 3.5 | Per-day page cache hit ratio for content- and sector- addressed caches for<br>read operations. The total number of pages read are 0.18, 2.3, and<br>0.23 million respectively for the web-vm, mail and homes workloads.<br>The numbers in the legend next to each type of addressing represent<br>the cache size.                                                                                                                                                                                                                                                                                                                                                                 | 23  |

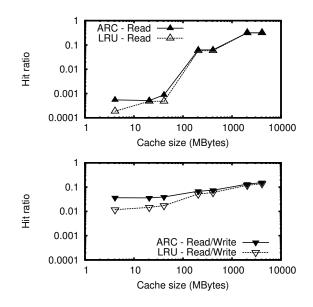

| 3.6 | Comparison of ARC and LRU content-addressed caches for pages read<br>only (top) and pages read/write operations (bottom). A single day<br>trace (0.18 million page reads and 2.09 million page read/writes) of<br>the web workload was used as the workload.                                                                                                                                                                                                                                                                                                                                                                                                                      | 24  |

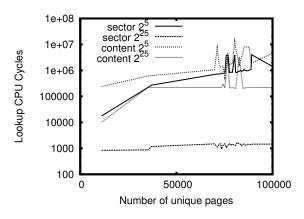

| 3.7 | Overhead of content and sector lookup operations with increasing size<br>of the content-addressed cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25  |

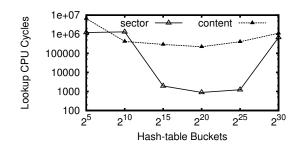

| 3.8 | Overhead of sector and content lookup operations with increasing hash-<br>table bucket entries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26  |

| 4.1 | An illustration of the model concepts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37  |

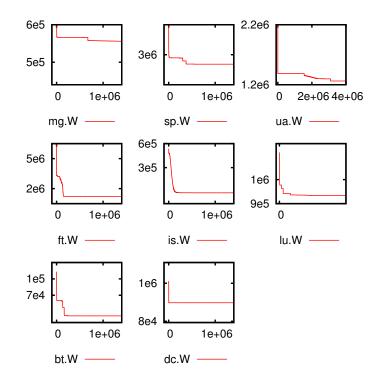

| 4.2 | MRCs for the NAS benchmark applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38  |

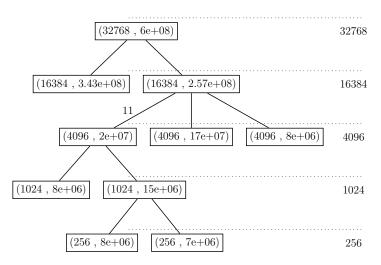

| 4.3 | A sample Generalized ERSS Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39  |

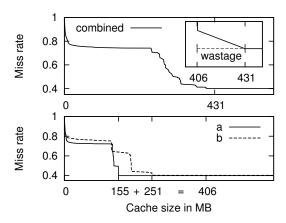

| 4.4 | Working set sizes and wastage on multi-workload MRC. Curves a and b<br>are the MRCs of the individual workloads and combined is the MRC<br>of both a and b running together. The reuse set sizes (RSS) of a,<br>b and combined are 155, 251 and 431 respectively. Notice how the<br>RSS of combined is larger than the sum of a and b's RSS                                                                                                                                                                                                                                                                                                                                       | 40  |

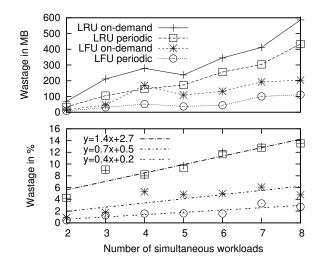

| 4.5 | Wastage with multiple workloads. Figure on top shows wastage in MB and figure at the bottom shows wastage as a percentage of the total amount of cache: $100^*W/RSS_c$ , where W is wastage and $RSS_c$ is the reuse set size of the combined workload. Notice how wastage as a percentage increases linearly with the number of workloads $\ldots$ . | 42 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6 | Phase Identification State Diagram.                                                                                                                                                                                                                                                                                                                   | 50 |

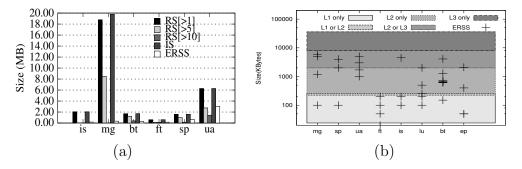

| 4.7 | (a) IS, RS, ERSS for one phase. (b) ERSS of various phases for NAS applications.                                                                                                                                                                                                                                                                      | 54 |

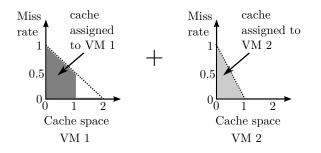

| 5.1 | Example of cache partitioning. A cache of size 2 is partitioned across two VMs. Both VMs MRCs are shown with the optimal assignment of cache shown in grey: one cache unit to each VM                                                                                                                                                                 | 62 |

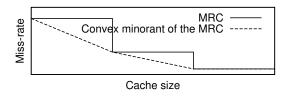

| 5.2 | Example of MRC and its convex minorant                                                                                                                                                                                                                                                                                                                | 62 |

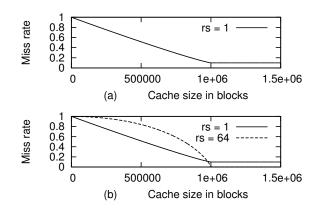

| 5.3 | MRCs for large requests sizes. (a) shows the MRC of a workload accessing a file of one million blocks with request size of one block and (b) shows the MRC for the same workload and a slightly different one where the request size was increased to 64 blocks. Note how the MRC gets concave with a large request size                              | 64 |

| 5.4 | Solution architecture.                                                                                                                                                                                                                                                                                                                                | 65 |

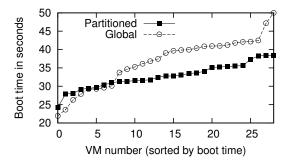

| 5.5 | 28 Virtual Linux desktops booting simultaneously using an 6 GB SSD cache. This figure shows the boot time using a global LFU cache and a partitioned LFU cache                                                                                                                                                                                        | 72 |

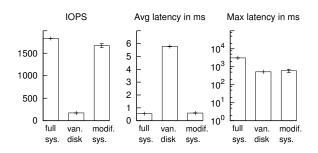

| 5.6 | System performance compared to vanilla disk and a simplified cache.<br>4kb aligned random reads/writes on 1GB using 100MB of cache                                                                                                                                                                                                                    | 73 |

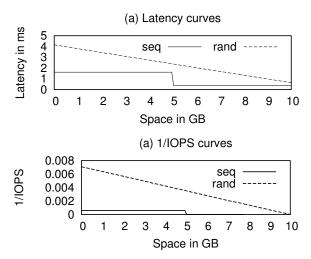

| 5.7 | Latency and $IOPS^{-1}$ curves.                                                                                                                                                                                                                                                                                                                       | 75 |

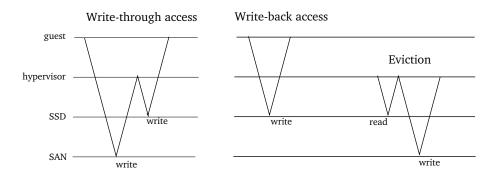

| 6.1 | Representation of a write access for write-back and write-through write policies                                                                                                                                                                                                                                                                      | 83 |

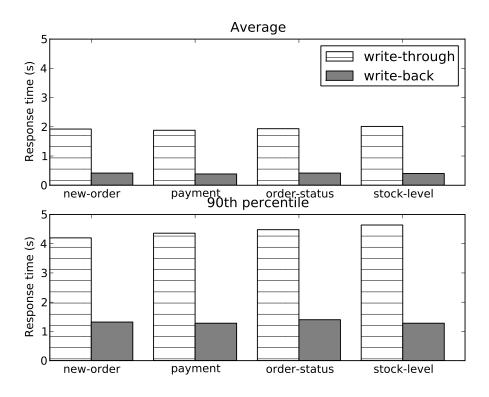

| 6.2 | Transaction response times for TPC-C using 1GB of RAM, 10 ware-<br>houses and 10 clients.                                                                                                                                                                                                                                                             | 85 |

| 6.3 | Dependency graph. Each node represents a write                                                                                                                                                                                                                                                                                                        | 86 |

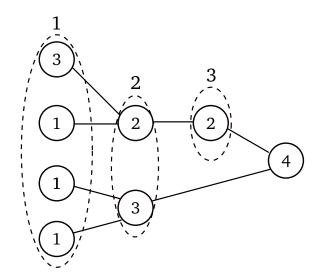

| 6.4 | Technique used to reduce the amount of memory used for maintaining dependencies.                                                                                                                                                                                                                                                                      | 88 |

| 6.5 | Eviction of node 1 requires the parallel eviction of nodes in set 1, then set 2, and finally set 3                                                                                                                                                                                                                                                    | 89 |

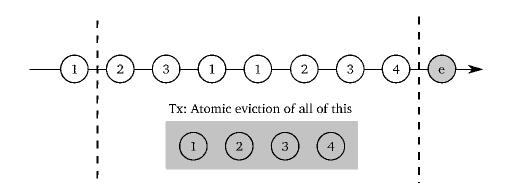

| 6.6 | Use of a journal for eviction of a list of blocks.                                                                                                                                                                                                                                                                                                    | 90 |

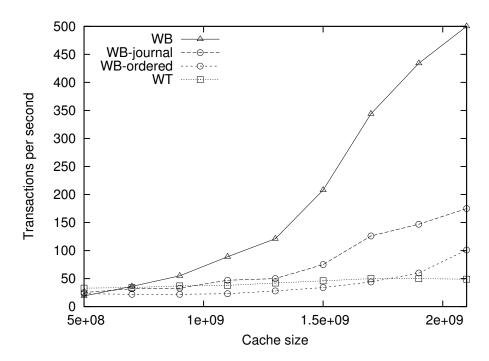

| 6.7 | Number of transactions per second at different cache sizes for all four write policies                         | 95 |

|-----|----------------------------------------------------------------------------------------------------------------|----|

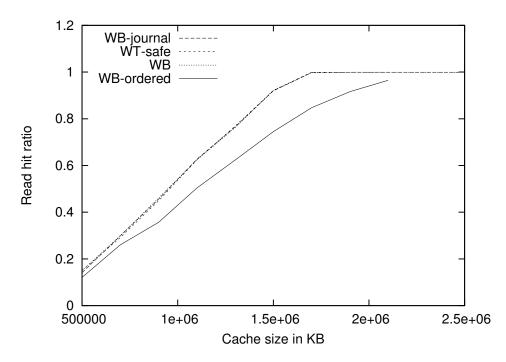

| 6.8 | Hit ratio of Postmark reads as we increase the size of the cache for all four write policies                   | 96 |

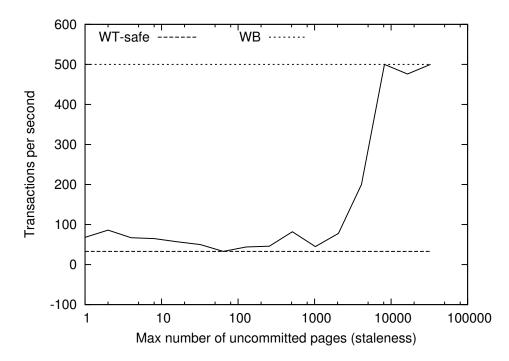

| 6.9 | Postmark performance with 2.1GB of SSD cache for varying staleness<br>set as the maximum number of dirty pages | 97 |

#### CHAPTER 1

# INTRODUCTION

Memory (CPU caches, DRAM, and disk) has become one of the most important design issues of most microprocessors and operating systems, and according to some authors the only important issue [JNW08, Sit96, McK04]. This is due to the ever increasing gap between processor and memory speeds. If the memory system does not provide timely data access to the processor, then processors are kept waiting, doing nothing. Most research has been done on improving processors speeds and to better tolerate slow memory systems. However, for most systems, memory is still a bottleneck and regardless of the processor speed, if the memory is slower, then the processor optimizations are both futile and expensive (both in terms of monetary and energy cost) [Jac09].

Ideally, computers would have a processor reading all of its data and instructions from a flat memory device that matches the processor speed. One such memory device is Static Random Access Memory (SRAM). Building a computer where all data and instructions are stored on SRAM and fetched directly from it to the processor would solve the performance bottleneck and would be a very simple and elegant solution. However, a computer built this way could cost approximately from hundred thousand to 10 million dollars<sup>1</sup>. Consequently, hardware manufacturers have sacrificed performance to achieve a lower price at a very good trade-off: minimal performance impact for huge price reductions.

There are many types of memory, all of them store information using some special physical property: disks use magnetism and semiconductor memories use electricity. These memories offer specific trade-offs between cost, capacity, and speed of access. For example, disks are cheap, large, and slow; and semiconductor memories

$<sup>^{1}100 \</sup>text{ GB}$  at roughly 1 to 100 \$ per MB [JNW08]

like SRAM are expensive, small, and fast. Computers have evolved into using a combination of many memory types and are now able to store terabytes of data at the cost of the cheapest memory type while achieving speeds close to the speed of the fastest memory type.

Computer manufacturers are capable of achieving high speed at low price due to one crucial engineering concept: *caches*. A cache is a small piece of fast memory that stores popular data so it can be accessed faster. Caches are designed to take advantage of a general phenomenon seen in applications' data and instructions: temporal locality. This phenomenon states that if data is accessed, it is very likely that it will be accessed again in the near future. Therefore, if a cache stores the data recently and frequently used in the past, it is very likely that cached data will be used again. By doing this, memory systems are able to efficiently use small, fast, and expensive caches for large terabytes of cheap memory storage.

Modern computers use the idea of caching in a hierarchy: there are several levels of memory and a memory level is a cache for a larger and slower memory level immediately below it. We now examine the most commonly used memory hierarchy. The first level is the processor which is supplied data and instructions from memory levels in the following order: CPU caches, main memory, and disk.

The access time of a level compared to the one immediately below is 10 to 1000 times smaller. That means that if the cache is unable to store data that is going to be used next, then the processor has to wait 10 to 1000 times more until it is retrieved from the level below. Sometimes, data can even be across a wide-area-network and accessing it can take several seconds, or data cached could be the result of a very lengthy computation. Therefore the cost of re-fetching the data or perform the slow computation again is too high: there is limited space and the cost of a cache miss is too high. Therefore, special care needs to be taken in choosing which blocks to store in caches at any time. Surprisingly, caches at all levels choose data to store based on policies that have not changed much in principle for decades. For instance, CPU and buffer caches are still managed using the Least Recently Used (LRU) policy introduced thirty years ago [Car81].

Since the introduction of policies like LRU, computing has changed radically, with the biggest change being that nowadays caches are shared across hundreds or thousands of simultaneous workloads. This change has introduced three problems:

- Duplicated content in caches. Having more workloads increase the chances of having blocks of data with the exact same content at the same cache level. This can waste precious cache space at all levels.

- Unknown cache requirements. In order to meet the performance goals of applications, users need to provision cache space for each workload sharing the cache with other workloads. For this, a precise estimation of usage across all levels of the memory hierarchy becomes necessary. Existing techniques for cache estimation have severe drawbacks when used for consolidated caches.

- Contention for shared caches. We observed experimentally that caches managed with traditional unified cache replacement policies can lead to wasted space, and that this wastage increases linearly with the number of workloads.

The second big change in computing paradigms is that nowadays caching is being employed at new levels of the storage hierarchy due to the availability of high-performance flash-based persistent media. Write-policies are not capable of providing both performance and consistency guarantees.

We believe that these are significant problems and that solving them have the potential of further bridging the gap between processor and memory system speeds. Additionally, by modeling a workload's behavior and requirements in terms of cache space we can make systems more predictable and workloads truly isolated.

This thesis makes the following contributions.

- 1. A technique to eliminate duplicated content from caches and use this new space for other data, therefore improving performance.

- 2. A generalized and unified model for applications' cache requirements across the memory hierarchy. Additionally, we model the effect of sharing a cache for several applications.

- 3. A technique to reduce wastage in shared caches. Previous research on partitioning only applies to CPU and buffer caches [SRD04, GJMT03]. We propose a generalized partitioning method applicable to any cache in the memory hierarchy. And finally.

- 4. A technique to improve the consistency guarantees of write-back caches while preserving their performance benefits.

The remaining chapters of this thesis are organized as follows. In chapter 2, we state the thesis contributions and significance. Chapter 3 is a description of the technique to eliminate duplication from caches. In chapter 4, we present the generalized and unified model for cache requirements. Chapter 5 describes the partitioning technique to reduce contention. In chapter 6, we show the design and implementation of the write policies capable of achieving performance and consistency guarantees. And finally, in chapters 7 and 8 we present related and future work.

#### CHAPTER 2

## THESIS OVERVIEW

In this chapter we state the contributions and significance of this thesis.

# 2.1 Thesis Statement

We propose improving the state-of-the-art in caching by:

- 1. reducing duplication in data content to improve caching efficiency,

- 2. modeling applications' cache usage across the memory hierarchy and the effect of contention when they are shared,

- 3. solving the cache contention problem through cache partitioning and isolation of workloads, and

- 4. achieving consistency guarantees for file systems, while achieving performance comparable to write-back caches, at the cost of controlled staleness.

## 2.2 Thesis Contributions

Recent trends in computing have increased the number of workloads sharing caches. One such trends is the use of virtualization by which several virtual machines themselves often running hundreds of processes are consolidated into the same physical machines, and therefore sharing all the CPU caches and the main memory used as cache for disk. In this thesis we model the effects of such consolidation and propose solutions to improve hit ratios of caches, improve performance, and ultimately reduce cost. We propose three specific contributions.

The first contribution is to study the amount of duplicated content present in consolidated buffer caches (RAM caches for disk) and find ways of using it for improving cache hit-rates. We studied duplication of data in the I/O path at the RAM buffer caches for disk data through the use of production traces. We found that there is a substantial amount of duplicated data being cached, and that same content data is accessed more frequently than the same data location. These two observations then motivated the construction of a *content addressed cache* which provides higher hit-rates than traditional location addressed caches. We present the design and evaluation of this system in Section 3.

The second contribution is the creation of application cache usage models across the entire memory hierarchy and being able to predict the resulting effect on performance when a set of applications contend for caches. We introduce the concept of Effective Reuse Set Size (ERSS) Tree as the basis for the modeling in Section 4. We then study methods for measuring and modeling it across all levels of the memory hierarchy. We specifically develop methods for measuring ERSS for CPU, RAM, and external memory caches. The main focus of study is related to the adverse effect that consolidation has on caches at any level of the memory hierarchy. We analytically prove certain properties of cache replacement policies such as cache wastage being greater or equal than zero regardless of the replacement policy used.

The third contribution addresses the reduction of cache space wastage because of cache sharing. Several researchers have proposed partitioning caches in order to reduce wastage. However, the partitioning methods proposed in the literature make assumptions only applicable to the first levels of the memory hierarchy: CPU and RAM caches. We found that most of these assumptions and related methods have large errors when applied to external memory caches. In chapter 5 we propose a partitioning method for Solid State Drives (SSD) caches (a type of external memory cache). Additionally, in chapter 6 we present two write-policies capable of providing consistency guarantees while still performing similarly to write-back, this at the cost of controlled staleness.

## 2.3 Thesis Significance

### 2.3.1 Using data de-duplication to improve caching efficiency

We observed that the amount of duplicated data in shared buffer caches is such that removing it can boost applications' performance by 10% to 4x when compared to conventional location-addressed caches. This is because by removing duplicates and having the cache addressed by content we can make space for other cached data which would otherwise miss the cache.

The impact of this for applications and users is that they can get an increase in performance without augmenting the size of the cache. A nice property of using a content-addressed cache is that miss rates will always be lower or equal than location-addressed caches: the same content can be in more than one location, but not vice versa. And because running many workloads on the same machine is more the norm than an exception, it is very likely that for most systems, same content resides in more than one location. Therefore, we expect performance gains for the majority of systems.

## 2.3.2 Modeling cache usage

An application requires resources at various memory levels in order to meet its performance objective. Administrators are constantly provisioning resources for applications and need accurate information about their requirements to do this well. One such resource is memory, which translates to memory requirements at all levels of the hierarchy. Not meeting cache requirements can lead to substantial performance degradation. For example, Verma *et al.* have observed a performance impact of up to a factor of 4 due to CPU-cache-unaware allocations for many HPC applications [VAN08b]. Further, memory provisioning needs to deal with the problem of multiple applications contending for shared levels of the memory hierarchy. We observed that this contention can result in a large amount of wasted cache space. We propose including this in the memory models by accurately characterizing the amount of cache resources required by each application including the over-provisioning required to address contention and ensure performance isolation between the applications.

# 2.3.3 Reducing cache contention

Server consolidation (e.g. via virtualization) is gaining acceptance as the solution to overcome server sprawl by replacing many low utilization servers with a few highly utilized servers. However, contention for the memory system can be a source of unexpected impact to an application's performance due to consolidation. We noticed that the source of this performance impact is some wasted space allocated in the caches that is not usable by any workload. We additionally observed that this wasted space increases linearly with the number of workloads, and that it exists for any cache replacement policy.

This problem was not serious thirty years ago, but in current over-consolidated scenarios where thousands of applications are sharing the same caches, this wasted space can be as big as the cache required by one of the applications contending for cache space. By managing caches more efficiently, we would have space to host one or more additional applications per host thereby reducing costs. Our proposed approach to cache partitioning eliminates wasted space in caches entirely.

#### 2.3.4 Guaranteeing consistency in write-back policies

There are two types of write-policies for caches: write-back and write-through. Write-back is a policy optimized for write accesses, which does not provide any guarantee of consistency. Write-through, on the other hand, does not optimize writes, and therefore performs worse than write-back for some workloads. It does, at least, provide full guarantees of data consistency.

Modern computers use write-back caches for most of the memory hierarchy: CPU caches and RAM [Int09, LSB08]. In contrast, SSD caches typically use writethrough caches because they are placed below file systems which already guarantee some form of consistency. The problem with using write-through caches is that we observed that for some transactional workloads, write-back caches allow the applications to achieve 8 times more transactions per second. Our proposed solution achieves performance comparable to write-back with some consistency guarantees by controlling a third dimension of cache behavior: staleness.

#### CHAPTER 3

# CONTENT ADDRESSED CACHING

In this chapter, we present a storage optimization that utilizes content similarity for improving performance by eliminating duplicated content in caches. This technique is motivated by our observations with I/O workload traces obtained from activelyused production storage systems, all of which revealed surprisingly high levels of content similarity for both stored and accessed data.

Duplication of data in primary storage systems is quite common due to the technological trends that have been driving storage capacity consolidation. The elimination of duplicate content at both the file and block levels for improving storage space utilization is an active area of research [CAVL09, JDT05, KDLT04, LEB<sup>+</sup>09, QD02, RCP08, ZLP08]. Indeed, eliminating most duplicate content is inevitable in capacity-sensitive applications such as archival storage for cost-effectiveness. On the other hand, there exist systems with moderate degree of content similarity in their primary storage such as email servers, virtualized servers, and NAS devices running file and version control servers. In case of email servers, mailing lists, circulated attachments and SPAM can lead to duplication. Virtual machines may run similar software and thus create co-located duplicate content across their virtual disks. Finally, file and version control systems servers of collaborative groups often store copies of the same documents, sources and executables. In such systems, if the degree of content similarity is not overwhelming, eliminating duplicate data may not be a primary concern.

Gray and Shenoy have pointed out that given the technology trends for pricecapacity and price-performance of memory/disk sizes and disk accesses respectively, disk data must "cool" at the rate of 10X per decade [GS00]. They suggest data replication as a means to this end. An instantiation of this suggestion is *intrinsic*  replication of data created due to consolidation as seen now in many storage systems, including the ones illustrated earlier. Here, we refer to intrinsic (or application/user generated) data replication as opposed to forced (system generated) redundancy such as in a RAID-1 storage system. In such systems, capacity constraints are invariably secondary to I/O performance.

We analyzed on-disk duplication of content and I/O traces obtained from three varied production systems at FIU that included a virtualized host running two department web-servers, the department email server, and a file server for our research group. We made three observations from the analysis of these traces. First, our analysis revealed significant levels of duplicate content in the storage medium and in the portion of the medium that is accessed by the I/O workload. We define these similarity measures formally in § 3.1. Second, we discovered a consistent and marked discrepancy between *reuse distances* [MGST70a] for sector and content in the I/O accesses on these systems indicating that content is reused more frequently than sectors. Third, there is significant overlap in content accessed over successive intervals of longer time-frames such as days or weeks.

Based on these observations, we explore the premise that intrinsic content similarity in storage systems and access to replicated content within I/O workloads can both be utilized to improve I/O performance. In doing so, we design and evaluate a storage optimization that utilizes content similarity to eliminate I/O operations altogether. The main mechanism is *content-addressed caching*, which uses the popularity of "data content" rather than "data location" of I/O accesses in making caching decisions.

We evaluated a Linux implementation of a content-addressed cache for workloads from the three systems described earlier. Performance improvements measured as the reduction in total disk busy time in the range 28-47% were observed across these workloads. Content-addressed caching increased memory caching effectiveness by at least 10% and by as much as 4X in cache hit rate for read operations.

We also measured the memory and CPU overheads and found these to be nominal.

In Section 3.1, we make the case for I/O deduplication. We elaborate on a specific design and implementation of its techniques in Section 3.2. We perform a detailed evaluation of improvements and overhead for three different workloads in Section 3.3. We discuss related research in Section 3.4, and finally conclude with directions for future work.

# 3.1 Motivation

In this section, we investigate the nature of content similarity and access to duplicate content using workloads from three production systems that are in active, daily use at the FIU Computer Science department. We collected I/O traces downstream of an active page cache from each system for a duration of three weeks. These systems have different I/O workloads that consist of a virtual machine running two web-servers (*web-vm* workload), an email server (*mail* workload), and a file server (*homes* workload). The *web-vm* workload is collected from a virtualized system that hosts two CS department web-servers, one hosting the department's online course management system and the other hosting the department's web-based email access portal; the local virtual disks which were traced only hosted root partitions containing the OS distribution, while the http data for these web-servers reside on a network-attached storage. The *mail* workload serves user INBOXes for the entire Computer Science department at FIU. Finally, the *homes* workload is that of a NFS server that serves the home directories of our small-sized research group; activities represent those of a typical researcher consisting of software development, testing, and experimentation, the use of graph-plotting software, and technical document preparation.

| Workload | File Sys. | Unique reads [GB] |         |         | Unique writes [GB] |         |         | File System |

|----------|-----------|-------------------|---------|---------|--------------------|---------|---------|-------------|

| type     | size [GB] | Total             | Sectors | Content | Total              | Sectors | Content | accessed    |

| web-vm   | 70        | 3.40              | 1.27    | 1.09    | 11.46              | 0.86    | 4.85    | 2.8%        |

| mail     | 500       | 62.00             | 29.24   | 28.82   | 482.10             | 4.18    | 34.02   | 6.27%       |

| homes    | 470       | 5.79              | 2.40    | 1.99    | 148.86             | 4.33    | 33.68   | 1.44%       |

Table 3.1: Summary statistics of one week I/O workload traces obtained from three different systems.

Key statistics related to these workloads are summarized in Table 3.1. The mail server is a heavily used system and generates a highly-intensive I/O workload in comparison to the other two. However, some uniform trends can be observed across these workloads. A fairly small percentage of the total file system data is accessed during the entire week (1.44-6.27% across the workloads), representing small working sets. Further, these are write-intensive workloads. While it is therefore important to optimize write I/O operations, we also note that most writes are committed to persistent storage in the background and do not affect user-perceived performance directly. Optimizing read operations, on the other hand, has a direct impact on user-perceived performance and system throughput because this reduces the waiting time for blocked foreground I/O operations. For read I/O's, we observe that in each workload, the unique content accessed is lesser than the unique locations that are accessed on the storage device. Notice that these are the unique number of content and sectors reads, not the total number of accesses. This is why the same content is accessed more than once and therefore unique sector reads are equal or higher than unique content reads. These observation directly motivates the three techniques of our approach as we elaborate next.

The systems of interest in our work are those in which there are patterns of work shared across more than one mechanism within a single system. A *mechanism*

Figure 3.1: Page cache hits for the web-vm (top), mail (middle), and homes (bottom) workloads. A single day trace was used with an infinite cache assumption.

represents any active entity, such as a single thread or process or an entire virtual machine. Such duplicated mechanisms also lead to intrinsic duplication in content accessed within the respective mechanisms' I/O operations. Duplicate content, however, may be independently managed by each mechanism and stored in distinct locations on a persistent store. In such systems, traditional storage-location (sector) addressed caching can lead to content duplication in the cache, thus reducing the effectiveness of the cache.

Figure 3.1 shows that cache hit ratio (for read requests) can be improved substantially by using a content-addressed cache instead of a sector-addressed one. Notice that this is a count of accesses to the same content or same sector, and not the total number of accesses. While write I/Os leading to content hits could be eliminated for improved performance, we do not explore them in this thesis. A greater number of sector hits with write I/Os are due to journaling writes by the file system,

Figure 3.2: Contrasting content and sector reuse distances for the web-vm (top), mail (middle), and homes (bottom) workloads.

repeatedly overwriting locations within a circular journal space.

For further analysis, we define the *average sector reuse distance* for a workload as the average number of requests between successive requests to the same sector. The *average content reuse distance* is defined similarly over accesses to the same content. Figure 3.2 shows that the average reuse distance for content is smaller than for sector for each of the three workloads that we studied for both read and write requests. For such workloads, data addressed by content can be cache-resident for lesser time yet be more effective for servicing read requests than if the same cached data is addressed by location. Write requests on the other hand do not depend on cache hits since data is flushed to rather than requested from the storage system. These observations and those from Figure 3.1 motivate *content-addressed caching*. In this section, we start with an overview of the system architecture and then present the various design choices and rationale behind constructing the content-address cache.

## 3.2.1 Architectural Overview

An optimization based on content similarity can be built at various layers of the storage stack, with varying degrees of access and control over storage devices and the I/O workload. Prior research has argued for building storage optimizations in the block layer of the storage stack [GUB+08]. We choose the block layer for several reasons. First, the block interface is a generic abstraction that is available in a variety of environments including operating system block device implementations, software RAID drivers, hardware RAID controllers, SAN (e.g., iSCSI) storage devices, and the increasingly popular storage virtualization solutions (e.g., IBM) SVC [IBM], EMC Invista [EMC], NetApp V-Series [Net]). Consequently, optimizations based on the block abstraction can potentially be ported and deployed across these varied platforms. In the rest of the chapter, we develop an operating system block device oriented design and implementation. Second, the simple semantics of block layer interface allows easy I/O interception, manipulation, and redirection. Third, by operating at the block layer, the optimization becomes independent of the file system implementation, and can support multiple instances and types of file systems. Fourth, this layer enables simplified control over system devices at the block device abstraction, allowing an elegantly simple implementation of selective duplication that we describe later. Finally, additional I/Os generated can leverage

Figure 3.3: System Architecture.

I/O scheduling services, thereby automatically addressing the complexities of block request merging and reordering.

Figure 3.3 presents the architecture of content-addressed caching for a block device in relation to the storage stack within an operating system. We augment the storage stack's block layer with additional functionality, which we term the I/O dedup layer, to implement the three major mechanisms: the content-addressed cache, the dynamic replica retriever, and the selective duplicator. The content-addressed cache is the first mechanism encountered by the I/O workload, which filters the I/O stream based on hits in a content-addressed cache. The dynamic replica retriever subsequently optionally redirects the unfiltered read I/O requests to alternate locations on the disk to avail the best access latencies to requests. The selective duplicator is composed of a kernel sub-component that tracks content accesses to create a candidate list of content for replication, and a user-space process that runs during periods of low disk activity and populates replica content in scratch space distributed across the entire disk. Thus, while the kernel components run

Figure 3.4: Data structure for the content-addressed cache. The cache is addressable by both sector and content-hash. vc\_entries are unique per sector. Solid lines between vc\_entries indicate that they may have the same content (they may not in case of hash function collisions.) Dotted lines form a link between a sector (vc\_entry) and a given page (vc\_page.) Note that some vc\_entries do not point to any page – there is no cached content for these entries. However, this indicates that the linked vc\_entries have the same data on disk. This happens when some of the pages are evicted from the cache. Additionally, pages form an LRU list.

continuously, the user-space component runs sporadically. Separating out the actual replication process into a user-level thread allows greater user/administrator control over the timing and resource consumption of the replication process, an I/O resource-intensive operation. Next, we elaborate on the design of the content addressed caching mechanism.

#### 3.2.2 Content addressed caching

Building a content-addressed cache at the block layer creates an additional buffer cache separate from the virtual file system (VFS) cache. Requests to the VFS cache are sector-based while those to the content-addressed cache cache are both sector- and content-addressed. The content-addressed cache layer only sees the read requests for sector misses in the VFS cache. We discuss exclusivity across these caches shortly. In the content-addressed cache layer, read requests identified by sector locations are queried against a dual sector- and content-addressed cache for hits before entering the I/O scheduler queue or being merged with an existing request by the I/O scheduler. Population of the content-addressed cache occurs along both the read and write paths. In case of a cache miss during a read operation, the I/Ocompletion handler for the read request is intercepted and modified to additionally insert the data read into the content-addressed cache after I/O completion only if it is not already present in the cache and is important enough in the LRU list to be cached. A write request to a sector which had contained duplicate data is simply removed from the corresponding duplicate sector list to ensure data consistency for future accesses. The new data contained within write requests is optionally inserted into the content-addressed cache (if it is sufficiently important) in the onward path before entering the request into the I/O scheduler queue to keep the content cache up-to-date with important data.

The in-memory data structure implementing the content-addressed cache supports look-up based on both sector and content-hash to address read and write requests respectively. Entries indexed by content-hash values contain a sector list (list of sectors in which the content is replicated) and the corresponding data if it was entered into the cache and not replaced. Cache replacement only replaces the content field and retains the sector-list in the in-memory content-cache data structure. For read requests, a sector-based lookup is first performed to determine if there is a cache hit. For write requests, a content-hash based look-up is performed to determine a hit and the sector information from the write request is added to the sector-list. Figure 3.4 describes the data structure used to manage the contentaddressed cache. A write to a sector that is present in a sector-list indexed by content-hash is simply removed from the sector list and inserted into a new list based on the sector's new content hash. It is important to also point out that our design uses a write-through cache to preserve the semantics of the block layer. Ideally, writes hits should dirty the page to be later flushed out to disk by a background process (i.e. pdflush for Linux). However, this current design uses a write-through cache. The main reason is that by having this type of cache, the semantics of writes below the block layer do not change: writes are not postponed. Additionally, the content addressed-cache can be dynamically removed at any time without any delay or inconsistency. Next, we discuss some practical considerations for our design.

Since the content cache is a second-level cache placed below the file system page cache or, in case of a virtualized environment, within the virtualization mechanism, typically observed recency patterns in first level caches are lost at this caching layer. An appropriate replacement algorithm for this cache level is therefore one that captures frequency as well. We propose using Adaptive Replacement Cache (ARC) [MM04] or CLOCK-Pro [JCZ05] as good candidates for a second-level content-addressed cache and evaluate our system with ARC and LRU for contrast.

Another concern is that there can be a substantial amount of duplicated content across the cache levels. There are two ways to address this. Ideally, the contentaddressed cache should be integrated into a higher level cache (e.g., VFS page cache) implementation, if possible. However, this might not be feasible in virtualized environments where page caches are managed independently within individual virtual machines. In such cases, techniques that help make in-memory cache content across cache levels exclusive such as cache hints  $[LAS^+05]$ , demotions [WW02a], and promotions [Gil08] may be used. An alternate approach is to employ memory deduplication techniques such as those proposed in the VMware ESX server [Wal02a], Difference Engine  $[GLV^+08]$ , and Satori [MMHF09]. In these solutions, duplicate pages within and across virtual machines are made to point to the same machine frame with use of an extra level of indirection, such as the shadow page tables. In memory, duplicate content across multiple levels of caches is indeed an orthogonal problem, and any of the referenced techniques could be used as a solution directly within content-addressed caching.

## 3.2.3 Persistence of metadata

A final issue is the persistence of the in-memory data structure so that the system can retain intelligence about content similarity across system restart operations. Persistence is important for retaining the locations of on-disk intrinsic and artificially created duplicate content so that this information can be restored and used immediately upon a system restart event. We note that while persistence is useful to retain intelligence that is acquired over a period of time, "continuous persistence" of metadata in a content-addressed cache is not necessary to guarantee the reliability of the system, unlike other systems such as the eager writing disk array [ZYKW02] or doubly distorted mirroring [OS93]. In this sense, *selective duplication* is similar to the opportunistic replication as performed by FS2 [HHS05] because it tracks updates to replicated data in memory and only guarantees that the primary copy of data blocks are up-to-date at any time. While persistence of the in-memory data is not implemented in our prototype yet, guaranteeing such persistence is relatively straightforward. Before the content-addressed cache kernel module is unloaded (occurring at the same time the managed file system is unmounted), all in-memory data structure entries can be written to a reserved location of the managed scratch-space. These can then be read back to populate the in-memory metadata upon a system restart operation when the kernel module is loaded into the operating system.

#### 3.3 Experimental Evaluation

In this section, we evaluate the performance impact of using a content-addressed cache. We also evaluate the CPU and memory overhead incurred by an contentaddressed cache. We used the block level traces for the three systems that were described in detail in § 3.1 for our evaluation. The traces were replayed as block traces in a similar way as done by blktrace [Axb07]. Blktrace could not be used as-is since it does not record content information; we used a custom Linux kernel module to record content-hashes for each block read/written in addition to other attributes of each I/O request. Additionally, the blktrace tool btreplay was modified to include traces in our format and replay them using provided content. Replay was performed at a maximum acceleration of 100x, with care being taken in each case to ensure that block access patterns were not modified as a result of the speedup. Measurements for actual disk I/O times were obtained with per-request block-level I/O tracing using blktrace and the results reported by it. Finally, all trace playback experiments were performed on a single Intel(R) Pentium(R) 4 CPU 2.00GHz machine with 1 GB of memory and a Western Digital disk WD5000AAKB-00YSA0 running Ubuntu Linux 8.04 with kernel 2.6.20.

Figure 3.5: Per-day page cache hit ratio for content- and sector- addressed caches for read operations. The total number of pages read are 0.18, 2.3, and 0.23 million respectively for the web-vm, mail and homes workloads. The numbers in the legend next to each type of addressing represent the cache size.

## 3.3.1 Evaluating performance

In our first experiment, we evaluated the effectiveness of a content-addressed cache against a sector-addressed one. The primary difference in implementation between the two is that for the sector-addressed cache, the same content for two distinct sectors will be stored twice. We fixed the cache size in both variants to one of two different sizes, 1000 pages (4MB) and 50000 pages (200MB). We replayed two weeks of the traces for each of the three workloads; the first week warmed up the cache and measurements were taken during the second week. Figure 3.5 shows the average per-day cache hit counts for read I/O operations during the second week when using an *adaptive replacement cache* (ARC) in two modes, content and sector addressed.

This experiment shows that there is a large increase in per-day cache hit counts for the web and the home workloads when a content-addressed cache is used (relative to a sector-addressed cache). The first observation is that improvement trends are consistent across the two cache sizes. Both cache implementations benefit substantially from a larger cache size except for the *mail* workload, indicating that *mail* is not a cache-friendly workload validated by its substantially larger working set and workload I/O intensity (as observed in Section 3.1). The *web-vm* workload

Figure 3.6: Comparison of ARC and LRU content-addressed caches for pages read only (top) and pages read/write operations (bottom). A single day trace (0.18 million page reads and 2.09 million page read/writes) of the web workload was used as the workload.

shows the biggest increase with an almost 10X increase in cache hits with a cache of 200MB compared to the home workload which has an increase of 4X. The *mail* workload has the least improvement of approximately 10%.

We performed additional experiments to compare an LRU implementation with the ARC cache implementation (used in the previous experiments) using a single day trace of the *web-vm* workload. Figure 3.6 provides a performance comparison of both replacement algorithms when used for a content-addressed cache. For small and large cache sizes, we observe that ARC is either as good or more effective than LRU with ARC's improvement over LRU increasing substantially for write operations at small to moderate cache sizes. More generally, this experiment suggests that the performance improvements for a content-addressed cache are sensitive to the cache replacement mechanism, which should be chosen with care.

Figure 3.7: Overhead of content and sector lookup operations with increasing size of the content-addressed cache.

#### 3.3.2 Evaluating Overhead

While the gains due to addressing a cache by content are promising, it incurs resource overhead. Specifically, the implementation uses content- and sector- addressed hashtables to simplify lookup and insert operations into the content-addressed cache. We evaluate the CPU overhead for insert/lookup operations and memory overhead required for managing hash-table metadata.

# **CPU** Overhead

To evaluate the overhead, we measured the average number of CPU cycles required for lookup/insert operations as we vary the number of unique pages (i.e., size) in the content-addressed cache (i.e., cache size) for a day of the *web* workload. Figure 3.8 depicts these overheads for two cache configurations, one configured with  $2^{25}$  buckets in the hash tables and the other with  $2^5$  buckets. Read operations perform a sector lookup and additionally content lookup in case of a miss for insertion. Write operations always perform a sector and content lookup due to our write-through cache design. Content lookups need to first compute the hash for the page contents which takes around 100K CPU cycles for MD5. With few buckets  $(2^5)$  lookup times approach O(N) where N is the size of the hash-table. However,

Figure 3.8: Overhead of sector and content lookup operations with increasing hash-table bucket entries.

given enough hash-table buckets  $(2^{25})$ , lookup times are O(1).

Next, we examined the sensitivity to the hash-table bucket entries. As the number of buckets are increased, the lookup times decrease as expected due to reduction in collisions, but beyond  $2^{20}$  buckets, there is an increase. We attribute this to L2 cache and TLB misses due to memory fragmentation, under-scoring that hash-table bucket sizes should be configured with care. In the sweet spot of bucket entries, the lookup overhead for both sector and content reduces to 1K CPU cycles or less than  $1\mu$ s for our 2GHz machine. Note that the content lookup operation includes a hash computation, which inflates its cycles requirement by at least 100K.

#### Memory Overhead

The management of a content-addressed cache introduces memory overhead for managing metadata for the content-addressed cache. Specifically, the memory overhead is dictated by the size of the cache measured in pages (P), the degree of *workload static similarity* (WSS), and the configured number of buckets in the hash tables (HTB), which also determine the lookup time, as we saw earlier. WSS is defined as the average number of copies per block accessed by the I/O workload. In our current unoptimized implementation, the memory overhead in bytes (assuming 4 byte pointers and 4096 byte pages) :

# mem(P, WSS, HTB) = 13 \* P + 36 \* P \* WSS + 8 \* HTB

These overheads include 13 bytes per-page to store the metadata for a specific page content ( $vc\_page$ ), 36 bytes per page per duplicated entry ( $vc\_entry$ ), and 8 bytes per hash-table entry for the corresponding linked list. For a 1GB content cache (256K pages), a static similarity of 4, and a hash-table of size 1 million entries, the metadata overhead is ~48MB or approximately 4.6%.

#### 3.4 Related work

Content similarity in both memory and archival storage have been investigated in the literature. Memory deduplication has been explored before in the VM ware ESX server [Wal02a], Difference Engine [GLV<sup>+</sup>08], and Satori [MMHF09], each aiming to eliminate duplicate in-memory content both within and across virtual machines sharing a physical host. Of these, Satori has apparent similarities to our work because it identifies candidates for in-memory deduplication as data is read from storage. Satori runs in two modes: content-based sharing and copy-on-write disk sharing. For content-based sharing, Satori uses content-hashes to track page contents in memory read from disk. Since its goal is not I/O performance optimization, it does not track duplicate sectors on disk and therefore does not eliminate duplicated I/Os that would read the same content from multiple locations. In copy-on-write disk sharing, the disk is already configured to be copy-on-write enabling the sharing of multiple VM disk images on storage. In this mode, duplicated I/Os due to multiple VMs retrieving the same sectors on the shared physical disk would be eliminated in the same way as a regular sector-addressed cache would do. In contrast, our work eliminates duplicated I/Os by retrieving their content irrespective of where they

reside on storage. Additionally, our work improves I/O performance by reducing head movement. Thus, the contributions of Satori are complementary to our work and can be used simultaneously.

Data deduplication in archival storage has also gained importance in both the research and industry communities. Current research on data deduplication uses several techniques to optimize the I/O overheads incurred due to data duplication. Venti |QD02| proposed by Quinlan and Dorward was the first to propose the use of a content-addressed storage for performing data deduplication in an archival system. The authors suggested the use of an in-memory content-addressed index of data to speed up lookups for duplicate content. Similar content-addressed caches were used in data backup solutions such as Peabody [MIG03] and Foundation [RCP08]. Content-addressed caching is inspired by these works. Recent work by Zhu and his colleagues [ZLP08] suggests new approaches to alleviate the disk bottleneck via the use of Bloom filters [Blo70] and by further accounting for locality in the content stream. The Foundation work suggests additional optimizations using batched retrieval and flushing of index entries and a log-based approach to writing data and index entries to utilize temporal locality [RCP08]. The work on sparse indexing  $[LEB^+09]$  suggests improvements to Zhu *et al.*'s general approach by exploiting locality in the chunk index lookup operations to further mitigate the disk I/O bottleneck. Content-addressed caching addresses an orthogonal problem, that of improving I/O performance for foreground I/O workload based on the use of duplicates, rather than their elimination. Nevertheless, the above approaches do suggest interesting techniques to optimize the management of a content-addressed index and cache in main-memory that is complementary to and can be used directly within content-addressed caching.

#### 3.5 Summary

System and storage consolidation trends are driving increased duplication of data within storage systems. Past efforts have been primarily directed towards the elimination of such duplication for improving storage capacity utilization. With content-addressed caching, we take a contrary view that intrinsic duplication in a class of systems which are not capacity-bound can be effectively utilized to improve I/O performance – the traditional Achilles' heel for storage systems. The content-addressed caching mechanism increased memory caching effectiveness by increasing cache hit rates by 10% to 4x for read operations when compared to traditional sector-addressed caching.

The work presented in this chapter was reported in ACM Transactions in Storage 2010 [KR10].

As said before, consolidation brings two big problems: data duplication and cache contention. In this chapter we observed that the first problem, can be used as an opportunity to improve performance. In the next chapter, we examine and address the problem of cache contention due to consolidation which introduces a large performance overhead which we could only model and minimize.

#### CHAPTER 4

# MODELING CACHE REQUIREMENTS AND CONTENTION

In order to meet the performance goals of applications, we need to provision cache space across the memory hierarchy. Existing techniques for cache estimation have severe drawbacks when used for consolidated environments. In this chapter, we present a unifying Generalized ERSS Tree Model that characterizes the resource usage at all levels of the memory hierarchy and accurately models the impact of sharing a cache with many workloads.

The ever-increasing gap between processing speed and disk bandwidth ensures that the allocation of resources at all levels of the memory hierarchy (henceforth also referred to simply as *memory levels*) significantly influence the performance of applications. The memory levels used by an application include on-chip caches (L1 and L2), off-chip caches (e.g., L3), DRAM, and other external memory caches (e.g., a flash-based disk cache [krm08]). Characterizing the resource utilization of an application at various memory levels has been an active research area over the years. While the consolidation of multiple applications on a shared hardware is not new, the rise of virtualization has made such systems more the norm than the exception. In virtualized systems, multiple applications run on the same physical server and compete for resources at all memory levels. For instance, it has been shown that contention in a shared cache can lead to performance degradation — as much as 47% [LLD<sup>+</sup>08] and 75% [VAN08b] depending on the workload. Contrast this problem with duplication (previous chapter's focus). Duplication can be used to boost I/O performance; contention on the other hand is more a problem than an opportunity.

An accurate characterization of the implications of this problem is a prerequisite to ensuring that all applications meet their performance goals [LLD<sup>+</sup>08, VAN08b, KRDZ10, VAN08a]. Specifically, there is a need for an accurate characterization of the resource requirement of resident applications within each virtual machine (VM), while carefully taking into account the impact of resource contention due to other applications.