## Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

4-23-2012

# A Hardware and Software Integrated Approach for Adaptive Thread Management in Multicore Multithreaded Microprocessors

Lichen Weng Florida International University, lichen.weng@fiu.edu

**DOI:** 10.25148/etd.FI12071106 Follow this and additional works at: https://digitalcommons.fiu.edu/etd

#### **Recommended** Citation

Weng, Lichen, "A Hardware and Software Integrated Approach for Adaptive Thread Management in Multicore Multithreaded Microprocessors" (2012). *FIU Electronic Theses and Dissertations*. 653. https://digitalcommons.fiu.edu/etd/653

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## A HARDWARE AND SOFTWARE INTEGRATED APPROACH FOR ADAPTIVE THREAD MANAGEMENT IN MULTICORE MULTITHREADED MICROPROCESSORS

A dissertation submitted in partial fulfillment of the

requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

#### ELECTRICAL ENGINEERING

by

Lichen Weng

2012

To: Dean Amir Mirmiran College of Engineering and Computing

This dissertation, written by Lichen Weng, and entitled A Hardware and Software Integrated Approach for Adaptive Thread Management in Multicore Multithreaded Microprocessors, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Malek Adjouadi

Gang Quan

Raju Rangaswami

Chen Liu, Major Professor

Date of Defense: April 23, 2012

The dissertation of Lichen Weng is approved.

Dean Amir Mirmiran College of Engineering and Computing

> Dean Lakshmi N. Reddi University Graduate School

Florida International University, 2012

© Copyright 2012 by Lichen Weng All rights reserved.

## DEDICATION

To my parents.

#### ACKNOWLEDGMENTS

First and foremost I offer my sincerest gratitude to my supervisor, Dr. Chen Liu, who has supported me throughout my doctoral study with his patience and knowledge. Dr. Liu has taught me in tremendous topics, which led me from a fresh graduate to a qualified doctor. Meanwhile, I attribute the level of my doctoral degree not only to my major professor, but also other committee members: Drs. Malek Adjouadi, Gang Quan and Raju Rangaswami. Without the valuable and great guidance from the committee, the dissertation would not have been completed.

Furthermore, honest appreciations are delivered to the faculty in the Department of Electrical and Computer Engineering, the School of Computing and Information Sciences and the Telecommunications and Information Technology Institute, for their inspiring teaching and informative lectures. I do honor the fine and prompt aid from the friendly staff in our department in various events.

Last but not least, I am absolutely grateful for the gorgeous help and constructive suggestions from my colleagues and friends. Especially in the Computer Architecture and Microprocessor Engineering Laboratory, we have had so much fun and so many fruitful collaborations.

## ABSTRACT OF THE DISSERTATION A HARDWARE AND SOFTWARE INTEGRATED APPROACH FOR ADAPTIVE THREAD MANAGEMENT IN MULTICORE MULTITHREADED MICROPROCESSORS

by

Lichen Weng

Florida International University, 2012

Miami, Florida

Professor Chen Liu, Major Professor

The Multicore Multithreaded Microprocessor maximizes parallelism on a chip for the optimal system performance, such that its popularity is growing rapidly in high-performance computing. It increases the complexity in resource distribution on a chip by leading it to two directions: isolation and unification. On one hand, multiple cores are implemented to deliver the computation and memory accessing resources to more than one thread at the same time. Nevertheless, it limits the threads' access to resources in different cores, even if extensively demanded. On the other hand, simultaneous multithreaded architectures unify the domestic execution resources together for concurrently running threads. In such an environment, threads are greatly affected by the inter-thread interference. Moreover, the impacts of the complicated distribution are enlarged by variation in workload behaviors. As a result, the microprocessor requires an adaptive management scheme to schedule threads throughout different cores and coordinate them within cores.

In this study, an adaptive thread management scheme was proposed, integrating both hardware and software approaches. The instruction fetch policy at the hardware level took the responsibility by prioritizing domestic threads, while the Operating System scheduler at the software level was used to pair threads dynamically to multiple cores. The tie between them was the proposed online linear model, which was dynamically constructed for every thread based on data misses by the regression algorithm. Consequently, the hardware part of the proposed scheme proactively granted higher priority to the threads with less predicted long-latency loads, expecting they would better utilize the shared execution resources. Meanwhile, the software part was invoked by such a model upon significant changes in the execution phases and paired threads with different demands to the same core to minimize competition on the chip. The proposed scheme was compared to its peer designs and overall 43% speedup was achieved by the integrated approach over the combination of two baseline policies in hardware and software, respectively. The overhead was examined carefully regarding power, area, storage and latency, as well as the relationship between the overhead and the performance.

### TABLE OF CONTENTS

| CHAPTER                                                                                                                                         | PAGE |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                                                                                                 | 1    |

| 1.1 The Motivation                                                                                                                              |      |

| 1.2     Scope of the Study                                                                                                                      |      |

| 1.3       Significance of the Study                                                                                                             |      |

| 1.4       The Dissertation Organization                                                                                                         |      |

|                                                                                                                                                 |      |

| 2. THEORETICAL PERSPECTIVE AND LITERATURE REVIEW                                                                                                | 8    |

| 2.1 Hardware Architecture of the MMMP                                                                                                           |      |

| 2.1.1 The SMT Architecture                                                                                                                      | 9    |

| 2.1.2 The Multicore Architecture                                                                                                                | 11   |

| 2.2 Scheduling in the SMT Architecture                                                                                                          | 12   |

| 2.2.1 The Long-Latency Load                                                                                                                     | 12   |

| 2.2.2 Instruction Fetch Policies for the LLC                                                                                                    |      |

| 2.2.3 Proactive Instruction Fetch Policies                                                                                                      | 14   |

| 2.2.4 More SMT Scheduling Policies                                                                                                              | 15   |

| 2.2.5 SMT Scheduling for Parallel Programmes                                                                                                    | 16   |

| 2.3 Multicore Scheduling in the OS                                                                                                              |      |

| 2.3.1 Homogeneous Microprocessors                                                                                                               |      |

| 2.3.2 Heterogenous Microprocessors                                                                                                              |      |

| 2.3.3 Allocation of Memory Resources                                                                                                            |      |

| 2.3.4 Scheduling Policies in Cluster                                                                                                            |      |

| 2.3.5 Thread Replacement                                                                                                                        |      |

| 2.4 The Shared Resources and Workload Behaviors                                                                                                 |      |

| 2.4.1 The Shared Resources                                                                                                                      | 24   |

| 2.4.2 Demands along Execution                                                                                                                   |      |

| 2.4.3 Demands among Workloads                                                                                                                   | 25   |

| 2.5 Summary of the Related Work                                                                                                                 |      |

| 2 THE ONLINE LINEAD MODEL                                                                                                                       | 28   |

| 3. THE ONLINE LINEAR MODEL                                                                                                                      |      |

| 3.1 The OLS Regression                                                                                                                          |      |

| 3.2 Construction of the OLM                                                                                                                     |      |

| 3.2.1The Sampling Module                                                                                                                        |      |

|                                                                                                                                                 |      |

| 3.3 Hardware Implementation $\dots \dots \dots$ |      |

| 3.3.1 The Sampling Engine                                                                                                                       |      |

| 3.3.2 The Regression Engine                                                                                                                     |      |

| 3.3.3 The Hardware Overhead                                                                                                                     |      |

| 3.4 Summary of the OLM                                                                                                                          | 37   |

| 4. THE REGRESSION-BASED ALGORITHM TO PRIORITIZE THREADS | 39       |

|---------------------------------------------------------|----------|

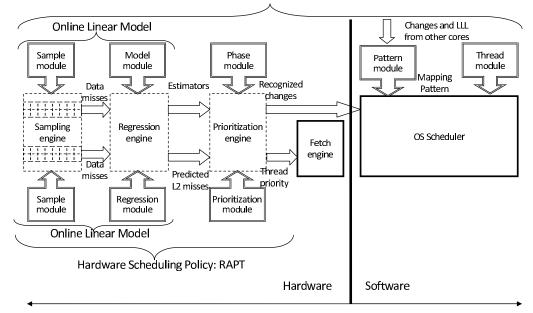

| 4.1 The Three-Module Design                             | 40       |

| 4.1.1 The Inherited Engines                             | 41       |

| 4.1.2 The Prioritization Engine                         | 42       |

| 4.2 Summary of the Hardware Overhead                    | 42       |

| 4.3 Experimental Methodology                            | 43       |

| 4.3.1 The Architectural Simulators                      | 44       |

| 4.3.2 The Workload Organization                         | 45       |

| 4.3.3 The Performance Measurement                       | 46       |

| 4.4 Experimental Results                                | 47       |

| 4.5 Implementation Details                              | 48       |

| 4.5.1 Performance Achievement                           | 50       |

| 4.5.2 Prediction Expectation of RAPT                    | 55       |

| 4.6 Sensitivity Analysis                                | 57       |

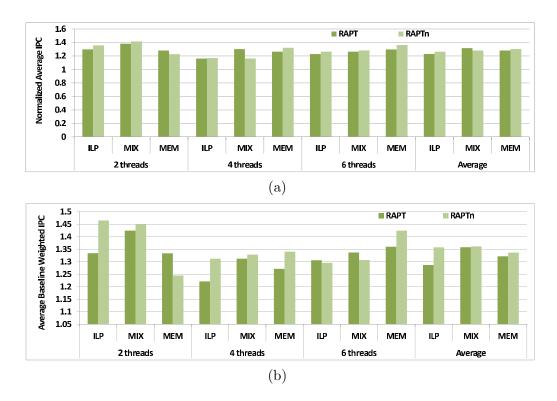

| 4.6.1 The Comparison between the RAPT and the RAPTn     | 57       |

| 4.6.2 The Algorithmic Configurations                    | 58       |

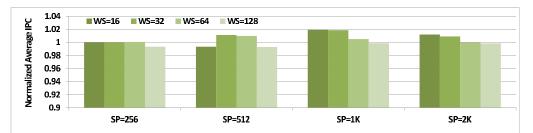

| 4.6.3 The Cache Configurations                          | 60       |

| 4.7 Summary of the RAPT                                 | 63       |

| 5. THE HARDWARE-ASSISTED SCHEDULING POLICY              | 65       |

| 5.1 Static Mix-Scheduling                               | 66       |

| 5.1.1 Experimental Methodology                          | 67       |

| 5.2 Dynamic Mix-Scheduling                              | 70       |

| 5.2.1 The sMIX and the dMIX                             | 70       |

| 5.2.1 The SMIX and the dMIX                             | 70<br>72 |

| 5.3 The Phase Triggered Scheduling Policy               | 73       |

| 5.3.1 The Sample Module                                 | 73<br>74 |

| 5.3.2 The Model Module                                  | 75       |

| 5.3.3 The Phase Module                                  | 76       |

| 5.3.4 The Pattern Module                                | 77       |

| 5.3.5 Performance Discussions                           | 80       |

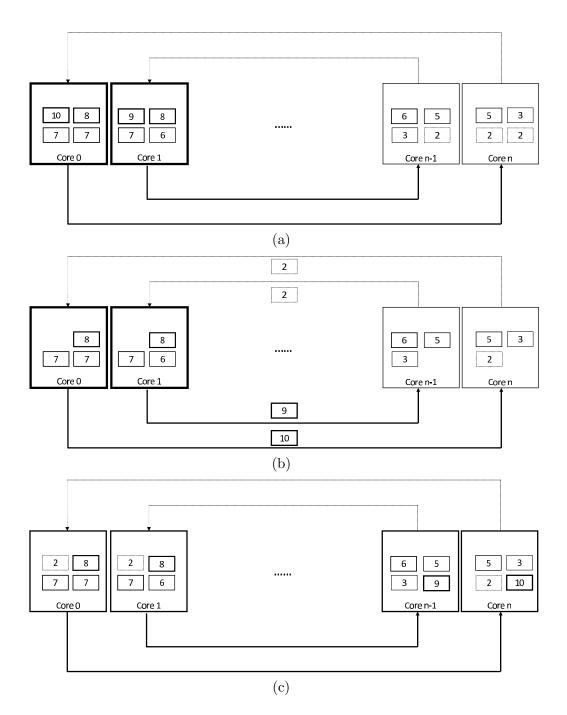

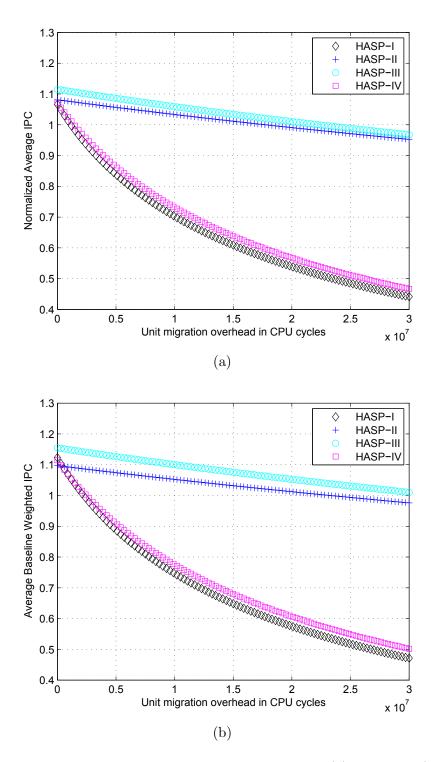

| 5.4 Scalability in the HASP                             | 86       |

| 5.4.1 Increasing Capacity                               | 86       |

| 5.4.2 Compromise to Scalability                         | 87       |

| 5.4.3 More Designs in the HASP                          | 89       |

| 5.4.4 Scheduling in Larger Systems                      | 89       |

| 5.5 Summary of the HASP                                 | 94       |

|                                                         |          |

| 6. THE ADAPTIVE THREAD MANAGEMENT SCHEME                | 95       |

| 6.1 Assembly of the ATMS                                | 96       |

| 6.1.1 Synchronization of the RAPT and the HASP          | 96       |

| 6.1.2 Summary of the ATMS                               |          |

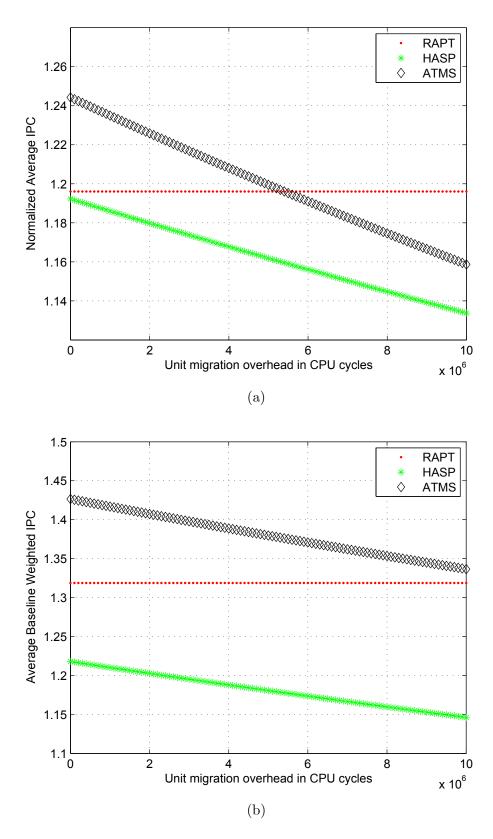

| 6.2 Performance Achievement                             | 100      |

| 7. CONCLUSION AND FUTURE WORK                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1 The Problems and Solutions                                                                                                                                                 |

| 7.2 The Proposed Policies $\dots \dots \dots$                                  |

| 7.2.1 Adaptability $\ldots \ldots \ldots$                      |

| 7.2.2 Integration $\dots \dots \dots$                                          |

| 7.2.3 Hardware Effectiveness                                                                                                                                                   |

| 7.2.4 Coordinated Hardware and Software $\ldots \ldots \ldots$ |

| 7.3 Future Work                                                                                                                                                                |

| BIBLIOGRAPHY                                                                                                                                                                   |

| VITA                                                                                                                                                                           |

| TAB | LE                                       | PA | GE |

|-----|------------------------------------------|----|----|

| 3.1 | Architecture units in Regression engine  |    | 34 |

| 3.2 | Storage for OLM                          |    | 35 |

| 3.3 | Latency in Regression engine             |    | 37 |

| 4.1 | Total RAPT overhead                      |    | 43 |

| 4.2 | The SPEC CPU2000 benchmarks employed     |    | 46 |

| 4.3 | The baseline parameters                  |    | 49 |

| 4.4 | The workloads in simulation              |    | 49 |

| 4.5 | The Average Variances of the IPCs        |    | 54 |

| 4.6 | The cache configurations                 |    | 61 |

| 5.1 | Threads scheduling in the Mix-Scheduling |    | 67 |

| 5.2 | Thread scheduling in the Mono-Scheduling |    | 68 |

| 5.3 | The objective in the dMIX                |    | 71 |

| 5.4 | The workloads in the dMIX                |    | 72 |

| 5.5 | The storage for the HASP                 |    | 75 |

| 5.6 | The adopted overheads in the HASP        |    | 81 |

| 5.7 | More workloads in the simulation         |    | 88 |

| 5.8 | Four derivatives of the HASP             |    | 90 |

| 6.1 | ATMS overhead                            |    | 99 |

## LIST OF TABLES

### LIST OF FIGURES

| FIGU | URE                                                | PAC | ΞE  |

|------|----------------------------------------------------|-----|-----|

| 2.1  | An MMMP Example                                    |     | 9   |

| 2.2  | The Horizontal and Vertical waste                  |     | 10  |

| 3.1  | The Online Linear Model of cache misses            |     | 31  |

| 4.1  | The RAPT Model                                     |     | 41  |

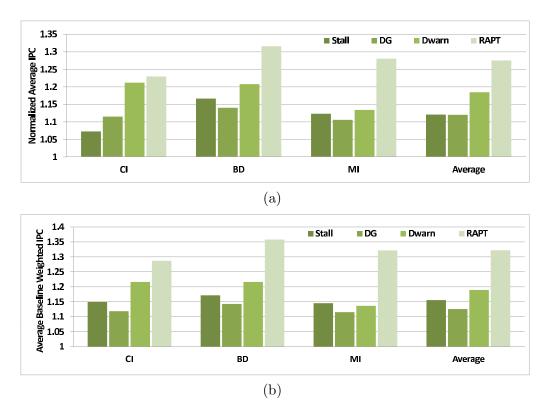

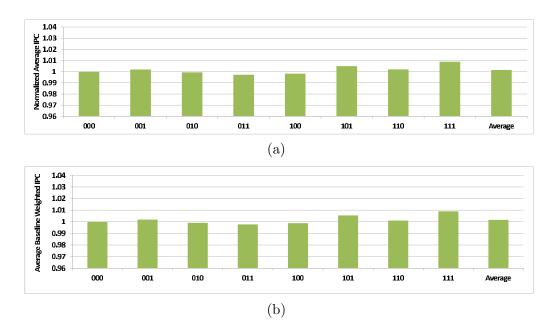

| 4.2  | The overall RAPT performance                       |     | 50  |

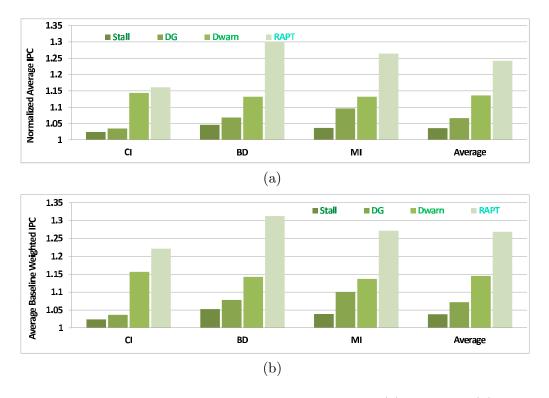

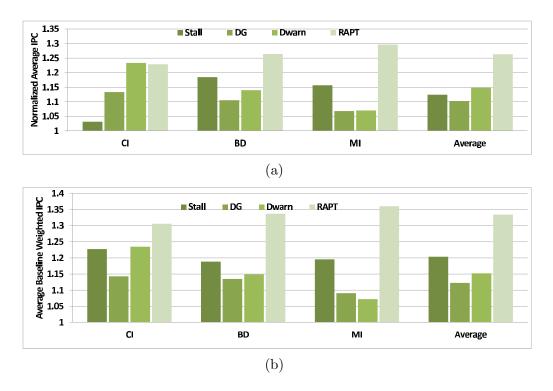

| 4.3  | The Two-threaded RAPT                              |     | 51  |

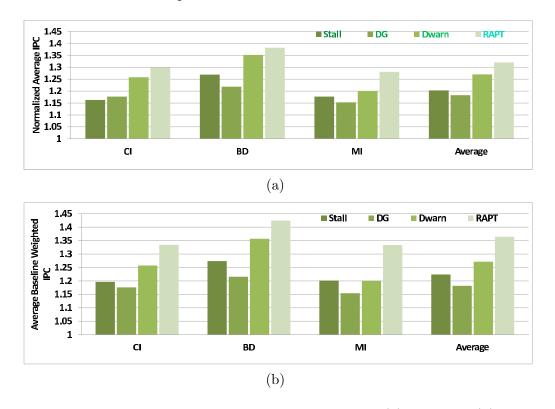

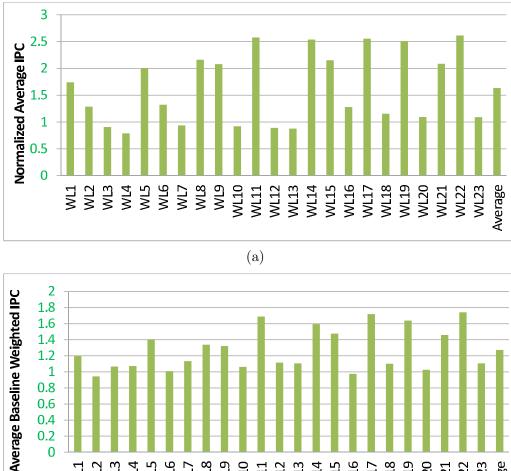

| 4.4  | The Four-threaded RAPT                             |     | 53  |

| 4.5  | The Six-threaded RAPT                              |     | 54  |

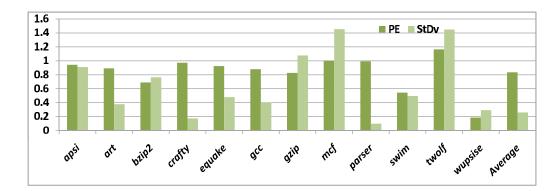

| 4.6  | The Prediction Expectation                         |     | 56  |

| 4.7  | The Difference between the RAPT and the RAPTn      |     | 59  |

| 4.8  | Performance of the RAPT with varying parameters    |     | 61  |

| 4.9  | Different performances in different configurations |     | 62  |

| 5.1  | Improvement in the sMIX over the Mono              |     | 69  |

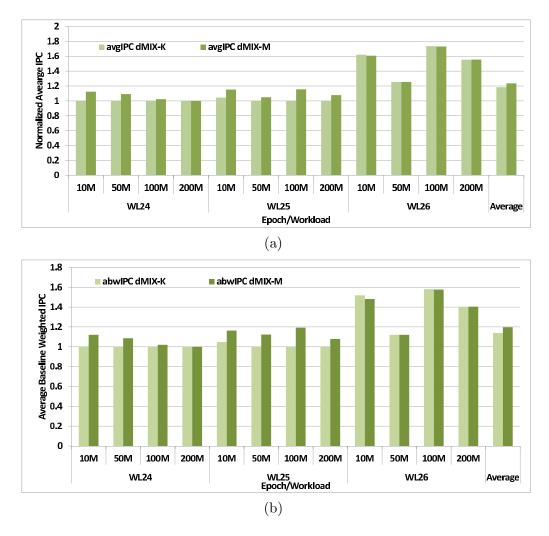

| 5.2  | Performance of the dMIX                            |     | 74  |

| 5.3  | The model indicates phase changes                  |     | 77  |

| 5.4  | The HASP Model                                     |     | 80  |

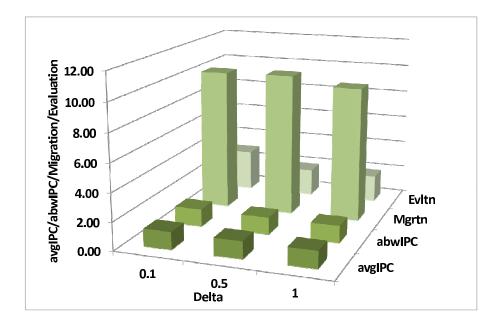

| 5.5  | Performance of the dynamic scheduling policies     |     | 83  |

| 5.6  | Delta defines overhead                             |     | 85  |

| 5.7  | Scalable evaluation in the HASP                    |     | 91  |

| 5.8  | Performance of HASP in larger systems              |     | 92  |

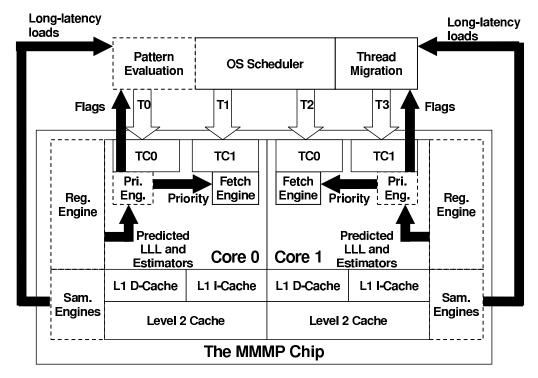

| 6.1  | The ATMS assignment                                |     | 99  |

| 6.2  | The ATMS architecture                              | 1   | .00 |

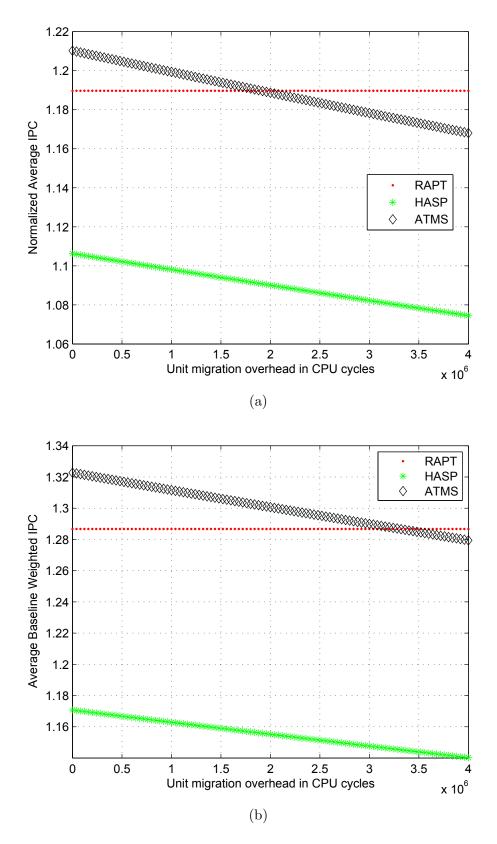

| 6.3  | Performance of the ATMS in a small system          | 1   | .04 |

| 6.4  | Performance of the ATMS in a large system          | 1   | .05 |

## LIST OF ACRONYMS

| The Average Baseline Weighted IPC                      | abwIPC |

|--------------------------------------------------------|--------|

| The Adaptive Thread Management Scheme                  | ATMS   |

| The Normalized Average IPC                             | avgIPC |

| Blended                                                | BD     |

| Computation Intensive                                  | CI     |

| Cycle Per Instruction                                  | CPI    |

| The Data Gating policy                                 | DG     |

| The Dynamic Scheduling Policy                          | dMIX   |

| The Data Cache Warn policy                             | DWarn  |

| The Scheduling Evaluation Overhead                     | EO     |

| First Come First Serve                                 | FCFS   |

| Front Side Bus                                         | FSB    |

| The Hardware Assisted Scheduling Policy                | HASP   |

| Instruction Level Parallelism                          | ILP    |

| Instruction Per Cycle                                  | IPC    |

| Instruction Set Architecture                           | ISA    |

| Job Level Parallelism                                  | JLP    |

| Last Level Cache                                       | LLC    |

| Long-Latency Load                                      | LLL    |

| Memory Intensive                                       | MI     |

| The Microprocessor without Interlocked Pipeline Stages | MIPS   |

| The Static Mix-Scheduling Policy                       | sMIX   |

| Multicore Multithreaded MicroProcessor                 | MMMP   |

| Memory Management Unit                                 | MMU    |

| The Model construction Overhead                        | МО     |

| The Mono-Scheduling Policy                           | Mono  |

|------------------------------------------------------|-------|

| Misses Per Kilo Instructions                         | MPKI  |

| Misses Per Million Instructions                      | MPMI  |

| Multicore Single-threaded MicroProcessor             | MSMP  |

| The Online Linear Model                              | OLM   |

| The Ordinary Least Square Regression                 | OLS   |

| Operating System                                     | OS    |

| The Phase detection Overhead                         | РО    |

| Prediction Expectation                               | PE    |

| Program Counter                                      | PC    |

| The Regression-based Algorithm to Prioritize Threads | RAPT  |

| Reduced Instruction Set Computing                    | RISC  |

| Re-Order Buffer                                      | ROB   |

| Single-core Multithreaded MicroProcessor             | SMMP  |

| Simultaneous Multithreading                          | SMT   |

| The Sampling Overhead                                | SO    |

| The Sampling Period                                  | SP    |

| Single-core Single-threaded MicroProcessor           | SSMP  |

| Standard Deviation                                   | StDev |

| Thread Level Parallelism                             | TLP   |

| The Thread migration Overhead                        | ТО    |

| Windows Size                                         | WS    |

#### CHAPTER 1

#### INTRODUCTION

High performance is greatly pursued in the microprocessor design and nowadays parallelism plays an essential role. The Multicore Multithreaded MicroProcessor (MMMP) employs different levels of parallelism to generate more throughput. Via implementing multiple cores in a processor, the Thread-Level Parallelism (TLP) is well utilized [1]. Further in the same core, the implementation of multiple threads is able to maximize on-chip parallelism, which is especially true for the Simultaneous Multithreading (SMT) architectures [2]. The SMT is defined as fully shared execution resources by several concurrently running threads in the same core, such that both TLP and Instruction-Level Parallelism (ILP) are utilized [3]. However, "Memory Wall" issues [4] still exit in such architectures, and may introduce great impacts on thread performance and system throughput. Moreover, due to the complexity of resource allocation and the variation in workload behaviors, it becomes more difficult to manage the shared resources in the MMMP. Thus more efforts, even innovative approaches, are required to manage the MMMP for better utilization of the resources and thus higher performance.

#### 1.1 The Motivation

The MMMP increases the complexity in resource distribution, and thus the difficulty in resource management. In particular, there are two opposite scenarios in distributing the on-chip resources in the MMMP: isolation and unification. On one hand, since several physical cores are implemented on the chip, the resources are isolated within different cores. Although it is used to explore the TLP, it makes a thread unable to access the resource in other cores. This issue is especially undesired when certain resources are idle in one core, but highly utilized in another core. It reduces the probability to schedule in a nature or heuristic way, such that resources are utilized comprehensively. On the other hand, threads in the same core live on the domestic resources jointly. As a result, the thread behavior is not independent any more, but rather has universal impacts on domestic threads and even threads in other cores. Thread performance may be degraded because of severe competition for the same resource, as well as inappropriate resource allocation, *e.g.*, ignorance of threads' resource demands. Therefore, it requires well-defined management scheme in the complex architecture to optimally utilize the hardware resources [2].

The complexity in hardware is not the only motivation, but workload variation also prompts a novel design. The phase behavior has been studied by dozens of researchers, which indicates workload behavior is somewhere between chaotic and periodic [5]. Phases exist in most workloads with granularity from thousands of instructions to millions of instructions. Within a phase, workload may exhibit similar or stable behaviors, with respect to retired instructions, memory accesses and resource demands. There are a few decent designs that explore phase behaviors for better system performance, but most of them result from a fixed doctrine or a universal assumption. In order to better make use of certainty in the phase behaviors, we advocate monitoring phase changes in a more active way, such that the system resources are allocated adaptively in observance of the varying demands.

#### 1.2 Scope of the Study

Among different levels of resource management schemes, this study is focused on two: the hardware scheduling policy that is executed at the architectural level, and the software scheduling policy that usually happens at the Operating System (OS) level. Hardware scheduling policies take the responsibility to manage the fully shared execution resource within a core, while their approaches may involve prioritization at the fetch stage based on memory accesses and thread behaviors. Hence the instruction fetch policy is a critical entry to allocate resources among simultaneous threads, which exactly belongs to the spectrum of this study. On the other hand, a fundamental objective of software scheduling policies is to increase system throughput in high-performance computing, while load balancing and power and thermal control might also be embedded. This study focuses on higher performance by scheduling, and thus it expects that the proposed design to overcome the boundary among different cores. In summary, both policies share the similar objective to better utilize system resources and the effectiveness of their decisions are highly dependent on workload behaviors. However, they may have the followed dissimilarities:

- **Target**: A software scheduling policy mainly manages threads across multiple cores while a hardware scheduling policy adjusts threads and their instructions in the same core;

- **Granularity**: A software scheduling policy's decisions are usually valid for millions of CPU cycles while a hardware scheduling policy may evaluate every clock cycle;

- Accessibility: A software scheduling policy is designed from a top-down view over multiple cores while a hardware scheduling policy is often embedded in computer architecture within every core.

Therefore, the two scheduling policies are not mutually exclusive, but rather have the potential to form a symbiotic relationship. In such a relationship, they are expected to work collaboratively to overcome the natural gap between hardware and software for optimal resource allocation. Consequently, this study proposes an Adaptive Thread Management Scheme (ATMS) in the MMMP, and the merit lies in integration and adaptability. The integration refers to the active collaboration between hardware (the architectural level) and software (the OS level). It includes, first of all, the mutually beneficial relationship between the OS and the computer architecture. The software scheduling policy provides the architectural level with a proper working environment based on universal hardware resources and thread demands. Meanwhile, the thread demands are collected and partially analyzed at the architectural level and passed to the OS level for even better scheduling. Secondly, it also refers to the cooperation to reinforce management goals at different levels. The software scheduling policy is able to utilize multiple cores to explore TLP for better performance, while it relies on the hardware scheduling policy to further maximize TLP and ILP. The SMT scheduling policy continues the management scheme to fully utilize the shared resource at the pipeline level.

On the other hand, in account for the variation in thread behavior, adaptability is explored through constructing the online model without *a priori* knowledge, such that the ATMS is capable of accessing the critical demands for better resource allocation, in spite of the varying thread behaviors. As they change, the proposed scheme samples the new phases and the periodic information is extracted mathematically. Therefore, the varying behaviors along the execution of a certain workload and various behaviors among different workloads are better summarized to guide both hardware and software scheduling policies. As a result, adaptability is reached in the proposed design.

#### **1.3** Significance of the Study

The MMMP is widely adopted as a critical trend in the design of the next-generation microprocessor. There have been some initial products in the commercial market already, including the Intel<sup>®</sup> Core<sup>TM</sup> processor family [6, 7], the IBM<sup>®</sup> Power7 [8] and the Intel<sup>®</sup> Xeon<sup>TM</sup>[9]. Even though such designs are able to achieve higher performance than previous generations, their resource efficiency might not be optimized until well-designed scheduling policy is implemented [3]. It means there is more difficulty and thus larger potential for better utilization of the hardware resources in the MMMP. Consequently, the proposed scheme makes the MMMP fully utilize the existing hardware resources, and adaptively distribute the shared resources according to the thread demands. Hence, the contributions of this research fall into four aspects:

- 1. Constructed the online linear model to estimate threads' resource demand for the architectural level and the OS level with no *a priori* knowledge;

- 2. Prioritized the threads proactively in a core such that the shared resources in the SMT core were utilized efficiently;

- 3. Scheduled threads adaptively according to their resource usage in a sustainable approach;

- 4. Integrated the hardware and software scheduling policies to further fulfill the responsibility of resource management.

As far as the overall system performance is concerned, the proposed scheme will optimize the resource allocation in the MMMP. As mentioned above, both isolation and unification exist in resource distribution in the MMMP. The ATMS takes into consideration the overall hardware resources and thread demands, such that the thread scheduling is optimized by dynamic manipulation. Though the software scheduling policy is at the OS level, the resource demands are collected and processed directly at the architectural level, which provides the software part with better observation. Furthermore, scalability is a critical challenge as the number of cores and threads increases, so the OS scheduling policy has to transmit partial management goals to the architectural level. In such a case, the ATMS strives to use multiple levels of efforts to achieve the management objective in a complex hardware environment. As a result, the hardware and software scheduling policies work jointly as the ATMS exploits both TLP and ILP for optimal system performance.

From the perspective of the threads, they are more likely to obtain the demanded resources and to be less affected by neighbor threads in the complicated environment. In the MMMP, the resources are isolated in different cores, meaning there are merely limited resources shared by domestic threads in a single core. When the proposed design pairs threads that demand different resources in the core, the contention for the same resource is minimized. Hence they are better satisfied by the limited resource budget through the proposed scheme. Furthermore, the threads sharing pipeline resources are less affected by Long-Latency Loads (LLL). When some threads suffer from the LLL, other threads are able to send more instructions to utilize the shared execution resources, which has minimal impact on the waiting threads.

#### 1.4 The Dissertation Organization

The background information has been introduced in this chapter to show the motivation and contribution of this study in an intuitive tone. In Chapter 2, theoretical perspective is taken to examine the related research. It first introduces the hardware architecture that the ATMS will be implemented in, and then reviews existing scheduling policies in the SMT environment and in the multicore environment.

The ATMS is introduced by addressing three technical topics in Chapters 3, 4 and 5, respectively:

- 1. Online Linear Model (OLM): It is constructed during execution and updated continuously, such that it ensures adaptability of the proposed scheme.

- 2. Regression-based Algorithm to Prioritize Threads (RAPT): The hardware scheduling policy utilizes the OLM at the architectural level to predict future thread demands in prioritizing simultaneous threads.

- 3. Hardware-assisted Scheduling Policy (HASP): The software scheduling policy explores adaptability in the OLM through pairing threads dynamically across multiple cores at the OS level.

After the hardware and software scheduling policies, the aggregation of different components is proposed in Chapter 6. Their performance, *i.e.*, system throughput and average thread performance, is presented with appropriate overheads integrated, such that the proposed designs are validated comprehensively. Eventually, Chapter 7 concludes this dissertation and recommends some interesting future work.

#### CHAPTER 2

#### THEORETICAL PERSPECTIVE AND LITERATURE REVIEW

The related studies are reviewed comprehensively in this chapter. There are several theoretical aspects that should be clarified before a new scheme is proposed:

- 1. Architectural development of the MMMP

- 2. Multithreaded scheduling policies

- 3. Multicore scheduling policies

- 4. The phase behavior

The first topic in Chapter 2.1 is the hardware architecture that this study is focused on, while Chapter 2.2 and 2.3 belong to hardware and software levels respectively. You will find they are usually designed separately by other researchers, but will be collaborating closely in the proposed design, which is the major innovation of this study. Chapter 2.4 is about the resource demands of the workloads.

#### 2.1 Hardware Architecture of the MMMP

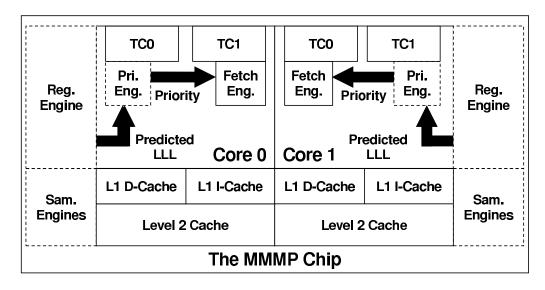

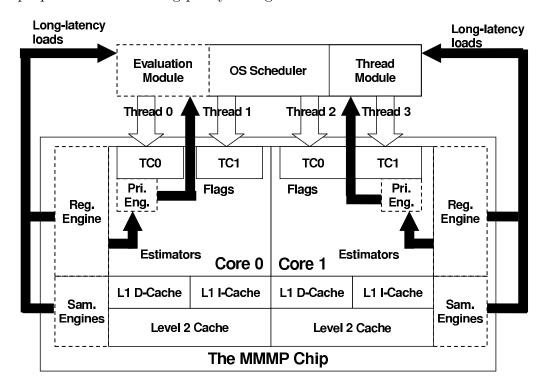

The MMMP is composed of two architectural designs: the multicore architecture and the multithreaded architecture. The former one designs several physical cores on the same chip, such that threads in different cores can explore TLP greatly. The latter one employs the Thread Context (TC) to implement logical cores in the same physical core. They share most execution resources in the same core to maximize the parallelism on the chip. An example of studied two-core four-threaded microprocessor is shown in Figure 2.1.

| тсо           | TC1        | тсо           | TC1        |

|---------------|------------|---------------|------------|

| Core 0        |            | Core 1        |            |

| L1 D-Cache    | L1 I-Cache | L1 D-Cache    | L1 I-Cache |

| Level 2 Cache |            | Level 2 Cache |            |

| The MMMP Chip |            |               |            |

Figure 2.1: An example of two-core four-threaded microprocessor

#### 2.1.1 The SMT Architecture

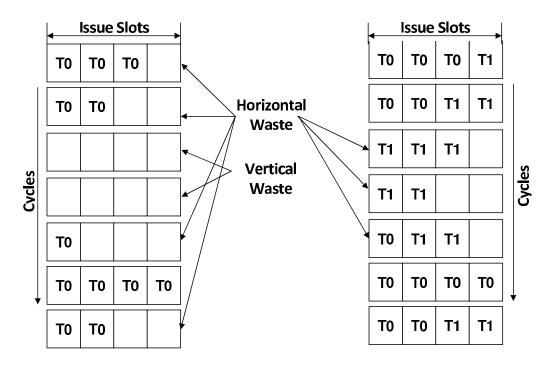

Furthermore, the SMT was first proposed as a multi-streamed superscalar processor by Yamamoto *et al.* [10]. The authors validated the idea mainly via mathematical analysis, though system performance was obtained from emulation. They did not compare the proposed design with other similar architectures, but rather focused on the difference between the simulated results and the predicted results. Tullsen *et al.* [11] proposed the architecture named SMT, in which several threads compete for each of the issue slots in each cycle. The difference was studied among the SMT, fine-grain multithreaded, single-issue and dual-issue designs. In general, the multithreaded architecture is able to minimize the vertical waste, while the SMT further reduces the horizontal waste in microprocessors [12]. Assuming two simultaneous threads T0 and T1 are implemented in the core, the example of minimized horizontal and vertical waste from the single-threaded architecture to the SMT architecture is shown in Figure 2.2.

Figure 2.2: Minimization of the horizontal and vertical waste by the SMT

Given an SMT core that is able to fetch instructions from multiple threads and its critical ability to issue and execute instructions from multiple threads at every clock cycle [13, 2], the computer architecture requires a policy that defines the fetched sources. Practically, the policy is noted as an instruction fetch policy, which concludes the priorities of domestic threads in the fetch stage for the fetch engine. It is of great importance to the performance of the SMT core, because it defines the instructions that utilize the shared resources in the pipeline. Therefore, it is expected to allocate the shared resources in the SMT core to those instructions and threads that have the ability to better utilize them, such that the system throughput is maximized and so is the overall performance. As a result, instruction fetch policies are widely studied as a convenient and effective scheduling policy in the SMT environment, which will be the focus at the hardware level in this study.

#### 2.1.2 The Multicore Architecture

The multicore architecture is mainly focused on Job-Level Parallelism (JLP) and TLP via executing several threads in different cores on the same chip [14]. Its design comes with two flavors: the heterogeneous architecture and the homogeneous architecture. There are several different cores on the chip in a heterogeneous design. For example, in IBM<sup>®</sup> Cell Broadband Engine<sup>TM</sup>[15], the threads are processed by one Power Processing Element (PPE) and then distributed to several Synergistic Processing Elements (SPE). The performance improvement may be achieved when the parallel threads are executed by multiple SPEs, while sequential threads by the the PPE running at a higher frequency [1]. On the other hand, a unique example of the homogeneous multicore microprocessor is the Intel<sup>®</sup> Single Chip Cloud Computer [16], on which 48 identical cores are implemented. It does not employ a separate core to manage the threads but may rely on the multicore scheduling policy in the OS to fully utilize the shared resources in cores.

Considering multiple cores on a chip, the resources are isolated among different cores. Without a thread management scheme, threads are able to access merely resources within the same core. Meanwhile, the threads in a core jointly share the local resources, such that the utilization of the resources are defined by the thread scheduling. Some resources may be highly demanded in a core, while rarely used in another core. From the perspective of threads, their resource demands could not be met because of the resource isolation, even though there are in total enough hardware resources on the chip. As a result, a multicore scheduling policy is needed to manage the threads across different cores, and it ought to take into consideration the resource unification by the SMT architecture as well.

#### 2.2 Scheduling in the SMT Architecture

The instruction fetch policy was originally set as Round-Robin by Yamamoto *et al.* [10], meaning all threads were fetched alternatively. In order to improve the performance of the SMT architectures, Tullsen *et al.* [17] proposed the ICOUNT to assign the priority according to the in-flight instructions. It assumed that the threads with fewer instructions in front-end stages in the pipeline were able to retire more instructions than other threads. As to the system throughput, those threads were expected to committee more instructions in the future and thus were favored in the fetch stage. However, it was argued that the ICOUNT might attach too much importance to high throughput thread, and Tullsen *et al.* realized that the Long-Latency Load (LLL) was the major obstacle to full utilization of the shared resources [17]. As a result, the LLL will be explained in Chapter 2.2.1, and then the hardware scheduling policies that were related to the LLL will be discussed. After that, the policies based on machine learning will be reviewed as well. Moreover, some other policies were proposed for parallel workloads, which have their own characteristics compared to multiprogramming workloads.

#### 2.2.1 The Long-Latency Load

The LLL refers to a miss in the last level cache (LLC), and is caused by the "Memory Wall" [18]. LLC misses lead a thread to wait for the data from lower memory hierarchy, which costs much more time than most operations in the pipeline and data from caches. Empirically the latency is increased from several CPU cycles for the L1 cache to hundreds of CPU cycles for main memory. Due to dependence among

instructions, the thread suffering from the LLL will eventually stall. Consequently, it denies the instruction fetch policies that have biased favor on high-throughput threads, because of the "Memory Wall" and limit ILP [19]. Moreover, the dependent instructions are still floating in the pipeline, occupying the shared resources such as ReOrder Buffer (ROB) and Instruction Queue (IQ). These resources are limited in the SMT architecture and may be demanded by other threads for immediate advancement. As a result, most SMT scheduling policies after the ICOUNT are related to the LLL issue.

#### 2.2.2 Instruction Fetch Policies for the LLC

Given the speed of the memory system develops slower than that of processors, it is less likely that this issue can be solved before long [20]. Therefore, several instruction fetch polices were proposed to deal with the LLL in the SMT.

The Stall and the Flush [21] were both based on the LLL, *i.e.*, L2 cache misses, which were recognized by the system some time after a load. The Stall policy stopped the thread experiencing any L2 cache miss from further fetching, because such a thread was less likely to use more resources efficiently. Nevertheless, the resources being occupied by such a thread could not be released until the data come back. More aggressively than the Stall, the Flush expelled the instructions from such thread to release the occupied resources. Hence, those resources would be available for other threads. It ensured the utilization of shared resources, but required extra overhead for flushing and re-fetching. The essential difference between the Stall and the Flush was whether to release the occupied resources or not. Actually they might lead to different performance depending on the resource budget in the SMT. Consequently, Cazorla *et al.* [22] proposed to improve the Stall and the Flush, such that at least one thread was active in the pipeline. In particular, the oldest stalled

thread was resumed when the final active thread was suspended due to a new LLC miss. They further proposed the Flush++ to enjoy the advantages of both the Stall and the Flush. The Flush++ executed the improved Stall when the system resource was relatively enough, *i.e.*, there were up to four threads in the processor, while followed the improved Flush when the resources were limited, *i.e.*, more than four threads.

#### 2.2.3 Proactive Instruction Fetch Policies

Considering it may be late to act upon a LLC miss, some other instruction fetch policies would rather depend on a L1 cache miss, such that they would respond to the LLL in advance. They were expected to minimize the inefficient occupancy on the shared resources. El-Moursy *et al.* [23] proposed the Data Miss Gating (DG) to observe the L1 cache miss, and stopped a thread from fetching when it had noutstanding L1 cache misses. Although they studied several values, n = 1 has been widely discussed. It resulted in an instruction fetch policy that suspended a thread when there was unsolved L1 cache miss associated with it, which was obviously different from previous work.

Actually, the overhead here to stop a thread with any outstanding L1 cache miss was still high, because the basic concept of the SMT was to utilize more instructions from different threads. In the DG, it might happen that most threads were stopped, such that a lot of resources were idle due to lack of instructions. Therefore, Cazorla *et al.* [24] proposed the Data Cache Warn (DWarn) to adjust the priority without stalling. The DWarn was also based on L1 cache misses, but it reduced the threads' priority with unsolved L1 cache misses in the fetch stage. Consequently, such threads were fetched when other threads without any unsolved L1 cache miss could not satisfy the fetch width. The DWarn strived to keep the fetch width as full as possible, such that the shared resources were utilized by more instructions. Overall, it generated more system throughput than other instruction fetch polices according to their study. In summary, the proactive instruction fetch policies relied on the relationship between L1 and L2 data misses, but there is rarely a precise description about it. Given the execution phases in workloads behaviors, a better observation on the relationship between L1 and L2 data misses, and thus the workload behaviors, would benefit the instruction fetch policies in the STM architectures.

#### 2.2.4 More SMT Scheduling Policies

Furthermore, several studies explored more design spaces in the architectural level as well as in the software level. They were not typical instruction fetch policies, and usually involved the OS in algorithmic computation. Therefore, they might face challenges: high overhead and low adaptability. The overhead is mainly introduced by submitting information to the OS, interrupting the OS and calculating algorithmic parameters; while the disadvantage in adaptability is due to the failure to consider execution phases. Consequently, this study ought to target at an instruction fetch policy that is equipped with low overhead and high adaptability.

Cazorla *et al.* [24] proposed to collect the information of registers and classify instructions with respect to integer, floating-point and load/store units, such that the resource usage was summarized. They assumed the threads without any outstanding L1 cache miss hardly needed any memory accessing resources, while those experiencing L1 cache misses could not perform better even if they were provided with extra computation resources. Therefore, threads fell into different groups with pre-defined resource quotas and fetch throttling was employed to enforce such quotas. On the other hand, Wang *et al.* [25] evaluated thread efficiency via monitoring resource entries and committed instructions. They introduced the Committed Instruction Per Resource Entry (CIPRE) to indicate the resource usage efficiency. Consequently, the threads that were capable of retiring more instructions with less resource entries were favored by the system, and it would fetch more instructions from them to improve the overall resource efficiency and thus system throughput, at the expense of hardware counters and the CIPRE computation by the OS.

Choi *et al.* [26] proposed to achieve the optimal performance via Hill-climbing. The system estimated the impacts of different resource distributions via actually executing them for one epoch. The best observation was employed for future epochs and gradually the optimal resource distribution was realized in the SMT environment. Obviously this scheduling policy introduced considerable hardware overhead in monitoring resource and evaluating performance in the OS.

Recently, as in-order execution is employed again by some modern processors, e.g., the Single Chip Cloud Computer by Intel<sup>®</sup> [16], research on the combination of in-order and out-of-order execution was done by Wang *et al.* [27]. They selected the dependent instructions of a cache miss and arranged them in an individual queue, which was closely related to the instruction queue. When the data came back and such instructions were ready, they were executed in-order in the pipeline. This design reduced instruction window occupancy rate and could be implemented together with other fetch policies.

#### 2.2.5 SMT Scheduling for Parallel Programmes

Originally the multithreaded workloads used by Tullsen *et al.* were composed of multiple independent threads, *e.g.*, benchmarks from SPEC95, which we call multiprogramming. The communication among threads increases rapidly when parallel programmes are employed *e.g.*, Splash [28], SPECjbb [29] and RUBiS [30]. Some scheduling efforts were finished at the granularity of instructions, and they are ad-

dressed here. Later contexts will discuss about the multicore scheduling policies for parallel programmes.

Long et al. [31] proposed to detect the Single Program Multiple Data (SPMD) portion in the benchmark, such that it requires only one instruction fetch for different threads. If the identical instructions required the same input, the execution was limited to one time while the results were duplicated to different threads. This design utilized preliminary analysis for less work in fetching and execution. Meanwhile, Cheng et al. [32] proposed to arrange memory accessing instructions according to the system capability. They justified the thread resource demands via Misses Per Kilo Instructions (MPKI). Assuming redundant memory accesses at the same time were not efficient, the system tried to schedule threads such that memory accesses were under a threshold. The threshold was called Memory Task Limit in the system, which was managed to achieve better performance. Bhattacharjee et al. [33] investigated thread criticality by the weighted summation of L1 and L2 misses, such that future thread behaviors were predicted based on the history information. The voltage and frequency were scaled in accordance with the thread criticality predictor (TCP), such that the power consumption is reduced, instead of improved system throughput.

Similarly in other designs about the parallel programmes in the multicore architecture, e.g., [34, 35, 36, 37, 38, 39, 40], there seemed to be more potential due to more communications among threads than a single program. It easily overwhelms the cost to migrate threads across different cores, such that improvement is virtually deterministic for parallel programmes [37]. However, to find out the critical sections in parallel programmes, *a priori* knowledge is sometime required, *e.g.*, [34], which reduced the adaptability greatly. Some other designs, *e.g.*, [36, 37, 38, 39], were highly dependent on history information, and failed to adopt a statistical view about workload behaviors. Moreover, Kokku *et al.* [35] and Cai *et al.* [40] mainly targeted at less power consumption by network processors.

In summary, they all agreed that the critical sections ought to be recognized and improved in the scheduling policy. Moreover, reducing the communication time within parallel programmes was convenient for performance improvement, especially when compilers were employed for *a priori* knowledge, *e.g.*, [41, 31, 40]. However, possible contribution from the instruction fetch policy was underestimated, and the mutual impacts among different programmes, similar to the inter-thread interference for multi-programming workloads, were not addressed well.

#### 2.3 Multicore Scheduling in the OS

There are many OS scheduling policies proposed for parallel architectures, and the majority of them reside in the OS at the software level. The underlying hardware architecture may be either homogeneous or heterogeneous, but they are not mutually exclusive, because homogenous cores exist partially in a heterogeneous architecture. For example,  $IBM^{(R)}$  Cell Broadband Engine<sup>TM</sup>[15] has identical SPEs. Consequently, the research on homogeneous architectures in this study is eligible for both areas. Furthermore, parallel architectures are extensively employed in clusters or cloud computing. They might not be exactly the same as a Chip MultiProcessor (CMP), in terms of more traffic through I/O interfaces and network communications, but their results are valuable in designing a multicore scheduling policy in the OS. In other words, the proposed schemes will be easily converted to a scheduling policy for cloud computing.

#### 2.3.1 Homogeneous Microprocessors

The multicore scheduling policies are widely studied to pursue various goals, and high performance is a major one. Especially in the MMMP, the resources are distributed across different cores, so the way in which the threads are scheduled defines how the resources are utilized [2].

In the environment of the Single-core Multithreaded Microprocessor (SMMP) with the SMT, Snavely *et al.* [42] proposed the symbiotic scheduling policy to mix jobs with different priorities together, such that the system throughput was increased due to multithreading and co-scheduling. Furthermore, scheduling based on cache usage in the Multicore Single-threaded Microprocessor (MSMP) was studied in [43, 44, 45]. They modified the scheduling policy in the Linux kernel, and the cache usage was balanced among private caches of different cores. However, they did not discuss the unique characteristic of the MMMP with the SMT, that potential for better performance could be explored through fully utilizing the execution resources by several concurrent threads.

Zhuravlev *et al.* [46] concluded that the dominant factor in the MMMP is the contention for resource lower than LLCs, *e.g.*, the DRAM controller, the Front Side Bus (FSB) and prefetch requests. It was found that better performance could be achieved by pairing threads with different demands for such resources [47], compared to scheduling threads with similar demands to the same core. More system throughput was generated by the proposed scheduling policy, but it did not conduct real-time migration, so the policy was a static dispatching policy with *a priori* knowledge. Radojkovic *et al.* executed a large quantity of task assignments among all possible combinations, such that the best observed one was statistically within the top performance group [48]. Their design spent 2 hours on executing every 5000 assignments, and every new set of threads needed such a process. Other studies such

as [49, 50, 46] conducted online manipulation for better scheduling, but fixed epochs with respect to CPU cycles, *e.g.*, 100 million CPU cycles, were employed in their designs. It could not adapt to the various workload behaviors during execution.

#### 2.3.2 Heterogenous Microprocessors

Aside from scheduling within the homogeneous domain, the coordination throughout multiple heterogenous cores also helps improve system performance. Fundamentally, the Amdahl's Law [51] pointed out two sources for performance improvement: the serial part and the parallel part. Hence, a more powerful core, e.q., higher frequency and voltage, can be used to execute the serial part, while exploring TLP by several less power cores [1, 52, 53, 54] for the parallel part. This approach is able to speedup both parts, such that the overall system throughput is increased. However, they did not address the resource sharing in the heterogeneous cores, so they would further need the scheduling policies for homogeneous cores to manage multiple identical cores. Furthermore, the scenario to identify the serial part and parallel part is a great challenge. Eyerman et al. [55, 56] proposed an off-line analysis tool to examine the Cycle Per Instruction (CPI) breakdowns for the parallel applications, and then use the results to estimate threads' demands during execution. In order to work in the multithreaded environment, a thread was sampled when it was running alone and then comprehensively running with other threads, such that a better scheduling was concluded [57]. Even though they specified hardware counters for their design, the execution of a thread alone and with other threads should not be a prerequisite for a design.

As a result, even though we see a convenient objective in the scheduling policy in heterogeneous microprocessors, the necessary information is rarely available during execution. In order to develop an adaptive scheduling policy, a better observation on the various workloads behaviors remains an open question.

#### 2.3.3 Allocation of Memory Resources

Some researchers proposed to manage the shared resources by coordinating accesses to the memory hierarchy, especially the cache [58, 59, 60, 61]. They spent many efforts on monitoring memory accesses by different threads, so the scalability of their designs might not be promising in larger systems. Moreover, because real memory accesses happen when an instruction is ready to retire, such approaches could not take the action proactively enough to prevent the inefficient occupancy on the shared resource in the pipeline. Studies such as [62, 63] proposed complex algorithm to allocate the cache resources to different threads, but their biased scheduling in the cache system may affect user experience and thus reduce Quality of Service (QoS). It was studied by Liu *et al.* [2] that to evenly divide the cache among corresponding threads results in superior performance given its relatively low complexity and overhead.

#### 2.3.4 Scheduling Policies in Cluster

Even though they do not share exactly the same architecture with multicore microprocessors, scheduling policies in many-node clusters are meaningful and useful. They shared the similar concept with our study that resource demands ought to be considered in scheduling. Weinberg *et al.* [64] proposed the symbiotic space-sharing in a many-node supercomputer. They argued that a single job on the node could not fully utilize the resources, so it was better in terms of resource efficiency to co-schedule some other jobs. As a result, they utilized the idle resources in nodes via executing background jobs at a lower priority than the primary jobs in the same node. Sodan *et al.* [65] proposed to schedule jobs according to their resource demands, which are CPU-bound, disk-bound and network-bound. Even though they mentioned the SMT architecture, in their cluster each node was equipped with independent hierarchical memory system. The difference between the MMMP and their cluster is the resources lower than the LLC, such as the DRAM controller, the FSB and prefecth requests. Moreover, Frachtenberg *et al.* [66] proposed to classify processes into several categories with descending priorities for scheduling in a manynode system. The categorization was in accordance with thread's synchronization requirement and CPU utilization. Although they provided some hints to classify the processes dynamically, their criteria were mainly based on the CPU time and communication time in the network, which was not applied to the shared resources in the SMT.

#### 2.3.5 Thread Replacement

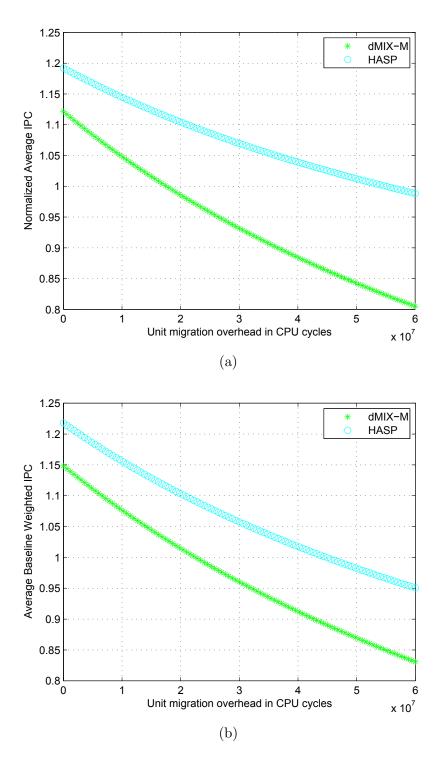

Compared to a static dispatching policy, a dynamic multicore scheduling policy that moves threads across different domains is better at ensuring the scheduling objective [46]. Therefore, most multicore scheduling policies, such as [42, 43, 46, 64, 65], involved dynamic thread migration. Essentially, the total improvement to the system is the difference between the suspending time during migration and the reduced execution time by migrating, so the overhead introduced by migrating threads plays a critical role in defining the final performance.

The overhead conceptually results from rescheduling the process to another hardware thread on another core, manipulating the page table and warming up a new cache in a homogeneous multicore architecture [67]. If there is a heterogeneous architecture, binary translation and state transformation are further required to execute the task in a new Instruction Set Architecture (ISA) [68]. There are many researchers who conducted the studies on easier and more efficient migrations, such as [68, 69, 70, 71], but they were focused on the heterogeneous architectures, and were unable to reduce the overhead to completely zero.

Moreover, DeVuyst *et al.* [68] found that the unit overhead of migration is highly dependent on the underlying architecture, the characteristic of the victim threads and the difference between the source and the destined environment. Consequently, we would like to emphasize the followed points in this study:

- 1. This study is focused on higher performance at a given overhead, while it does not fall into our scope to reduce the unit overhead.

- 2. This study is based on the homogeneous architectures and thus the overhead is due to rescheduling and warming up.

- 3. The performance of the proposed schemes will be discussed with the overhead properly considered.

# 2.4 The Shared Resources and Workload Behaviors

In the followed context, we will first of all examine the shared resources. There have been several approaches to monitor the resources, such that the utilization was summarized. The second part is about the workload behaviors. The related studies have spent great efforts on analyzing the demands in different phases along execution, and among different workloads. The results paly an essential role in scheduling instructions and thread in the multithreaded architecture and the multicore architecture.

#### 2.4.1 The Shared Resources

It provides better abstraction to divide the shared resources in the MMMP into two categories: computation resources and memory accessing resources [66]. The former one involves execution resources in the pipeline as well as the high-level caches. State-of-the-art design of fast cache is at similar speed with the CPU clock, meaning its latency is around 1 - 2 CPU cycles. Therefore, the accesses to highlevel cache belong to usage of computation resources. On the other hand, lower memory hierarchical systems are memory accessing resources, which include lowlevel memory hierarchy, the DRAM controller, the FSB and prefetch requests. In quantity, Zhu *et al.* [72] provided the Cycle Per Instruction (CPI) portions to express the usage. The overall CPI was decomposed into computing, L1, L2, L3 and main memory accessing. The sum of the first two parameters suggested the usage of computation resources, while others were considered as memory accessing resources. Sharing the same concept, the cache miss rate was used as the metric by Cazorla *et al.* [73].

#### 2.4.2 Demands along Execution

From the perspective of threads, their resource demands can be described in such a categorization. Take cache miss rate as an example [73]: the threads with miss rate no less than 1% are considered to mainly utilize memory accessing resources, such that their performance is Memory Intensive (MI). On the contrary, the threads with cache miss rate less than 1% belong to the Computation Intensive (CI) category. This categorization is widely used in constructing multi-programming workloads. Depending on the benchmark category, a multiprogramming workload may be pure, *i.e.*, CI or MI, or blended, *i.e.*, BD. The similar result is available from summarizing misses over retired instructions, *e.g.*, Misses Per Kilo (1024) Instructions (MPKI)

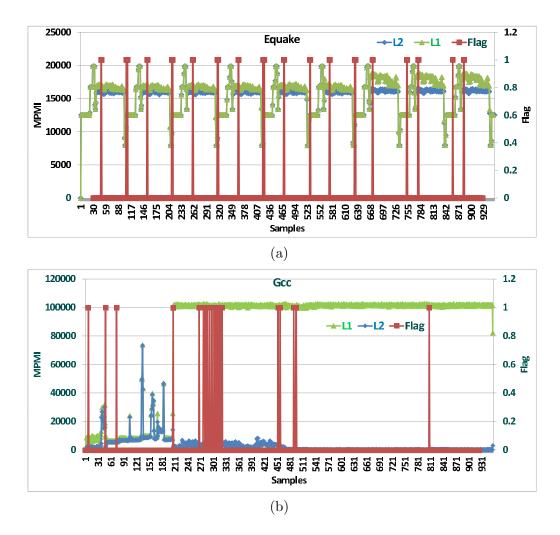

in [32, 74, 45] and Misses Per Million ( $1024 \times 1024$ ) Instructions (MPMI). It follows the natural pace of the thread, rather than any specific execution environment. Thus, the MPKI or the MPMI are better at telling the thread resource demands in spite of the architectural specification. Considering execution phases [5], thread demands in terms of the MPKI or the MPMI partially shows phase behaviors along the execution of a single workload.

Duesterwald *et al.* studied the prediction along the execution of a single thread. Their designs were focused on the correlation among different performance metrics, *e.g.*, IPC and cache misses, and had no consideration for inter-thread interference [75]. Other categorizations were proposed as Colors [76] and Animals [77], which had more categories for the threads and thus more information was represented by the categorization. Furthermore, there were designs focused on the demands of threads [43, 77, 78, 79, 80], but their designs required *a priori* knowledge, and thus were not qualified for a real-time approach. For example, Chen *et al.* [80] involved deep profiling in the source code, searching for instructional dependency, data locality, instruction mixture and control flows.

#### 2.4.3 Demands among Workloads

Pereira *et al.* [81] proposed to dynamically identify phase based on traces of the workloads. It obviously required analysis before the workloads were actually executed on the machine. Inspired by the Branch Predictor in the computer architecture, other studies [82, 83, 84] employed history patterns at different levels, *e.g.*, global or local, to predict the execution phases. The basic concept of their approaches was not adaptive enough for the execution phases, because the answer of a basic predictor is simply True or False. In order to further understand the workload demands, their approaches were associated with more hardware resources, such as phase information tables, though its consistency with the prediction remains an open question.

The term Critical Section is mostly applied to parallel programmes, which is the serial part in the execution and defines the total execution time. Hollingworth [85] was the first to insert segments to the source code and monitor the program during execution to identify the critical sections. Recent studies such as Age-based approach [86] and Bottleneck Identification and Scheduling (BIS) [87] were also assisted by the source code, the library and/or the compiler in differentiating the applications. Even though prediction is proposed by Fields *et al.* [88, 89], their predictor was Program Counter(PC)-indexed and trace-based. Some other studies, *e.g.*, [90, 91], obtained the representative information of the underlying architecture, and then estimated the performance of the applications. Their employment of the *a priori* knowledge hardly helps apply their designs to various environments.

Ebrahimi *et al.* [41] identified the serial parts in the parallel applications, and increased their priorities in the memory scheduler, such that the application moves faster to the parallel parts that may be executed by multiple threads and/or cores. Cai *et al.* [40] relied on the hint instructions inserted into the source code, and thus the execution of a loop would trigger new scheduling decisions. However, they attached little importance to inter-program interference, which is more universal in both parallel workloads and multi-programmed workloads.

Therefore, inter-thread interference further increases the difficulty in utilizing execution phases for scheduling policies. Most of current studies rely on analysis in advance in order to predict during the actual execution. When *a priori* knowledge is not available, the prediction is shrunk to PC-based, so that the detailed characteristics of the execution phases cannot be easily unveiled. On the other hand, the focus on the critical section in parallel programmes underestimates the importance of inter-thread interference, such that an adaptive and practical approach to identify execution phases is high desired.

## 2.5 Summary of the Related Work

In this chapter, we first of all examined the underling hardware in this study, which was the multicore multithreaded architecture. It introduced two distinguished impacts on the resources in an MMMP: unification and isolation. It meant the resources were shared by domestic threads within a core, but isolated among different cores. Meanwhile, the varying behavior of various workloads were spotted by a lot of researchers, and most of them would like to better use the execution phases to guide the scheduling in the MMMP. As a result, we recognized two major problems in the studied area: complexity in resource allocation and variation in workload behaviors.

In order to provide a solution to the problems, integration and adaptability will be proposed in this study. In this chapter, we have reviewed many related studies, and to our best knowledge, their designs were separated by the hardware and the software, or there has been no collaborative design. On the other hand, the existing scenarios to identify execution phases were either associated with off-line analysis, or weak at detailed information of the coming phases. Therefore, the proposed policies in this study will be an integrated approach, that employs both hardware and software efforts to cope with the complicated resource allocation in the MMMP; while they are also adaptive in identifying execution phases and telling more details about the phases.

#### CHAPTER 3

# THE ONLINE LINEAR MODEL

Let us start the design from observing workloads of the MMMP. In general, phase behaviors are seen in most workloads at different granularity, but the repeated behavior is somewhere between ideally periodic and totally chaotic. Memory accesses are major phase behaviors and they show the essential demands of thread in scheduling policies [5, 46]. In practice, it is motivated by the observation in [47], in which a correlation coefficient of -0.4492 was obtained between L1 and L2 cache miss rates. Such coefficient hints an interesting relationship between L1 and L2 cache misses, which is neither linear, *e.g.*, coefficient = 1, nor unrelated, *e.g.*, coefficient = 0. It summons further investigation for better description, especially from a statistical perspective.

As a result, the Online Linear Model (OLM) regression is proposed in this chapter in an effort to better investigate into the relationship and the phase behavior. The proposed design relies on the Ordinary Least Square (OLS) Regression to construct the online model. Though there are a few mathematical approaches available in constructing models, efficiency is not guaranteed empirically for a sophisticated implementation. Hence, the estimation is started from the OLS regression in Chapter 3.1. Furthermore, the OLM is designed in Chapter 3.2, and its hardware engines are built to accommodate its features in Chapter 3.3. Optimization is conducted to reduce latency and complexity, while other overheads, such as power, area and storage, are considered as well. Summary of the OLM is written in Chapter 3.4.

## 3.1 The OLS Regression

Given that a random variable Y is a function depending only on another random variable X and their relationship is linear, they can be expressed as:

$$Y = \beta X + \alpha + \varepsilon \tag{3.1}$$

where  $\varepsilon$  is Gaussian distribution with zero mean and variance  $\sigma^2$ , while  $\beta$  and  $\alpha$  can be evaluated as  $\hat{\beta}$  and  $\hat{\alpha}$  through the regression [92]. Therefore  $\hat{\beta}$  and  $\hat{\alpha}$  are evaluated:

$$\hat{\beta} = \left[\sum_{i=1}^{n} (x_i - \bar{x})(y_i - \bar{y})\right] \left[\sum_{i=1}^{n} (x_i - \bar{x})^2\right]^{-1}$$

(3.2)

$$\hat{\alpha} = \bar{y} - \hat{\beta}\bar{x} \tag{3.3}$$

where  $\bar{x}$  and  $\bar{y}$  are the mean values for X and Y respectively,  $x_i$  is for misses in the L1 DCache,  $y_i$  refers to the data requests that miss in L2 cache and n stands for the number of samples. The OLS regression is the best among all unbiased estimators in the sense of having the smallest variance [92, 93].

Furthermore, X and Y are both one-dimension matrices, or vectors, so the simple regression can be used to calculate the estimators:

$$\hat{\beta} = \frac{L_{xy}}{L_{xx}} = \left[\sum_{i=1}^{n} x_i y_i - n\bar{x}\bar{y}\right] \left[\sum_{i=1}^{n} x_i^2 - n\bar{x}^2\right]^{-1}$$

(3.4)

And  $\hat{\alpha}$  still uses Equation 3.3.  $\varepsilon$  is omitted from our model to achieve moderate simplicity in computation. The beauty of simple regression is to update factors accumulatively, rather than to re-calculate them completely, and thus it is feasible to reduce the hardware overhead greatly.

In reality, perfect linear relationship hardly exists, especially between L1 and L2 cache misses along execution, so significance test on the linear relationship may be used to determine the accuracy of the regression. The total sum of squares  $(S_T)$

is composed of the residual sum of squares  $(S_e)$  and the regression sum of squares  $(S_R)$ . As a result, the difference between the estimated values  $(\hat{Y})$  and the original values (Y) is decomposed into two parts: one resulting from the linear relationship, *i.e.*,  $S_R$ , and one caused by other factors, *i.e.*,  $S_e$ .

$$F = \frac{S_R}{S_e/(n-2)} = \frac{\sum_{i=1}^n (\hat{y}_i - \bar{y})^2}{\sum_{i=1}^n (y_i - \hat{y}_i)^2/(n-2)}$$

(3.5)

Given the hypothesis that there exists linear relationship, when the variation mainly results from the linear relationship, rather than other factors, the linearity hypothesis is true. Hence, the F value of the regression is used to test the significance level of the model quantitatively [92]. With the required significance level  $\rho$ , the above hypothesis holds when  $F \gg \mathcal{F}_{\rho}(1, n-2)$  is true, where  $\mathcal{F}_{\rho}(1, n-2)$  is the Fdistribution upon  $\rho$ , and n is the number of elements in Y.

### 3.2 Construction of the OLM

Two modules are needed to construct OLM:

- 1. **Sampling**: It collects cache misses information and interrupts other modules upon newly completed samples.

- 2. **Regression**: It performs an iteration of regression as soon as new samples are available. It also predicts according to the updated sample and the current model.

## 3.2.1 The Sampling Module

L1 and L2 data misses are collected in this module, while samples are formed for every Sampling Period (SP). The model is focused on the relationship between L1 DCache misses and the consequential L2 cache misses. Even if the L2 cache is

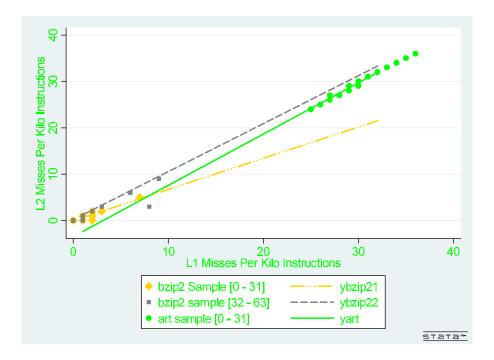

Figure 3.1: The Online Linear Model of cache misses

unified, we track the data request misses only. Here the Misses Per Kilo Instructions (MPKI) [32, 74] or the MPMI might be employed, where the SP is 1 kilo (1024) or 1 million (1024<sup>2</sup>) instructions. We feel it is a better metric than miss rate in terms of quantitatively describing the pressure on the cache system caused by the thread. Two SPEC CPU2000 benchmarks [94]: bzip2 and art, are taken as an example. Their MPKIs are collected in some arbitrary segments, which are shown in Figure 3.1.

## 3.2.2 The Regression Module

Given X as the L1 Data Cache (DCache) MPKI and Y as the data MPKI in L2 cache, the OLS regression is conducted using Equations 3.2 and 3.3 in this module. The number of samples employed in regression is denoted as the Window Size (WS) in this study, and  $\{SP, WS\}$  will be used to specify OLM's configuration. Prediction

is fulfilled using newly updated L1 data misses and estimators:

$$\hat{y} = \hat{\beta}x + \hat{\alpha} \tag{3.6}$$

where  $\hat{\beta}$  and  $\hat{\alpha}$  are estimators from the OLS regression, x is the current L1 MPKI, while  $\hat{y}$  is the predicted value, *i.e.*, the L2 MPKI. Let's stick to the example in Figure 3.1, in which 32 samples are recorded in a row, *i.e.*, {1K, 32}. Consequently, there are three groups of consecutive samples, which are shown as the dots in Figure 3.1.

First of all, it is valid to employ the OLS regression for linear model, because they are proven by the significance test, *i.e.*, F test based on Equation 3.5. In detail, the *art* model has  $F_{art} = 405.31$ , while bzip2 models have  $F_{bzip2[0-31]} = 179.09$ and  $F_{bzip2[32-63]} = 179.36$ , which are all greatly larger than the corresponding F distribution, *i.e.*,  $\mathcal{F}_{0.01}(1, 30) = 7.56$ .