### Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-5-2010

### Realization of Differentiated Quality of Service for Wideband Code Division Multiple Access Core Network

Yechang Fang Florida International University, yfang003@fiu.edu

**DOI:** 10.25148/etd.FI10080417

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

#### Recommended Citation

Fang, Yechang, "Realization of Differentiated Quality of Service for Wideband Code Division Multiple Access Core Network" (2010). FIU Electronic Theses and Dissertations. 244. https://digitalcommons.fiu.edu/etd/244

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## REALIZATION OF DIFFERENTIATED QUALITY OF SERVICE FOR WIDEBAND CODE DIVISION MULTIPLE ACCESS CORE NETWORK

A dissertation submitted in partial fulfillment of the

requirements for the degree of

DOCTOR OF PHILOSOPHY

in

ELECTRICAL ENGINEERING

by

Yechang Fang

2010

To: Dean Amir Mirmiran

College of Engineering and Computing

This dissertation, written by Yechang Fang, and entitled Realization of Differentiated Quality of Service for Wideband Code Division Multiple Access Core Network, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

|                                                | Jean H. Andrian                                         |

|------------------------------------------------|---------------------------------------------------------|

|                                                | Deng Pan                                                |

|                                                | Yimin Zhu                                               |

|                                                | Kang K. Yen, Major Professor                            |

| Date of Defense: March 5, 2010                 |                                                         |

| This dissertation of Yechang Fang is approved. |                                                         |

|                                                |                                                         |

|                                                | Dean Amir Mirmiran College of Engineering and Computing |

|                                                | Interim Dean Kevin O'Shea                               |

|                                                | University Graduate School                              |

Florida International University, 2010

© Copyright 2010 by Yechang Fang

All rights reserved

#### **DEDICATION**

I dedicate this thesis to my wife, parents and parents-in-law. Without their patience, understanding, support, and most of all love, the completion of this work would not have been possible.

#### **ACKNOWLEDGMENTS**

I wish to thank my advisor, Dr. Kang Yen, for his support, patience, and good humor. His gentle but firm direction has been most appreciated. His interest in sense of telecommunication was the impetus for my proposal. From the beginning, he had confidence in my abilities to not only complete a degree, but to complete it with excellence. I extend my gratitude to my committee members Dr. Jean Andrian, Dr. Deng Pan and Dr. Yimin Zhu for their valuable input.

I have found my coursework throughout the curriculum and instruction program at FIU to be stimulating, providing me with the tools with which to explore both past and present ideas and research issues.

The research infrastructure of the System Dynamic Lab and the financial support provided by the Presidential Fellowship and the Dissertation Year Fellowship made of this research endeavor a successful one.

#### ABSTRACT OF THE DISSERTATION

## REALIZATION OF DIFFERENTIATED QUALITY OF SERVICE FOR WIDEBAND CODE DIVISION MULTIPLE ACCESS CORE NETWORK

by

#### Yechang Fang

#### Florida International University, 2010

#### Miami, Florida

#### Professor Kang K. Yen, Major Professor

The development of 3G (the 3rd generation telecommunication) value-added services brings higher requirements of Quality of Service (QoS). Wideband Code Division Multiple Access (WCDMA) is one of three 3G standards, and enhancement of QoS for WCDMA Core Network (CN) becomes more and more important for users and carriers. The dissertation focuses on enhancement of QoS for WCDMA CN. The purpose is to realize the DiffServ (Differentiated Services) model of QoS for WCDMA CN.

Based on the parallelism characteristic of Network Processors (NPs), the NP programming model is classified as Pool of Threads (POTs) and Hyper Task Chaining (HTC). In this study, an integrated programming model that combines both of the two models was designed. This model has highly efficient and flexible features, and also solves the problems of sharing conflicts and packet ordering. We used this model as the programming model to realize DiffServ QoS for WCDMA CN.

The realization mechanism of the DiffServ model mainly consists of buffer management, packet scheduling and packet classification algorithms based on NPs. First,

we proposed an adaptive buffer management algorithm called Packet Adaptive Fair Dropping (PAFD), which takes into consideration of both fairness and throughput, and has smooth service curves. Then, an improved packet scheduling algorithm called Priority-based Weighted Fair Queuing (PWFQ) was introduced to ensure the fairness of packet scheduling and reduce queue time of data packets. At the same time, the delay and jitter are also maintained in a small range. Thirdly, a multi-dimensional packet classification algorithm called Classification Based on Network Processors (CBNPs) was designed. It effectively reduces the memory access and storage space, and provides less time and space complexity.

Lastly, an integrated hardware and software system of the DiffServ model of QoS for WCDMA CN was proposed. It was implemented on the NP IXP2400. According to the corresponding experiment results, the proposed system significantly enhanced QoS for WCDMA CN. It extensively improves consistent response time, display distortion and sound image synchronization, and thus increases network efficiency and saves network resource.

#### TABLE OF CONTENTS

| CHAPTER   |                                               | PAGE      |

|-----------|-----------------------------------------------|-----------|

| CHAPTER 1 | INTRODUCTION                                  | 1         |

|           | Statement of the Problem Area                 |           |

|           | cance of the Study                            |           |

| _         | ch Premise                                    |           |

|           | ch Methodology                                |           |

|           | zation                                        |           |

| CHAPTER 2 | REALIZATION MECHANISM OF DIFFERSEV QOS        | FOR WCDMA |

|           | TELEBERTHON WEETHINGS OF BITTERSEV QUS        |           |

|           | ction                                         |           |

|           | IA QoS Architecture                           |           |

|           | v QoS Model                                   |           |

|           | DiffServ Architecture                         |           |

|           | DiffServ Features and Advantages              |           |

|           | v QOS Realization Mechanism                   |           |

|           | DiffServ Realization Framework                |           |

|           | DiffServ Realization Mechanism                |           |

| 2.5 Summa | ry                                            | 22        |

|           |                                               |           |

|           | B HARDWARE PLATFORM AND PROGRAMMING           |           |

|           | QOS FOR WCDMA CN                              |           |

|           | 0 NP Overview                                 |           |

|           | 0 Functional Modules                          |           |

|           | ages of Using IXP2400 to Achieve DiffServ QoS |           |

|           | 0 Programming Models                          |           |

| 3.4.1     | The HTC Model                                 |           |

| 3.4.2     |                                               |           |

|           | pment of the Comprehensive Programming Model  |           |

| 3.6 Summa | ry                                            | 36        |

| CHAPTER 4 | QUEUE MANAGEMENT ALGORITHM DESIGN             | 37        |

|           | Management Overview                           |           |

|           | g Buffer Management Algorithms                |           |

|           | pment of the PAFD Algorithm                   |           |

| 4.3.1     | Algorithm Description                         |           |

| 4.3.2     |                                               |           |

|           | Simulation Results                            |           |

| 4.4.1     | Simulation for Commen Services                |           |

| 4.4.2     | Simulation for DiffServ                       |           |

|           | g Packet Scheduling Algorithms                |           |

|           | pment of the PWFQ Algorithm                   |           |

| 4.6.1 Algorithm Description                        | 57  |

|----------------------------------------------------|-----|

| 4.6.2 Performance Analysis                         |     |

| 4.7 PWFQ Simulation Results                        |     |

| 4.8 Summary                                        |     |

| CHAPTER 5 PACKET CLASSIFICATION ALGORITHM DESIGN   | 65  |

| 5.1 Introduction                                   |     |

| 5.2 Existing Packet Classification Algorithms      |     |

| 5.3 CBNPs Algorithm                                |     |

| 5.3.1 Algorithm Description                        |     |

| 5.3.2 Performance Analysis                         |     |

| 5.3.3 Algorithm Implementation and Optimization    | 70  |

| 5.4 Simulation Results                             | 72  |

| 5.5 Summary                                        | 74  |

| CHAPTER 6 REALIZATION OF DIFFSERV QOS FOR WCDMA CN | 75  |

| 6.1 Introduction                                   |     |

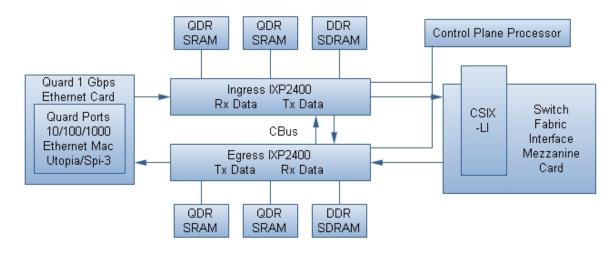

| 6.2 Hardware Design of WCDMA QoS Based on IXP2400  | 76  |

| 6.3 Software Design of WCDMA QoS Based on IXP2400  | 78  |

| 6.4 Simulation Results                             | 83  |

| 6.4.1 DiffServ Test                                | 83  |

| 6.4.2 System Test                                  | 92  |

| 6.5 Summary                                        | 98  |

| CHAPTER 7 CONCLUSION                               | 99  |

| 7.1 Major Outcomes                                 | 100 |

| 7.2 Prospective Research Endeavors                 | 101 |

| LIST OF REFERENCES                                 | 103 |

| VITA                                               | 108 |

#### LIST OF TABLES

| TABLE                                                      | PAGE |

|------------------------------------------------------------|------|

| Table 4-1 Fairness Index Comparison of TD, RED and PAFD    | 51   |

| Table 4-2 Fairness Index Comparison between TD and DS-PAFD | 53   |

| Table 4-3 Comparison of Algorithm Results                  | 62   |

| Table 4-4 Flows Distribution                               | 63   |

| Table 4-5 Latency Comparison                               | 63   |

| Table 5-1 Measured Results from Real Application.          | 74   |

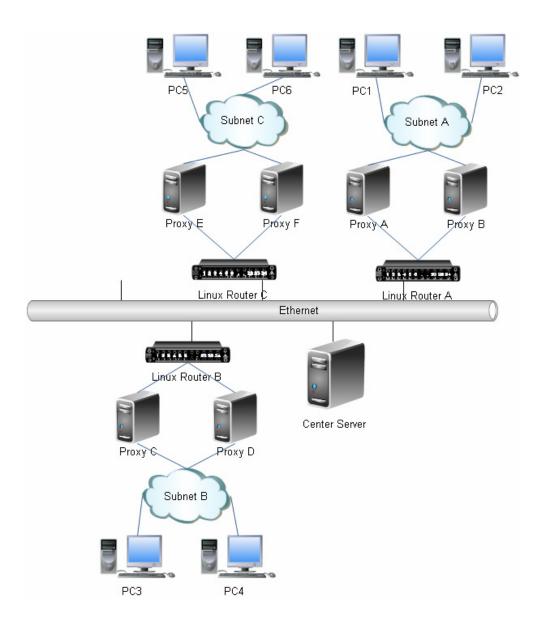

| Table 6-1 Test Equipments and Simulation Modules           | 93   |

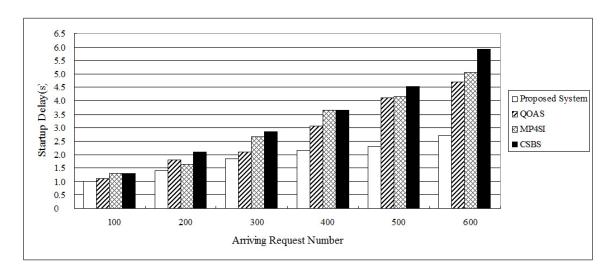

| Table 6-2 Startup Delay Comparison Results                 | 96   |

| Table 6-3 System Capacity Comparison Results               | 98   |

#### LIST OF FIGURES

| FIGURE                                                                 | PAGE |

|------------------------------------------------------------------------|------|

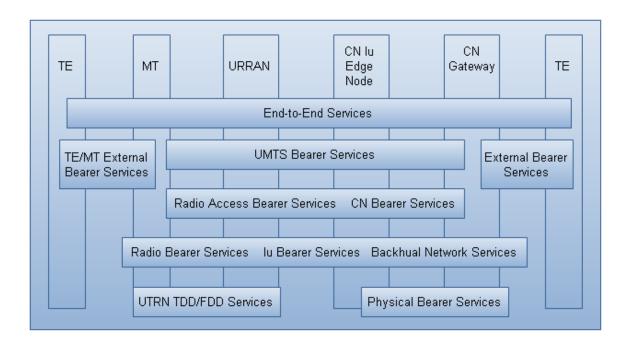

| Figure 2-1 WCDMA QoS Structure                                         | 11   |

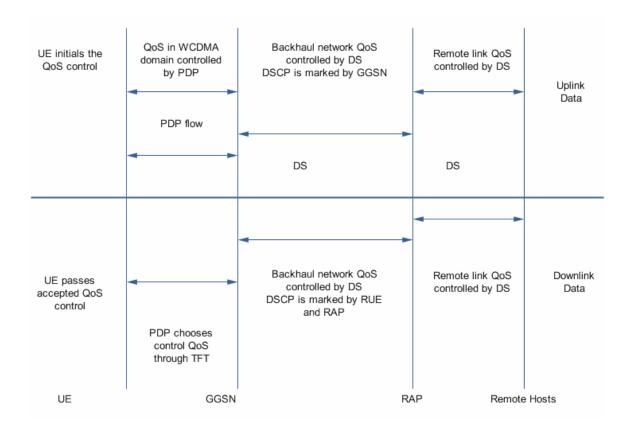

| Figure 2-2 Control Information Interactive Process                     | 21   |

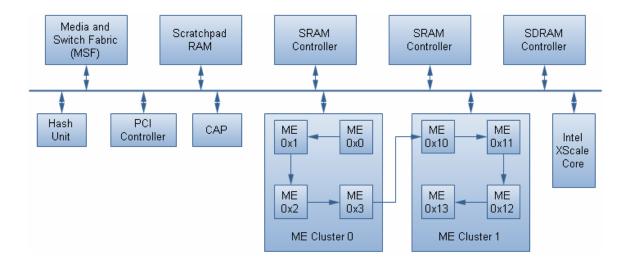

| Figure 3-1 IXP2400 Main Functional Units                               | 26   |

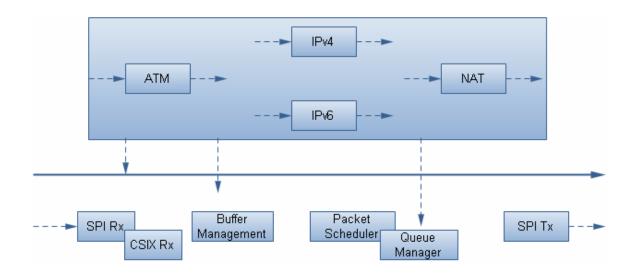

| Figure 3-2 POTs Model Structure                                        | 32   |

| Figure 3-3 Comprehensive Programming Model Structure                   | 35   |

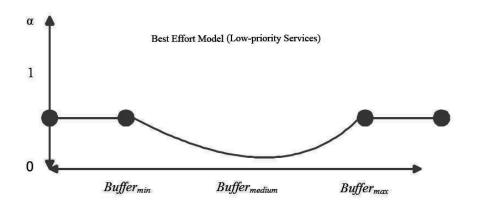

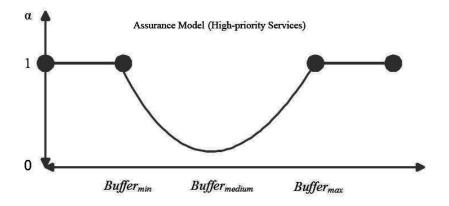

| Figure 4-1 An Adaptive Curve of Parameter α                            | 45   |

| Figure 4-2 Values of Parameter α for Different Priority Services       | 46   |

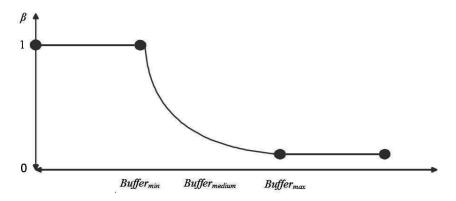

| Figure 4-3 Values of Parameter β for Different Priority Services       | 47   |

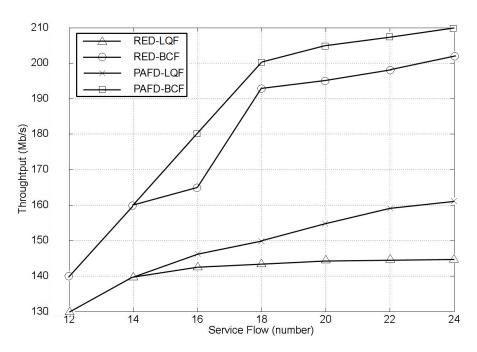

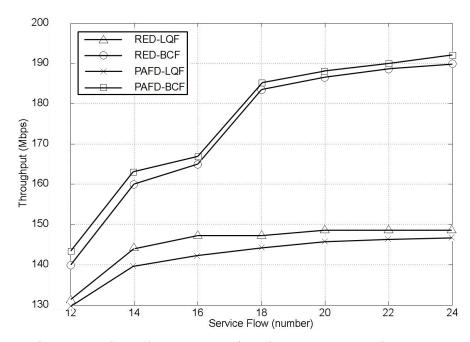

| Figure 4-4 Throughput Comparison between RED and PAFD                  | 49   |

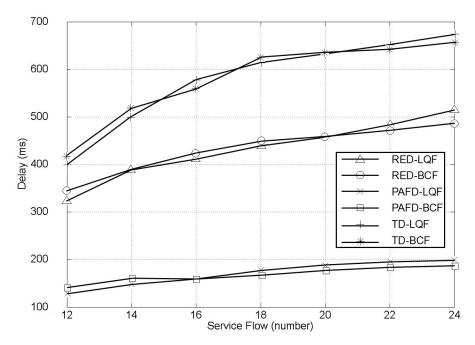

| Figure 4-5 Comparison of Average Queuing Delay for TD, RED and PAFD    | 50   |

| Figure 4-6 Throughput Comparison between RED and DS-PAFD               | 52   |

| Figure 4-7 Comparison of Average Queuing Delay for RED and DS-PAFD     | 52   |

| Figure 4-8 A Typical Packet Scheduling System                          | 54   |

| Figure 6-1 Positions of QoS Switching in a Network.                    | 76   |

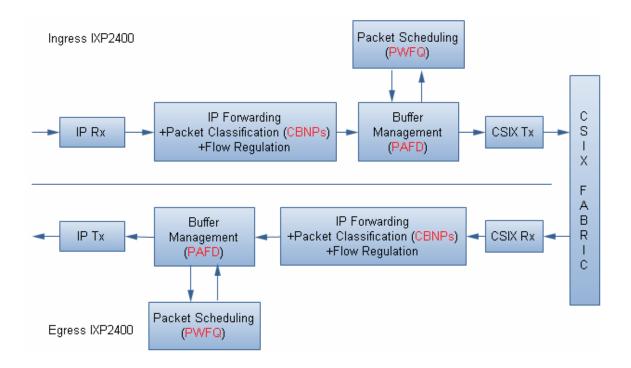

| Figure 6-2 Hardware Architecture of DiffServ QoS                       | 77   |

| Figure 6-3 Software Architecture of DiffServ QoS                       | 79   |

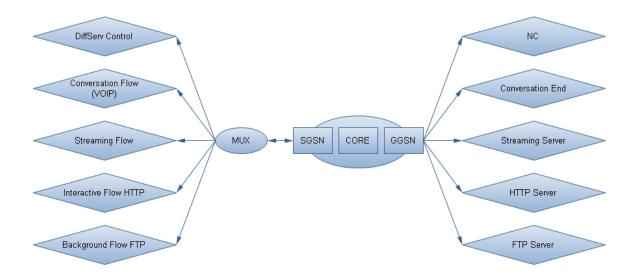

| Figure 6-4 DiffServ Test Structure                                     | 83   |

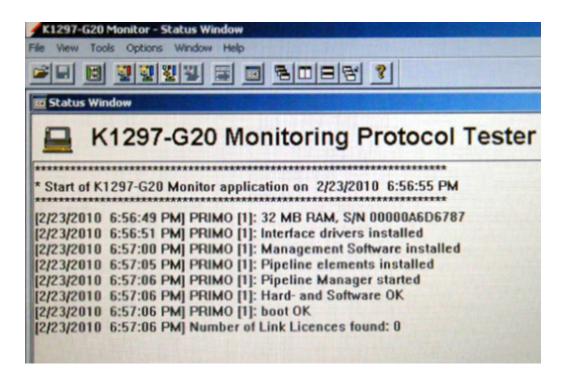

| Figure 6-5 (a) K1297-G20 Signaling Analyzer (b) The Interface of K1297 | 84   |

| Figure 6-6 K1297-G20 System Configration Status                        | 85   |

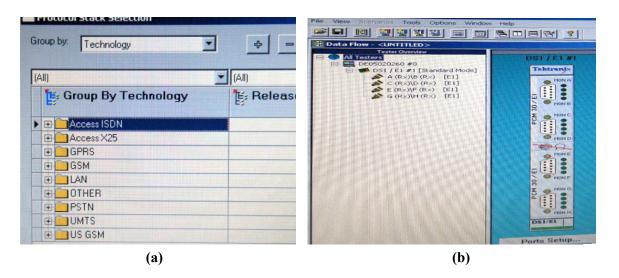

| Figure 6-7 (a) Test Type Options (b) Data Flow Setup                   | 86   |

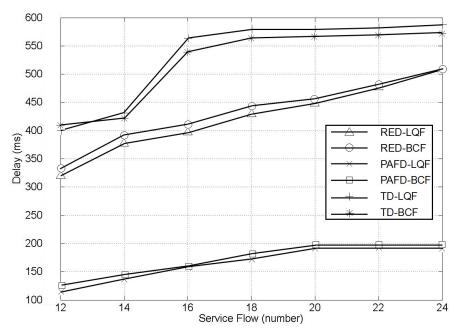

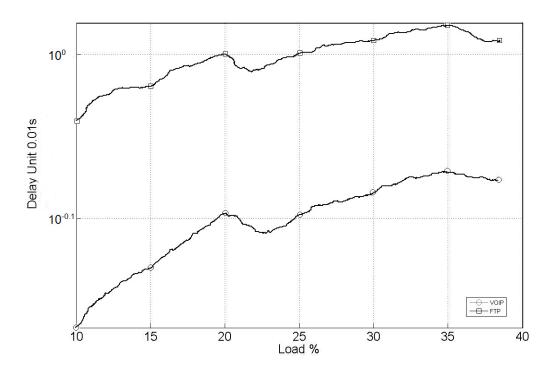

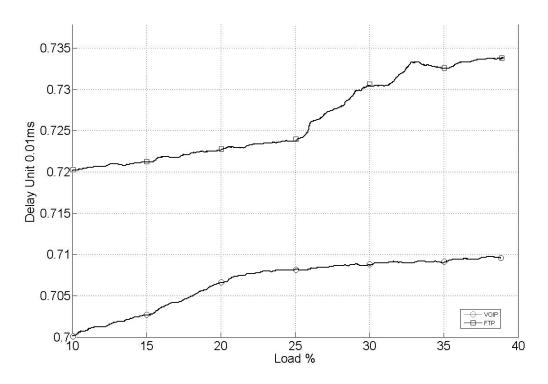

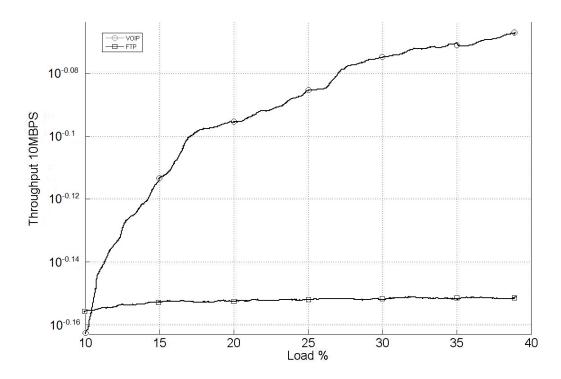

| Figure 6-8 Delay for Test Case 1               | 88 |

|------------------------------------------------|----|

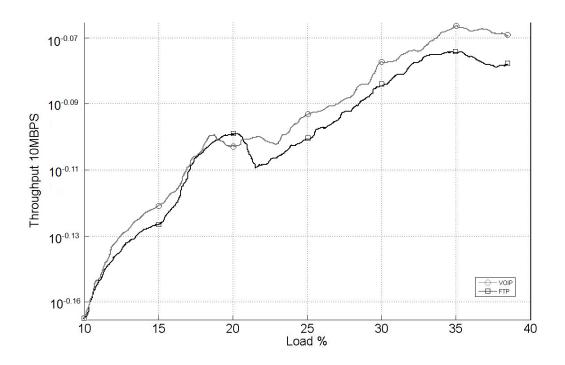

| Figure 6-9 Throughput for Test Case 1.         | 89 |

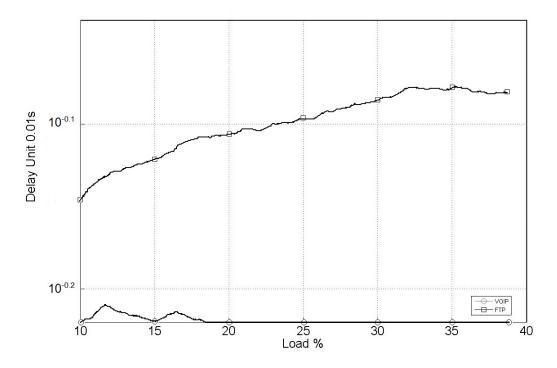

| Figure 6-10 Delay for Test Case 2              | 90 |

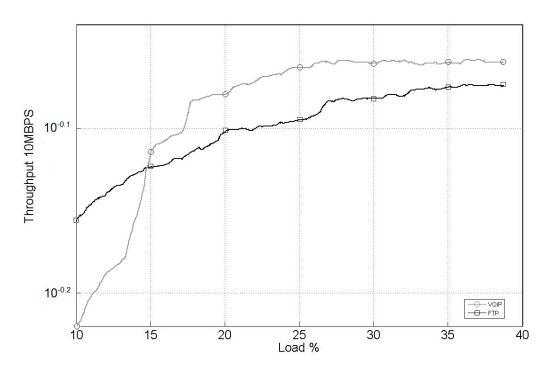

| Figure 6-11 Throughput for Test Case 2         | 90 |

| Figure 6-12 Delay for Test Case 3              | 91 |

| Figure 6-13 Throughput for Test Case 3         | 91 |

| Figure 6-14 System Test Structure              | 93 |

| Figure 6-15 Startup Delay Comparison Diagram   | 96 |

| Figure 6-16 System Capacity Comparison Diagram | 97 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 General Statement of Problem Area

As the development of 3G, 3G QoS has become the research focus of the network carriers. Wireless communication systems based on switch circuits will eventually evolve into an end-to-end all-IP network, which uses IP networks as the core, and wireless networks as the access approach. It also provides voice, video and multimedia operations with QoS assurance mechanisms [1]. QoS is a kind of measurement for desired performance and priorities of a communication system, which is designed to apply to downlink and uplink connections. As the main model of 3G, Wideband Code Division Multiple Access (WCDMA) has become mature after years of development. It uses a similar structure as Global System for Mobile Communications (GSM) including the Core Network (CN) and the Radio Access Network (RAN) [2-3]. The CN processes voice and data services, and has the capability of switching and routing to external networks. WCDMA CN and all-IP networks are the trend of 3G development [4-5], and the problem of QoS for WCDMA CN is the extension in mobile communication networks [6].

The QoS assurance provided in IP networks is the development trend of the next generation network (NGN) [7]. IP QoS research aims at providing an effective end-to-end QoS control or assurance. A lot of service models and mechanisms, offering different

levels of QoS assurance for IP networks, have been recommended and standardized, in which the most common ones are IntServ/RSVP (Integrated Services/Resource Reservation Protocol) and DiffServ (Differentiated Services). Compared to the IntServ model, the DiffServ model has better scalability, and can better adapt to the mobile wireless environment, especially suitable for large-scale backhaul networks. Koodli [8] pointed out that the DiffServ model is the most effective method to provide WCDMA CN with QoS guarantee under the current technical condition.

Compared with GSM CN, WCDMA network is committed to providing different types of service with QoS. To achieve the smooth transition of the CN from GSM to WCDMA, the General Packet Radio Service (GPRS) was introduced. GPRS adds packet switching to circuit-switched mode. The Non-Access Stratum (NAS) of WCDMA is horizontally divided into two sub-layers, i.e. mobility management sub-layer and connection management sub-layer. GPRS vertically belongs to two surfaces, i.e. control surface and user surface. Control surface is used for data transmission and processing, while the user surface is for the transmission of user data. The entities which complete the packet-switched service belong to the packet domain. In order to support packet-based operations, two network entities are added. They are Service GPRS Support Node (SGSN) and Gateway GPRS Support Node (GGSN). GGSN uses router architecture that based on NPs. SGSN uses an architecture that includes Asynchronous Transfer Mode (ATM) switches and NP forwarding board. Therefore, the realization of QoS function for WCDMA CN depends on the research and application of NPs. The NP will be the core

technology promoting the next generation high-performance networks. A lot of current research concentrating on its structure and applications has become a hot topic.

In the WCDMA system, communications between user nodes and internet hosts must be transmitted via the CN. The quality of WCDMA CN services directly impacts user's perceivable feeling. Recently, a lot of QoS realization mechanisms of mobile communication networks have been proposed [9-10], which are constrained in the RAN. Research on QoS for WCDMA CN is still limited. Furthermore, designs of fixed network QoS mechanisms are valuable [11-12], but they do not meet service structures and QoS requirements of WCDMA CN. For various types of QoS operation requirements of WCDMA CN, it is necessary to study the corresponding system models and realization mechanisms.

#### 1.2 Significance of the Study

Compared with the previous mobile communication technology, one of the advantages of 3G is that it gives the carriers more freedom in managing QoS. So that QoS becomes a network management mechanism with strict quantitative definition from a vague concept. From service carriers' perspective, carriers can improve the competitiveness by providing high value-added services in a network, in which an effective control and monitoring of QoS can be carried out. They can also develop different operating strategies for different user services, so the resource utilization can be improved. Since the end-users experience the end-to-end QoS, the carriers are most concerned about how to ensure end-to-end QoS in WCDMA networks.

To provide differenciated QoS will definitely become the trend of future networks, based on the facts below:

- The diversity of 3G shifts the attention from price to value.

- The emergence of multimedia services makes people concern more about business experience.

- 3G service diversity makes business model and resource allocation model more complex.

- The diversity in services of 3G makes the design of 3G networks novel, and more complex.

Enhancement of QoS for WCDMA CN definitely improves consistent response time, display distortion and sound image synchronization to increase network efficiency and save network resource.

#### 1.3 Research Premise

The main purpose of this study is to implement the DiffServ model of QoS for WCDMA CN. In WCDMA CN, the main network nodes in Packet Switched (PS) domain come from NPs. Due to this characteristic, this research mainly introduced programming models of NPs and key mechanisms to realize the DiffServ model of QoS for WCDMA CN. Based on the proposed programming model and algorithms, an integrated system is designed to realize the DiffServ model of QoS for WCDMA CN.

#### 1) Programming models of NPs:

- A comprehensive programming model which combines existing programming models will be designed.

- A solution will be proposed to solve packet ordering and resources exclusive issues.

- 2) Key realization mechanisms of DiffServ QoS for WCDMA CN:

- The buffer management algorithm: According to the QoS features of WCDMA, a novel algorithm which supports DiffServ will be designed. This algorithm can take consideration of both fairness and throughput, with smooth service curves, and it can also be adjusted in accordance with network traffic.

- The packet scheduling algorithm: By analyzing QoS characteristics of different WCDMA service types, this dissertation will introduce an improved algorithm, which can ensure the fairness of packet scheduling, and reduce queue time of data packets. The algorithm can also keep the delay and wobble within a minimum range, and its performance can be evaluated through a mathematical model of WCDMA packet data.

- The packet classification algorithm: Based on packet compress, rule merger and other algorithms, a new algorithm will be proposed to improve the lookup efficiency, gain desired time and space complexity.

- 3) Based on a comprehensive programming model and three algorithms proposed in this study, an integrated hardware and software system will be realized on GGSN and

SGSN equipment based on IXP2400. The effectiveness and performance of the proposed system will be tested by simulations which consist of DiffServ test and system test.

#### 1.4 Research Methodology

WCDMA CN is an IP network which provides the CN bearer services and the associated QoS guarantees. It consists of GGSN and SGSN nodes, and uses tunneling technology to forward packets. In order to use the DiffServ model for QoS control in WCDMA CN, the following issues need to be solved:

- 1) Appropriate access control schemes must be involved in the design of QoS management functions in the control plane.

- 2) A variety of WCDMA services must be mapped to Per Hop Behaviors (PHBs) of the DiffServ domain in the design of QoS management functions in the data plane.

Many papers have thoroughly done studies on QoS management in the control plane. However, this study mainly focuses on QoS management in the data plane, which consists of buffer management, packet scheduling and packet classification schemes.

In this dissertation, we used the research method of comparing and empirical study. Firstly, we analyzed and compared the traditional NP programming models, queue management and packet classification algorithms, and pointed out the existing shortcomings. Then, we designed new programming models and algorithms; significance and efficiency of the new algorithms were also tested carefully for the feasibility. Finally, based on the new programming model and algorithms, an integrated hardware and

software system of DiffServ QoS for WCDMA CN was realized on IXP2400. The research is based on Intel IXA framework and development tool SDK3.0, and the simulation was carried out on K1297-G20 Protocol Tester, Microsoft Visual C++ 6.0 and Microsoft Media Server.

#### 1.5 Organization

The study is mainly conducted on QoS for WCDMA CN. Based on summarizing and analyzing the existing research works, a comprehensive programming model for the NP and several new algorithms for QoS control in WCDMA CN were proposed. An integrated system of DiffServ QoS for WCDMA was designed. The main contents of this dissertation are as follows:

Chapter 1 summarized the development of 3G CN and the structure of CN equipment. The DiffServ model of QoS for WCDMA CN was proposed. This chapter also concludes that the NP is an ideal hardware platform to achieve DiffServ QoS for WCDMA CN.

Chapter 2 analyzed the QoS structure of WCDMA CN. Compared with the IntServ model, the advantages of the DiffServ model are outstanding. Realization mechanism of DiffServ QoS was also introduced.

Chapter 3 introduced the research on the NP architecture. In-depth description is carried out on the parallel feature and programming models of NPs. Solutions were proposed to solve sharing conflicts and packet ordering problems that are encountered in

applications. A comprehensive programming model was proposed as the implementation model of DiffServ QoS for WCDMA CN.

In Chapter 4, Queue management is divided into two aspects, buffer management and packet scheduling. A new buffer management algorithm called PAFD and an improved packet scheduling algorithms called PWFQ were proposed. Theoretical analysis and experiments showed that the algorithms had the following characteristics: (1) to guarantee fair bandwidth allocation, (2) to provide determined upper bound of the delay, (3) to offer less computational complexity, and (4) to take full advantage of the hardware features of network processing.

Chapter 5 proposed a fast packet classification algorithm called CBNPs by using regulation compression and parallel tuple search technology. This algorithm reduces the number of classification rules and classification domain width to accelerate the classification process. It also has high-speed, multi-dimensional and scalable features.

In Chapter 6, based on the programming model and all algorithms proposed in this study, an integrated hardware and software design of DiffServ QoS for WCDMA CN was introduced. The simulation results showed that the proposed system has much better performance than others.

Chapter 7 summarized the research work performed in this dissertation and proposed further research directions.

#### **CHAPTER 2**

# REALIZATION MECHANISM OF DIFFERSEV QOS FOR WCDMA CN

#### 2.1 Introduction

WCDMA networks allow us to provide a variety of communications services in service networks and home environments. The objective of them is to provide a single integrated system. Users can access this system using standard method in a variety of environments. WCDMA defines a number of architectures consisting of logic components with specific functions. An end-to-end WCDMA system includes User Equipment (UE), Universal Mobile Telecommunications System (UMTS) Terrestrial Radio Access Network (UTRAN), the CN as well as external networks. WCDMA UTRAN is formed by a group of Radio Network Subsystems (RNS), which are access part of UE in the PS domain. It is responsible for achieving the majority of air interface. WCDMA CN is an IP network which can provide the CN bearer service and the associated QoS assurance [13]. It consists of GGSN and SGSN nodes, and handles all calls, bearing service support and controls related functions. SGSN implements the mobility management, security management, access control and routing functions. GGSN is responsible for providing interface of GPRS to the outer packet data network. It also provides necessary inter-network security mechanisms, such as firewall.

The QoS problem in WCDMA networks is more complex than that of general IP networks. Restriction of wireless interface must be taken into account when QoS services are implemented. The complex QoS mechanisms in the fixed network [14] are often unable to adapt to the high error rate at wireless interface. Due to the constraints and robustness of wireless interface, the 3rd Generation Partnership Project (3GPP) [15] defines four types of QoS for WCDMA: Conversation Class, Stream Class, Interaction Class and Background Class. These classifications are based on the delay sensitivity of different operations [16].

WCDMA CN supports services of different QoS levels. Each service is described by a group of QoS parameters. This set of parameters determines the scope of WCDMA bearer services that users can have, and describes the property of users' WCDMA bearer services, which includes the maximum transmission rate, guaranteed transmission rate, transmission order, the largest service data unit, service data unit format, service data unit error ratio, residual error ratio, transmission of the error service data unit, transmission delay, and service process priorities. By treating service types as attributes, WCDMA can first assume the source of a service operation, and then optimizes the transmission of this service.

WCDMA is capable of providing voice, data and multimedia with end-to-end QoS support. Because characteristics of various types of services are significantly different, they require different load-bearing characteristics. 3G network should adopt the appropriate control mechanisms to meet the QoS requirements of different services. For

the WCDMA network which is based on packet switching, it is particularly important to develop a reliable QoS management mechanism to meet the demand of 3G services.

#### 2.2 WCDMA QoS Architecture

3GPP proposed a hierarchical structure shown in Figure 2-1, which supports endto-end QoS assurance. In order to achieve QoS in WCDMA networks, between the start and the end of service, bearer services whose properties and functions are clearly defined must be established.

Figure 2-1 WCDMA QoS Structure

In WCDMA networks, the end-to-end service can be decomposed into the terminal equipment/mobile terminal (TE/MT), the local bearer service, WCDMA bearer services and the external bearer service. During the delivery of a service flow from one TE to another TE, the flow must go through different network bearer services. TE/MT

local bearer service is responsible for the communication between various components of a mobile station (MS). These components can be MTs, and one or multiple of the connected TE. The MT is responsible for physical connection of air interface to WCDMA UTRAN. The TE is connected to the WCDMA network through the MT. The end-to-end services in the application layer uses the underlying network bearer services to provide various services to achieve WCDMA QoS [13]. The external bearer services are responsible for connections between the CN and external network terminals.

WCDMA bearer services are realized by the Radio Access Bearer (RAB) services and the CN bearer services. These two services reflect an optimized method to achieve WCDMA bearer services in their respective network topology. Factors to be optimized include the mobility and mobile user properties. The RAB services can provide confidential delivery of signals and user data between the MT and CN Iu edge node, and also satisfy the negotiated QoS of WCDMA bearer services or the default QoS of signals. The CN bearer services connect the CN Iu edge node and the CN gateway to the outside network to effectively control and use the backhaul network to provide the corresponding WCDMA bearer services. WCDMA CN can support various backhaul network bearer services with different QoS requirements.

The CN bearer services use the common backhaul network services, including the functions of the first and second layers of the network. These functions can be chosen according to the needs of network carriers to meet QoS requirements of the CN bearer services. WCDMA does not define the backhaul services, so it can take advantage of the

existing standards. For example, the WCDMA R99 version uses the ATM standard directly, while the bearer services of the IP-based CN use the IETF IP protocol instead.

#### 2.3 DiffServ QoS Model

#### 2.3.1 DiffServ Architecture

DiffServ uses the classification standard of IntServ. However, it removes the complex admission control algorithms and end-to-end resource reservation protocol. The scalability of DiffServ is improved by classifying and marking the traffic at the edge routers. Moreover, DiffServ does not need complex signaling, so it is particularly suitable for large-scale backhaul networks.

At the edge of the network, DiffServ classifies and forms the single flows entering the network into different flow aggregations. They are then mapped to pre-defined categories. Only a small number of these categories are saved at the core of the network. The router treats the categories of flows differently by using different buffer management and queue scheduling algorithms, and the different treatments brings different service levels. First of all, users and network carriers have to sign a Service Level Agreement (SLA), which defines performance indicators and user flow characterizations. Users pay for data within the scope described in SLA, and the network provides the data with QoS assurance. For the data not specified in the SLA, the network does not provide QoS assurance, or the service level will be reduced.

When the user traffic enters the network, an edge router measures and classifies the traffic. The user's flows are aggregated into a flow aggregation. The aggregated information is stored in each IP header code point, which is used to tag flow aggregation belonging to IP packets. DiffServ Code Point (DSCP) is located in Types of Service (TOS) at IPv4 header or in Categories of Service (COS) at IPv6 header. Network core equipment conducts scheduling and forwarding according to DSCP, and its external characteristic is called PHB. Overall, the corresponding, forwarding and scheduling behaviors of PHBs are the division of priority. Virtually every PHB corresponds to a priority level. The parameters of each priority specify different requirements on delay, jitter, and packet loss rate. The essence of PHB is the method of resources allocation of each router in DiffServ area for specific flow aggregation. The current standardized PHB includes the default type Best Effort (BE), Class Selector (CS), Expedited Forwarding (EF) [17], and Assured Forwarding (AF) [18]. AF consists of four PHBs. Each Internet Service Provider (ISP) can define different TOS according to their actual needs, such as reward service through EF and Olympic service through AF.

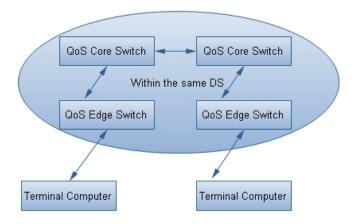

The DiffServ model uses a hierarchical structure in different ISP networks for coordination. A single ISP network constitutes a DiffServ (DS) domain, and multiple DS domains constitute one DS zone. In a DS domain, the behaviors of DiffServ scheduling forwarding are consistent. DS domains in the same DS zone have to be connected through the edge routers. By using Traffic Condition Agreement (TCA), DS domains provide the cross-DS domain services to ensure consistency in the provision of services to users.

#### 2.3.2 DiffServ Features and Advantages

By studying the DiffServ model, we can summarize the main features of the DiffServ model:

- 1) There is a sharp distinction between functions of edge routers, core routers and hosts. In the DiffServ model, the routers are further divided into edge routers and core routers. Edge routers keep the per-flow state, SLA information, packet classification, and marking. Core routers do not hold per-flow information, but only keeps a small number of classified information. The core routers also provide different types of packet with different priority treatments.

- 2) There is a clear contractual relationship between hosts and networks. SLA describes the services that user can expect and the user flow specifications. Difference between SLA and FLOWSPEC which is a list of parameters in IntServ is that SLA is a long-term, static service specification, and the later expresses the exact description for the flow specification of a specific QoS request.

- 3) Core routers provide different levels of services. In the DiffServ model, the core routers in the backhaul network have only a small number of queues, and flows are converged to a coarse-grained flow aggregation, so that the network can maintain high statistical multiplexing features.

- 4) The DiffServ model offers a variety of levels of services. According to different bandwidth and delay requirements, DiffServ can provide multiple levels of

services through different PHBs. From an architectural point of view, DiffServ has the advantages of both IntServ and the traditional Best Effort model. This model maintains the good statistical multiplexing characteristics of the Best Effort model, and has good scalability.

DiffServ is an ideal QoS implementation mechanism in WCDMA CN under the current technology, because

- 1) The DiffServ architecture and WCDMA CN structures have a certain similarity, therefore the renovation cost is relatively low. SGSN in WCDMA CN is equivalent to the entrance router in DiffServ, so mapping the WCDMA QoS to DiffServ DSCP to achieve the corresponding PHB is all the works. GGSN is similar to the edge router which can improve the flow control function, achieve the inter-regional differential services, and ensure the consistency of QoS.

- 2) DiffServ does not need complex control signaling, and its good scalability makes it suitable for wireless communications, especially as the QoS control mechanisms in large-scale backhaul networks such as WCDMA CN.

- 3) Due to the high error rate of wireless interface and heterogeneous network compatibility, WCDMA does not define precise QoS requirements for different TOS. Thereby, this property perfectly matches the characteristic of DiffServ, which does not perform fine granularity QoS control based on the flow aggregation.

#### 2.4 DiffServ QOS Realization Mechanism

#### 2.4.1 DiffServ Realization Framework

Different from the IntServ model, the core switch in the DiffServ model forwards and schedules the data packets based on a limited number of COS, rather than the specific circumstances of a session streaming. This requires an important QoS mapping process at the terminal. The physical framework of QoS mapping is different based on different DiffServ implementations. However, a key mapping link in always there. The data packets are mapped into the appropriate COS based on the Relative Priority Index (RPI). In order to satisfy different applications and reduce the edge exchange process, these mapping processes are implemented at the end systems. QoS mapping is an important technology in the implementation of DiffServ. The network edge router provides the services and QoS assurance based on the service category in the specific data packet header. The client can request an overall consideration of QoS requirements and service charges, and map the packets into different service categories, so that the data packets have the corresponding QoS guarantee in the network. Overall the QoS mapping is the basic scheme for DiffServ.

In the DiffServ model, the services are sorted into *i* categories based on the parameters of QoS, and COS is a set of related QoS parameters. The DiffServ model is reflected as follows: If data packets request category *i*, the edge router provides services according to the standard specified by the QoS parameter set of category *i*. COS is a carrier that transmits QoS information between the terminal and network. According to

whether the defined type of services has global consistency, DiffServ implementation is divided into two types: absolute implementation and relative implementation. Absolute implementation can provide a more secure end-to-end QoS, but its structure is more complex, and the flexibility and scalability are poor. When the sender conducts adaptive coding and the network edge routers are more intelligent, relative implementation is more flexible and efficient than absolute implementation. In order to separate the encoding details and the network self-adaptive function, we need to define an appropriate evaluation criterion by which each packet is marked with one RPI to correctly represent the importance of the packet in the flow and integrate a variety of factors. An important part to achieve DiffServ QoS is to determine the corresponding DiffServ COS based on the RPI of each data packet, which is so called QoS mapping.

#### 2.4.2 DiffServ Realization Mechanism

The DiffServ architecture provides theoretical principles and framework basis for implementation of QoS guarantee mechanism in the IP backhaul network. The specific usage strategies and the corresponding realization of the mechanism are decided by different manufactures. QoS realization mechanism in the DiffServ model is the key to provide QoS guarantee for users. It mainly consists of buffer management, packet scheduling and packet classification mechanism [19-20].

1) Buffer management mechanism is designed to solve the packet-discard problem, when network congestion happens. If the network congestion occurs at the output port, the router buffers must discard some packets to improve the output flow of

the buffer queue. How to reasonably drop some packets is mainly determined by the buffer management algorithm.

- 2) Packet scheduling mechanism is the queuing and regulation methods used on data flows to prevent congestion at the network output ports. This mechanism determines how a router selects the next packet from one or more buffer areas and forwards it. Main performance indicators for an efficient packet scheduling algorithm include fairness, delay characteristics, isolation capacity of malicious traffic flow, link bandwidth utilization, and complexity.

- 3) Packet classification mechanism is mainly used in classifiers and regulators in the DiffServ model. This mechanism ensures that input data flows accord with the Traffic Conditioning Agreement (TCA) and classifies the flows to a certain behavior aggregate, and then tags them as packets correspondingly. The classifier follows the specific rules in TCA to assign packets to a category according to the fields in header such as the DSCP value or the five-factor group of MF, and then hands this category over to the appropriate regulator module for further processing.

In the DiffServ model, EF PHB provides low packet loss rate, delay, and jitter to guarantee bandwidth services. AF PHB is responsible for providing a flow range in the DiffServ domain. The packets within the flow range can receive ensured QoS, and those beyond the range cannot receive guaranteed QoS. AF PHB provides four independent forwarding AF categories, and each category has three different packet loss priorities. BE is suitable for the traditional Internet service, but does not guarantee QoS.

According to 3GPP requirements, UE makes the request of QoS by mapping QoS requirements in the end application layer to the Packet Data Protocol (PDP) parameters via an application layer protocol such as the Session Description Protocol (SDP). The management function of WCDMA QoS decides whether to accept the request based on the resource utilization in the UTRAN, SGSN and GGSN. Once the request is allowed, the DiffServ edge node defines the classifier settings and maps different QoS COS to different PHBs based on the DiffServ framework in IP networks. Downlink WCDMA QoS is controlled by a remote host to the GGSN. Then GGSN uses the DiffServ edge function to re-classify the data flow by re-encoding DSCP, and assigns the data to different PDP through DSCP. UE is responsible for controlling PDP content in the process, while GGSN is responsible for providing interaction between the PDP content and DiffServ. The control range of PDP flows is limited to access network part of the WCDMA system between UE and GGSN.

Figure 2-2 shows the detailed interactive flow of QoS control information, in which RAP is the remote access point, and RUE means the remote UE. GGSN completes the conversion from PDP to DiffServ in the uplink, while in the downlink the Flow Template (TFT) completes the conversion from DiffServ to the PDP flow through the TFT filters.

Figure 2-2 Control Information Interactive Process

In the WCDMA COS, the conversation and stream classes which are delay-sensitive are mapped to EF and AF1 PHB, respectively, while the interaction and background classes are mapped to AF2 and BE PHB, respectively. Each type of AF PHB can be divided into different sub-types. For example, the interaction services with different QoS requirements can be mapped to AF2 subtypes such as AF21, AF22 and AF23. The mapping from different WCDMA COS to DiffServ PHBs is not unique. It mainly reflects the different QoS requirements of various COS. The QoS control of these service flows is directly determined by queue management algorithms, which include buffer management and packet scheduling algorithms.

#### 2.5 Summary

In this chapter, the WCDMA QoS requirements in 3GPP agreement were analyzed. It is pointed out that the QoS problem in the CN is an extension of QoS problem in IP networks. By studying on the DiffServ structure, we find that the DiffServ model is more suitable to achieve QoS for WCDMA CN than IntServ. There was also an in-depth analysis of the QoS mapping approach in the DiffServ model and of the realization mechanism in this chapter. The DiffServ model of QoS is mainly implemented in the data planes of GGSN and SGSN which are the main entities of WCDMA CN.

#### **CHAPTER 3**

# HARDWARE PLATFORM AND PROGRAMMING MODEL OF DIFFSERV QOS FOR WCDMA CN

#### 3.1 IXP2400 NP Overview

As the network scale and interface speed are both increasing, network equipment based on a common Reduction Instruction Set Chip (RISC) technology cannot meet the performance requirements of line-speed processing. On the other hand, new network communication protocols and standards are emerging and changing, and the user's demand is also constantly evolving. As a result, the product cycle of data communication products is greatly shortened. In this background, an NP with both high-speed processing and flexible programming capability provides a flexible solution for design of the next generation communication products [21-23].

An NP is a general purpose chip that dedicates to network communication equipment, which supports an open, diverse, and programmable development environment. In the NP environment, different equipment vendors can use the same chip to create their own network equipment with different functions and features. An NP combines the advantages of RISC and Application Specific Integrated Circuit (ASIC). Just as RISC, an NP is programmable and provides sufficient flexibility to adapt to the fast development of data communication market. It also has high performance as ASIC, but does not take a very long development period. An NP takes into account both

flexibility of RISC and implementation efficiency of ASIC, and also provides good support for the second-layer to the seventh-layer applications. By downloading different programs, the same hardware platform can support Virtual Local Area Network (VLAN) switches, routers, broadband remote access servers, NAT, firewall, WEB switches and so on. It supports all speeds of Ethernet, ATM, POS and other interfaces, so it is very convenient for upgrading [21].

An NP has a typical multi-core RISC parallel real-time processing architecture. It carries out real-time tasks of packet processing and network bandwidth management. An NP usually consists of a general-purpose processor and multiple parallel or pipelined data packets Processing Engines (PEs) and each internal PE supports multiple threads. Intel's IXP2400 is an NP launched after IXP1200. This NP is based on Intel Exchange Architecture (IXA) [22], and supports 2.5Gbps applications, with eight 600MHz microengines and a 600MHz processing core XScale. One double-data-rate (DDR) SDRAM and two quad-data-rate (QDR) SRAMs can be added to it. IXP2400 also supports standard Media and Switch Fabric (MSF) interface standard SPI-3 or CSIX-L 1. Its Micro-engine processing power is suitable for data packet forwarding and other functions. Eight micro-engines can forward three million packets in Layer 3 per second. The XScale processor can be used to handle complex tasks, such as address learning, establishing and maintaining forward table, and network management. IXP2400 provides high-performance parallel processing capability, with various levels of scalability. Combining the XScale microprocessor with eight separate 32-bit RISC micro packets forwarding engines, as well as hardware multi-threading support, IXP2400 can achieve

5.4G operations per second to support a wide variety of WAN and LAN applications. By improving the micro-engine architecture, IXP2400 achieves high performance and scalability. These improvements include multi-threading allocation and high-speed cache which gives the software pipeline feature.

#### 3.2 IXP2400 Functional Modules

IXP2400 contains eight programmable 32-bit RISC processors which are called micro-engines [23]. The micro-engines are dedicated to handling network traffic. Each micro-engine has eight program counters for eight threads such that we can execute ALU and shift operations in one clock period. Micro-engine instruction set is a data type designed to quickly and efficiently forward packets for networking and communications applications. The set includes bits, bytes and long words.

Micro-engine uses the multi-threading feature, so no extra clock time is needed for thread switching overhead. Each thread has its own thread ID, allowing for the visit results to be returned directly to the requesting thread. When a thread of micro-engines sends a fetch request, this thread switches itself out to let other threads run. It waits for the results from memory and then switches back to run. Thread-switching does not require interrupt mechanism, but is under the control of the micro instructions. This thread switching mechanism can take full advantage of the visit deposit gaps, to improve the micro-engine utilization and throughput.

Figure 3-1 IXP2400 Main Functional Units

Figure 3-1 shows a simplified block diagram of IXP2400 main functional units, and the functions of these units are described as below [24].

- 1) XScale core: It is a complete 32-bit RISC processor with high-performance, low power consumption and compact layout features. It comes with an integrated cache which can be used to achieve management functions, running routing protocols, exception handling and other functions. This unit is applicable to be integrated with other specific operational units in a single chip.

- 2) Eight micro-engines: These highly efficient RISC engines can be used on any demand for quick detection, data processing, and transmission of packet contents. They are fully programmable 32-bit engines with 5 levels of large pipelined register groups. These micro-engines are multi-threading, and can conduct fast context switching in context-sensitive register windows.

- 3) Peripheral Component Interconnect (PCI) bus interface module: This module is a standard interface, which provides possible connection to other PCI devices or other host processors. The PCI interface can reach speed of 133MHz, but this maximum available speed is limited by the PCI bus protocol and bandwidth. There is no internal direct connection between the PCI unit and micro-engines, so PCI is not the primary means of IXP2400 data access.

- 4) SDRAM, SRAM and Scratchpad RAM modules: The SDRAM module is a shared, intelligent memory interface, which can be accessed by the XScale core, microengines and equipment on the PCI bus. The SRAM module is also a shared intelligent interface, which can be accessed from the XScale and the micro-engine. Scratchpad RAM has small space in IXP2400, and its delay is also very short. It is often used in internal communications, and for shared semaphore and counters. These three storage resources SRAM, SDRAM, and Scratchpad RAM are different in capacity and bandwidth. The benefits of having all three types of storage are that each of these memory operations can be carried out in parallel, and programmers can also select different storage resources based on the requirements of performance. For example, SDRAM memory is suitable for data packets storage and extra large tables, and SRAM memory is for lookup table with shorter delay.

- 6) MSF interface module: The interface is used to connect IXP2400 to a physical layer device (PHY) and/or to a Switch Fabric. The MSF consists of separate receive and transmit interfaces, which are unidirectional and independent of each other.

### 3.3 Advantages of Using IXP2400 to Achieve DiffServ QoS

To accelerate the delivery ability of new network services, Intel is providing network equipment vendors and network service providers with the latest second-generation Intel IXA NPs. Each NP family is optimized to meet the requirements of target network segments, and is complemented by software tools and development platforms to reduce development cost. We choose IXP2400 as the hardware platform to achieve DIFFSERV QoS for WCDMA CN based on the following reasons:

- 1) Multi-micro-engine and multi-threading technologies: Each micro-engine is a fully programmable, multi-threaded RISC processor subsystem. It enables high-performance packet processing in the data plane. When the system is running, each micro-engine deals with only one task. During the thread switching, there is no need for protection. This is because each thread has its own register. So the switching speed is very fast.

- 2) XScale technology: Intel XScale core is designed to control the application processing and for low-layer communications. It manages and updates the data structure shared by routing tables and micro-engines, and establishes and controls the communication media and switching devices. Because the XScale micro-architecture uses the hyper-pipeline technology, it can achieve a relatively high performance. The multi-process and efficient instruction-layer processing pipeline architecture makes the reaction time be reduced to the minimum, and the clock speed is also selected to achieve ultra-low energy consumption.

3) IXA mobile architecture technology: As described above, Intel IXA mobile architecture provides us with advanced design architecture, so that we can develop products quickly and efficiently.

# 3.4 IXP2400 Programming Models

In general, the data packet processing tasks in practical applications tend to be more complex, so they require multiple micro-engines to work in parallel. This involves how to distribute complex and arduous data tasks among a number of micro-engines, that is, what kind of method can be adopted to map the packet processing tasks to the specific micro-engines. Micro-engine programming model problem is a macro level strategic issue [25], and the study of this problem focuses on how to distribute the data packets among multiple micro-engines in order to obtain the highest processing performance. Micro-engine programming model is universal, not only applicable to eight micro engines in IXP2400, but also to sixteen micro-engines in IXP2800 and the future NPs with more micro-engines.

Packet processing tasks in most applications are complex and diverse, while the micro-engines are fully programmable, so the micro-engine programming models are varied, and are also more flexible choices according to the actual situation. In the following, we introduce two micro-engine programming models. One is known as the super-task chain model such as HTC (Hyper Task Chaining) [26], and the other one is the thread pool model such as POTs (Pool of Threads) [27]. No matter what kind of programming model is chosen, the model must effectively solve two important problems

in the packet processing. One is maintaining packet ordering, and the other is the thread mutual exclusion problem when multi-threads need to access the same data structure. In mutual exclusion, when a thread is using a data structure for operation, the data structure should be locked to prohibit the use by other threads in order to avoid undermining the integrity of the data. This problem is divided into two situations including inside microengine and among multi-micro-engines. In this chapter, we mainly discuss mutual exclusion encountered in the multi-micro-engine parallel processing problems and the corresponding solutions. Some applications require IXP2400 to maintain the order of packets during the process, and let the data packets leave the IXP2400 according to the arriving order. For example, when dealing with the compressed IPv6 packets, the current data is compressed based on the previous packet, therefore only after the previous packet is processed, the current data packet can be processed. In a word, data packets should be processed in order, which is the so-called packet ordering problem.

#### 3.4.1 The HTC Model

HTC is a pipeline style packet processing model [26, 27]. In this model, the duration of each data packet processing time is relatively fixed, and pre-calculated. Therefore, HTC model is commonly used in the situation that most of the data packets are similar (mainly refers to the case that the packet processing complexity and processing time are basically the same), as well as the situation that data packets belong to the same data flow. In the latter case, we can use the LM, Q-Array, CAM and other hardware structures to quick-fix mutual exclusion problem. In general, using the HTC model for data packet processing can achieve relatively certain processing performance.

HTC divides a large data packet processing task into several small data packet processing sub-tasks, namely, Network Function = Task 1 + Task 2 + Task 3 + ... + Task n, Each sub-task can be organized and combined to get another large data packet processing task. There are two combination models as follows:

- 1) Function Chaining: By using time-division, multiple packet processing tasks are combined in a micro-engine to form a large data packet processing task. To enhance the parallel processing capability, we use multiple micro-engines to run the same packet processing program to process multiple packets. The Function Chaining method is generally suitable for the situation in which multiple processing and substantial changes need to be made for data packets

- 2) Context Chaining: This model allocates multiple sub-tasks to multiple microengines by using space-division, and then these micro-engines are combined together to form one large data packet processing task. Context Chaining is only used on implementation of single processing and minor modifications for packets.

In general, a series of data packet processing tasks get involved between receiving data packets and adding them into a queue. We can use Function Chaining to link a series of data packet processing tasks together and process them on one micro-engine. For a single micro-engine, packet processing tasks are very heavy, thus the execution speed of Function Chaining is slower than that of Context Chaining. However, we can use multiple micro-engines to work in parallel to improve overall system processing speed. In Context Chaining, one micro-engine is responsible for one packet processing sub-task,

and unlike the Function Chaining in which one micro-engine is responsible for multiple data packet processing sub-tasks. Therefore, Context Chaining is much simpler than the Function Chaining. This is because that the mutual exclusion problem among multiple micro-engines is not considered.

#### 3.4.2 The POTs Model

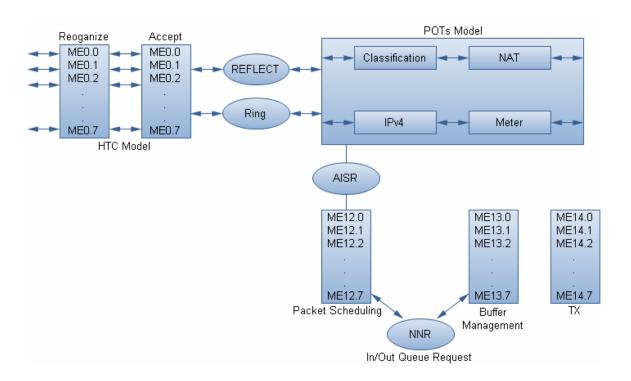

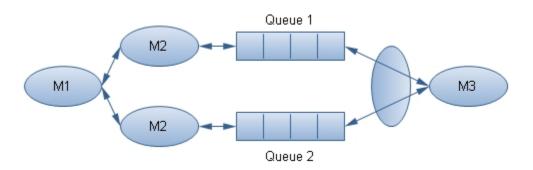

POTs is also known as "run-to-completion" model [27]. In this model, one program or thread executes most of the data packet processing tasks, such as a series of data packet processing tasks between receiving data packets and executing enqueue operation. The POTs structure is similar to that of the programming model of general-purpose processors, and has more understandability. The schematic model of POTs is shown in Figure 3-2, in which SPI is Serial Peripheral Interface, and NAT means Network Address Translation.

Figure 3-2 POTs Model Structure

Figure 3-2 shows that the POTs model is based on basic modules which are closely relevant to the underlying hardware architecture. These basic modules including Rx, Buffer Management, Queue Manager and Tx module, are equivalent to the hardware driver modules in the operating system of general-purpose processors. In POTs, DRAM is used for storing data packets, statistical database, forwarding information table and other large data structures. While SRAM memory device is used to store the information associated with data structures such as the packet descriptor, packet status information and Longest Prefix Matching (LPM) lookup table. When the MSF receives a data packet, the packet is cached in the Receive Buffer (RBuf), and then Rx module reads the packet from the RBuf for receiving and reorganizing processing. After that, POTs are used for classification, packet forwarding and other data packet front-end processing tasks. Next, Queue Manager executes enqueue operation, and the packet joins the sending queue. Then the dequeue operation is executed and the packet is removed from the queue. Finally, POTs are used again to complete the back-end data packet processing tasks.

# 3.5 Development of the Comprehensive Programming Model

In the above sections, we analyzed two micro-engine programming models HTC and POTs. Both models have their own advantages and disadvantages. In general, POTs is more flexible and simpler than the HTC, and its scalability is also better. For example, when the system hardware platform is upgraded from IXP2400 to IXP2800, the number of micro-engines is increased from 8 to 16. If POTs is used in this situation, there are no major changes on micro-engine programs. All we need to do is to add additional threads in the micro-engines to the free thread pool. However, HTC requires that the number of

packet processing sub-tasks equals to that of micro-engines, which means that we need to re-design the data packet processing procedures and re-divide the data packet processing tasks [28].

Assume that most of the data packets are basically the same, and the processing time are roughly equal, HTC is more efficient than POTs during serial processing. Because in HTC model, distributed cache such as CAM and LM can be used to quickly solve the mutual exclusion problem, and the Inter-Threading-Signal mechanism is relatively simple to solve the packet ordering problem. Conversely, POTs is more efficient than HTC if differences of the processing time among data packets are relatively significant. In this case, due to strict synchronization constraint between various threads of HTC, those threads that process packets with relatively short processing time are idle, and wait for other threads taking longer processing time. This results in waste of resources and decline in processing speed. While threads in POTs run independently, there are no strict synchronization requirements.

The comparison between HTC and POTs depends on the actual situation. As described above, if the majority of the data packet and their processing time are basically the same, we can use HTC module for fast processing of data packets. If the differences are relatively large, POTs model can be used for effective processing. In addition, if we take into account simplicity of program development and scalability of the corresponding platform, POTs is a more suitable micro-engine programming model.

For SGSN and GGSN, we proposed a comprehensive programming model which combines HTC and POTs to achieve the best processing efficiency. As shown in Figure 3-3, HTC and POTs can be combined to be responsible for front-end data packet processing tasks, while HTC is used for the back-end data packet processing tasks. We adopt HTC sub-model Context Chaining to let two micro-engines handle restructuring and receiving the packets, and then through the Reflector the packets are transmitted to the next packet processing modules which are achieved by POTs model. Once POTs completes the data packet processing, the Asynchronous-insert and Synchronous Remove (AISR) software mechanism of POTs is used to restore the sequence of the packets, and then the packets are sent to the back-end packet processing modules which are controlled by HTC sub-mode Context Chaining.

Figure 3-3 Comprehensive Programming Model Structure

# 3.6 Summary

WCDMA QoS must be implemented on the CN element nodes GGSN and SGSN, and the data planes of SGSN and GGSN are implemented on forwarding board based on NPs. An NP has high-speed processing and flexible programming capabilities, and it is an ideal hardware platform to achieve DiffServ QoS for WCDMA CN. In gerenal, an NP is different from a general-purpose processor in its operations and development methods, so we need to better understand it in order to efficiently achieve the differentiated QoS for WCDMA CN.

In this chapter, we presented in-depth analysis of two existing programming models HTC and POTs. A comprehensive programming model was put forward to solve the sharing conflicts and packets ordering problem. This model combines HTC and POTs and maps them to different QoS management modules. This model gets the advantages of the two existing models, and is highly efficient and flexible. We use this programming model to implement DiffServ QoS for WCDMA CN.

#### **CHAPTER 4**

# QUEUE MANAGEMENT ALGORITHM DESIGN

### 4.1 Queue Management Overview

Queue management plays a significant role in the control of network transmission. It is the core mechanism to control network QoS, and the key method to solve the network congestion problem. Queue management consists of buffer management and packet scheduling. Generally the buffer management is applied at the front of a queue and cooperates with the packet scheduling to complete the queue operation [29, 30]. When a packet arrives at the front of a queue, the buffer management decides whether to allow the packet to come into the buffer queue. From another point of view, the buffer management determines whether to drop the packet or not, so it is also known as dropping control.

# 4.2 Existing Buffer Management Algorithms

In recent years, the buffer management mechanism is a hot research area. A number of schemes have been introduced in this area. These designs adopt different control schemes for various situations. Based on basic principles of the buffer management control, the control schemes of the buffer management can be analyzed from two levels, data flow and data packet. In the data flow level if we view it from the aspect of system resource management, the buffer management needs to adopt certain resource management schemes to make a fair and effective allocation of queue buffer

resources among flows through the network nodes. In the data packet level and viewed from the aspect of packet dropping control, the buffer management needs to adopt certain drop control schemes to decide that under what kind of circumstances a packet should be dropped, and which packet will be dropped. Considering congestion control response in an end-to-end system, the transient effects for dropping different packets may vary greatly. However, statistics of the long-term operation results indicates that the transient effect gap is minimal, and this gap can be negligible in majority of cases. In some specific circumstances, the completely shared resource management scheme can cooperate with drop schemes such as tail-drop and head-drop to reach effective control. However, in most cases, interaction between these two schemes is very large. So the design of buffer management algorithms should consider both of the two schemes to obtain better control effects [31, 32].

The RED algorithm [33] was proposed for active queue management (AQM) mechanism [34] and was standardized as a recommendation from IETF [35]. RED introduces congestion control to the router's queue operations, and uses early random drop scheme to smooth packet dropping in time. This algorithm can effectively reduce or even avoid the congestion in network, and solve the TCP protocol global synchronization problem. However, one concern of the RED algorithm is the stability problem, i.e., the performance of the algorithm is very sensitive to the control parameters and changes in network traffic load. During heavy flow circumstances, the performance of RED drops drastically. Since RED algorithm is based on best-effort service model, which does not consider different levels of services and different user flows, it cannot provide fairness. In

order to improve the fairness and stability, several improved algorithms have been developed, including WRED, SRED, Adaptive-RED, FRED, RED with In/Out (RIO) [36, 37] etc. But these algorithms still have a lot of disadvantages. For example, a large number of studies have shown that it is difficult to find a RIO parameter setting suitable for various and changing network conditions.

### 4.3 Development of the PAFD Algorithm

This study proposed a new buffer management algorithm called PAFD (Packet Adaptive Fair Dropping). This algorithm adaptively gains balance between congestion and fairness according to cache congestion situation. When there is minor congestion, the algorithm tends to fairly drop some packets in order to ensure that all users access the system resources to their scale. For moderate congestion, the algorithm inclines to drop packets of low quality service flows by reducing its sending rate using scheduling algorithm to alleviate congestion. In severe congestion, the algorithm will tend to fairly drop packets, through the upper flow control mechanism to meet the QoS requirements, and reduces sending rate of most service flows, in order to speed up the process of easing the congestion.

In buffer management or packet scheduling algorithms, it will improve the system performance to have service flows with better transmission conditions reserved in advance. But this operation makes system resources such as buffer space and bandwidth be unfairly distributed, so that QoS of service flows with poor transmission conditions cannot be guaranteed. Packet scheduling algorithms usually use generalized processor

sharing (GPS) as a comparative model of fairness. During the process of realization of packet scheduling algorithms based on GPS, each service flow will be assigned a static weight to show their QoS. The weight  $\phi_i$  actually expresses the percentage of the service flow i in the entire bandwidth B.  $\phi_i$  does not change with packet scheduling algorithms, and meets

$$\sum_{i=1}^{N} \boldsymbol{\phi}_{i} = 1 \tag{4-1}$$

where N expresses the number of service flows in the link. And the service volume is described by

$$g_i^{inc} = \frac{\phi_i}{\sum_{j \in B} \phi_j} B \tag{4-2}$$

where i, j denotes two different service flows. In GPS based algorithms, the bandwidth allocation of different service flows meets the requirement  $B_i/\phi_i = B_j/\phi_j$ , where  $B_i$  is the allocated bandwidth of the service flow i. By assigning a smaller weight  $\phi_{low}$  to an unimportant background service flow, the weight of service flow with high priority  $\phi_{high}$  is much larger than  $\phi_{low}$ , so that the majority of the bandwidth is accessed by high-priority service flows.

### 4.3.1 Algorithm Description

In buffer management algorithms, how to control the buffer space occupation is very important [38]. Here we define

$$\frac{C_i}{W_i} = \frac{C_j}{W_j} \tag{4-3}$$

where  $C_i$  is the buffer space occupation, and  $W_i$  expresses the synthetic weight of the service flow i. When the cache is full, the service flow with the largest value of  $C_i/W_i$  will be dropped in order to guarantee fairness. Here the fairness is reflected in packets with different queue length [39-40]. Assume that  $u_i$  is the weight, and  $v_i$  is the current queue length of the service flow i. The synthetic weight  $W_i$  can be calculated as described by

$$W_i = \alpha \times u_i + (1 - \alpha) \times v_i \tag{4-4}$$

where  $\alpha$  is the adjust parameter of the two weighting coefficients  $u_i$  and  $v_i$ . The parameter  $\alpha$  can be pre-assigned, or determined in accordance with usage of the cache. The weight  $u_i$  is related to the service flow itself, and different service flows are assigned with different weight values. As long as the service flow is active, this factor remains unchanged. But  $v_i$  is time varying, which reflects dropping situation of the current service flow.

Suppose a new packet *T* arrives, then the PAFD algorithm process is described as follows:

Step 1: Check whether the remaining cache space can accommodate the packet T, if the remaining space is more than or equal to the length of T, add T into the cache queue. Otherwise, drop some packets from the cache to free enough storage space. The

decision on which packet will be dropped is given in the following steps.

Step 2: Calculate the weighting coefficients u and v for each service flow, and the value of the parameter  $\alpha$ . Then find the values of new synthetic weights W for each flow according to (4-4).

Step 3: Choose the service flow with the largest weighted buffer space occupation  $(C_i/W_i)$ . If the service flow associated to the packet T has the same value as it, then drop T at the probability P and returns. Otherwise, drop the head packet of the service flow with the largest weighted buffer space occupation at probability 1-P, and add T into the cache queue. Here Probability P is a random number generated by the system to ensure the smoothness and stability of the process.

Step 4: Check whether the remaining space can accommodate another new packet, If the answer is yes, the packet will be transmitted into the cache. Otherwise, return to Step 3 to continuously choose and drop packets until there is sufficient space.

If all packet lengths are the same, the algorithm only needs one cycle to compare and select the service flow with the largest weighted buffer space occupation. Therefore, the time complexity of the algorithm is O(N). In this case, we also need additional 4N storage space to store the weights. Taking into account the limited capacity of wireless network, N is usually less than 100. So in general the algorithm's overhead on time and space complexity are not large. On the other hand, if packet lengths are different, then it is necessary to cycle Step 3 and Step 4 until the cache has enough space to accommodate the new packet. The largest cycling times is related to the ratio between the longest and

the shortest packets. At this moment, the time complexity overhead is still small based on practices.

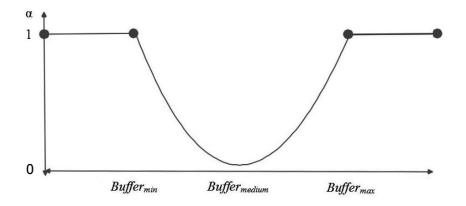

In Step 2,  $\alpha$ , a function of shared buffer, is a parameter for adjusting proportion of the two weighting coefficients u and v. For a large value of  $\alpha$ , the PAFD algorithm tends to fairly select and drops packets according to the synthetic weight W. Otherwise, the algorithm tends to select and drop the service flow with large queue length. A reasonable value for  $\alpha$  can be used to balance between fairness and performance. Here we introduce an adaptive method to determine the value of  $\alpha$  based on the congestion situation of the cache, and this process does not require manual intervention.

When there is a minor congestion, the congestion can be relieved by reducing the sending rate of a small number of service flows. The number of service flows in wireless network nodes is not as many as that in the wired network. So the minor congestion can be relieved by reducing the sending rate of any one of service flows. We hope this choice is fair, to ensure that all user access to the system resources according to their weights.

When there is a moderate congestion, the congestion cannot be relieved by reducing the sending rate of any one of service flows. Reducing the rate of different service flows will produce different results. We hope to reduce the rate of service flows which are most effective to the relief of congestion. That is, the service flow which current queue length is the longest (The time that these service flow occupied the cache is also the longest). This not only improves system throughput, but also made to speeds up the congestion relief.

When there is a severe congestion, it is obvious that reducing the sending rate of a small portion of the service flows cannot achieve the congestion relief. We may need to reduce the rate of a lot of service flows. Since the TCP has a characteristic of additive increase multiplicative decrease (AIMD), continuous drop packets from one service flow to reduce the sending rate would adversely affect the performance of the TCP flow. While the effect on relieving system congestion becomes smaller, we gradually increase the values of parameters, and the algorithm will choose service flows to drop packet fairly. On one hand, at this point the "fairness" can bring the same benefits as in the minor congestion system; on the other hand this is to avoid continuously dropping the longer queue service flow.

Congestion is measured by the system buffer space occupation rate.  $\alpha$  is a parameter relevant to system congestion status and its value is between 0 to 1. Assume that the current buffer space occupation rate is denoted by  $Buffer_{cur}$ , and  $Buffer_{medium}$ ,  $Buffer_{min}$ , and  $Buffer_{max}$  represent threshold value of the buffer space occupation rate for moderate, minor, and severe congestion, respectively.

When  $Buffer_{cur}$  is close to  $Buffer_{min}$ , the system enters a state of minor congestion. The system is in a state of severe congestion when  $Buffer_{cur}$  reaches  $Buffer_{max}$ . The value of  $\alpha$  can be determined by using linear approach, then the system will have a dramatic oscillation. Instead we use high order nonlinear or index reduction to get smooth curve of  $\alpha$  as shown in Figure 4-1.

Figure 4-1 An Adaptive Curve of Parameter α

The value of  $\alpha$  can be calculated from