# Florida International University FIU Digital Commons

Electrical and Computer Engineering Faculty Publications

College of Engineering and Computing

4-23-2014

# Reconfigurable and non-volatile vertical magnetic logic gates

J. Butler University of California, Riverside

M. Shachar University of California, Riverside

B. Lee University of California, Riverside

D. Garcia University of California, Riverside

B. Hu University of California, Riverside

See next page for additional authors

Follow this and additional works at: https://digitalcommons.fiu.edu/ece\_fac Part of the <u>Electrical and Computer Engineering Commons</u>

## **Recommended** Citation

Butler, J.; Shachar, M.; Lee, B.; Garcia, D.; Hu, B.; Hong, J.; Amos, N.; and Khizroev, Sakhrat, "Reconfigurable and non-volatile vertical magnetic logic gates" (2014). *Electrical and Computer Engineering Faculty Publications*. 39. https://digitalcommons.fu.edu/ece\_fac/39

This work is brought to you for free and open access by the College of Engineering and Computing at FIU Digital Commons. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Publications by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fu.edu.

### Authors

J. Butler, M. Shachar, B. Lee, D. Garcia, B. Hu, J. Hong, N. Amos, and Sakhrat Khizroev

## **Reconfigurable and non-volatile vertical magnetic logic gates**

J. Butler,<sup>1,a)</sup> M. Shachar,<sup>2</sup> B. Lee,<sup>1</sup> D. Garcia,<sup>2</sup> B. Hu,<sup>3</sup> J. Hong,<sup>4</sup> N. Amos,<sup>1,2</sup> and S. Khizroev<sup>1,5</sup>

<sup>1</sup>Electrical Engineering Department, University of California, Riverside, California 92504, USA

<sup>2</sup>Materials Science and Engineering Program, University of California, Riverside, California 92504, USA

<sup>3</sup>Computer Science and Engineering, University of California, Riverside, California 92504, USA

<sup>4</sup>Electrical and Computer Engineering, University of California, Berkeley, California 94720, USA

<sup>5</sup>Electrical and Computer Engineering, Florida International University, Miami, Florida 33174, USA

(Received 17 February 2014; accepted 14 April 2014; published online 23 April 2014)

In this paper, we discuss the concept and prototype fabrication of reconfigurable and non-volatile vertical magnetic logic gates. These gates consist of two input layers and a RESET layer. The RESET layer allows the structure to be used as either an AND or an OR gate, depending on its magnetization state. To prove this concept, the gates were fabricated using a multi-layered patterned magnetic media, in which three magnetic layers are stacked and exchange-decoupled via non-magnetic interlayers. We demonstrate the functionality of these logic gates by conducting atomic force microscopy and magnetic force microscopy (MFM) analysis of the multi-layered patterned magnetic media. The logic gates operation mechanism and fabrication feasibility are both validated by the MFM imaging results. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4873297]

#### I. INTRODUCTION

Today, like never before, the electronics industry is looking for an alternative to semiconductor technology. This is because current semiconductor technologies are approaching fundamental limitations.<sup>1</sup> The most promising alternative to current technologies is magnetic logic devices or some hybrid of magnetic and semiconductor technology, which would take the best of the two technologies. There are a number of key advantages to using magnetic devices: Fundamentally lower energy consumption, non-volatility, radiation hardness, ultra-high scalability,<sup>2,3</sup> and relatively high data rates. In this paper, we present an experimental study on magnetic logic gates/cells that can be used to construct purely magnetic devices or be integrated with current semiconductor technologies.

The idea of magnetic logic devices is not new. In the 1950s-1960s, research groups were already working on all-magnetic logic computing. At that time, their main advantage over transistors was that they were practically indestructible when compared to vacuum tubes. These devices were relatively large because they consisted of magnetic ferrite elements interconnected with copper wires. The logic state of the device was determined by the direction of magnetization, clockwise or counterclockwise. Due to the rapid advancements of integrated circuits, they were never able to keep up with transistor technologies.<sup>4,5</sup> Around the same time, other research groups proposed all-magnetic logic using magnetic thin films. Their research focused on domain tips (DOT) logic devices. In these devices, the domain tips were propagated through low coercivity force channels that were fabricated in magnetic films with high coercivity. There were three important properties that were utilized to create these devices: (1) Direction of domain tip propagation was dependent on the direction of the applied field, (2) the interactions between domain tips, and (3) domain tip speed of propagation.<sup>6-8</sup> This research can thus be considered a precursor to the domain wall logic that is being explored today.

Recently, there has been a renewed interest in magnetic logic computing. Current developments include work on magnetic domain wall logic,<sup>9</sup> combinations of magnetic and semiconductor logic,<sup>10</sup> and magnetic quantum-dot cellular automata.<sup>11–13</sup> These technologies are mainly based on longitudinal magnetic thin films. Nonetheless, not all research has been focused on longitudinal media. Some recent research on nanomagnetic logic implemented perpendicular magnetic thin films. One group successfully created a 1-bit full adder using perpendicular multi-layered magnetic media. The group used a focused ion beam of gallium atoms to partially irradiate the media to locally adjust its anisotropy. This created a nucleation center that was used to propagate the signal through the magnetic logic device.<sup>14,15</sup> Another group was able to fabricate stacked magnetic layers to generate a magnetic ratchet for logic applications.<sup>16</sup> They made use of antiferromagnetically coupled magnetic layers to shift a soliton from one layer to another. We propose a magnetic logic structure that relies on both perpendicular media and exchanged-decoupled magnetic layers. This way, each magnetic layer can be changed independently and not be affected by the other layers in the stack. Furthermore, since we adopted perpendicular magnetic media, we are able to make a stacked gate that is relatively smaller, hence gaining a crucial advantage over other similar technologies that use longitudinal media.

#### **II. CONCEPT**

Using Boolean algebra, it is possible to prove that any logic operation can be created with the three basic logic functions: NOT, AND, and OR.<sup>17</sup> It has been shown that the magnetic NOT gate can be created by two antiferromagnetically coupled

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: jbutl001@ucr.edu

cells being fabricated, therefore, it will not be discussed in this paper.<sup>8</sup> The logic gates/cells that will be discussed in this paper will consist of two inputs and a RESET. The purpose of the RESET is to determine if the gate will either be an AND gate or an OR gate. When the RESET is set to "0," the gate will work as an AND gate, and when the RESET is set to "1," it will function as an OR Gate. The truth table for such gates can be seen in Table I.

In order to implement the logic gates that are discussed above, we designed a three-layer magnetic media to demonstrate the logic operations. There are at least a couple of possible ways that this media could be used; both ways have advantages and disadvantages. One possibility is to fabricate it as a homogeneous media, such as that used in conventional perpendicular magnetic recording disks.<sup>18</sup> The main advantage of this is the low fabrication cost. Existing magnetic recording media fabrication facilities can be used for this type of media. The other possibility is to use a patterned media to implement these gates. In this case, each logic gate would be physically separated from its neighboring cells. Thus, the possibility of magnetic fields from one device affecting the state of another device is minimized. Also, another advantage of this fabrication method is that the devices can be packed more densely together than in the continuous media, allowing for a greater number of devices per unit area. In order to create the patterned media, some type of lithography will be necessary, such as x-ray lithography, e-beam lithography, imprint lithography, or ion-beam lithography. In this paper, our focus will be on the design and fabrication of the patterned media that can be used for such logic gates.

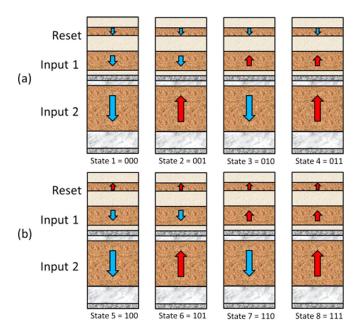

As described above each of the magnetic layers will act as either an input layer or a RESET layer for the vertical logic gate. The logic operations will be carried out by the interactions between the magnetic fields that are created by each of the layers, as seen in Figs. 1(a) and 1(b). Each of the layers needs to be magnetically "hard" so that the field created by one layer does not affect the magnetization of the other two layers. In order to be able to selectively change each layer/input individually without altering the state of the others layers, each layer must have a unique coercivity. Hence, the media is designed with a gradient of coercivity values (H<sub>C</sub>). The bottom layer ("Input 2") will have the lowest coercivity and the top layer ("Reset") will have the highest coercivity, such that:  $H_{C\_input2} < H_{C\_input1} < H_{C\_reset}$ . The "Reset" layer must have the highest value of coercivity so that its magnetization direction will not be changed when

TABLE I. Truth table for the reconfigurable AND/OR gate.

| GATE | STATE | RESET | Input 1 | Input 2 | Output |

|------|-------|-------|---------|---------|--------|

| AND  | 1     | 0     | 0       | 0       | 0      |

|      | 2     | 0     | 0       | 1       | 0      |

|      | 3     | 0     | 1       | 0       | 0      |

|      | 4     | 0     | 1       | 1       | 1      |

| OR   | 5     | 1     | 0       | 0       | 0      |

|      | 6     | 1     | 0       | 1       | 1      |

|      | 7     | 1     | 1       | 0       | 1      |

|      | 8     | 1     | 1       | 1       | 1      |

an input field is applied to the gate. The other important property of each layer is its magnetic moment. In order to distinguish the magnetic state of each layer during the read-back process, the magnetic media must be fabricated such that:  $m_{input2} > 2m_{input1} > 4m_{reset}$ , where *m* is the total magnetic moment of each layer.

Each of the magnetic layers will be designed to have perpendicular anisotropy, so they can be analogous to transistors. When the magnetization of the layer is in the "Up" direction, this will correspond to a binary "1" and when the magnetization is in the "Down" direction, this will correspond to a binary "0." The magnetization direction of the top RESET layer will determine if the stack will act as either an AND gate (Fig. 1(a)) or an OR gate (Fig. 1(b)), "0" and "1," respectively. For this study, the stacks will be fabricated to be square stacks that are 120 nm on a side and separated by 225 nm.

The main focus of this study is the theory and fabrication of 3D magnetic logic gate, but we will briefly describe methods for reading and writing to the inputs and reset layer. As will be shown in Sec. IV, the output of the logic gate can be read with an magnetic force microscopy (MFM) probe. Another method would be to utilize the read/write heads of a hard disk drive to polarize each layer in a certain direction and then read the net magnetization of the stack to determine the output of the logic operation. In addition, a patterned array of nanomagnets or magnetic quantum-dot cellular automata can also be implemented to transfer inputs and outputs between the gates.<sup>19</sup> The latter method would be the most useful, because it would allow our magnetic logic gates to be integrated into existing semiconductor technologies. The inputs of the gates will be set by the effect of spintorque transfer, in which a spin-polarized current is applied to set the direction of magnetization for each layer.<sup>20</sup> The output can be read using giant/tunneling magneto-resistive (TMR/GMR) sensors. The resistance of the output will

FIG. 1. (a) AND and (b) OR gates of the three-layer reconfigurable magnetic logic gate. The direction of the magnetization determines if the bits is a 1 or a 0. "Up" = 1 and "Down" = 0.

change depending on the net magnetization of the 3 magnetic layers of the stack.<sup>21</sup> The effects of MTJ have been extensively studied by a number of different groups.<sup>22–26</sup> Recently, there has been a study, by Tanaka *et al.*, into the possibility of using microwaves to selectively switch the magnetization in a three-layered stacked magnetic structure.<sup>27</sup> Through micromagnetic simulations, they were able to show that it is possible to individually switch the polarization of each layer. Although this research was conducted for uses in magnetic recording, it can be utilized to selectively switch each of the layers in our logic gates. These are just a few feasible methods that can be exploited to read and write information to the input and RESET layers.

#### **III. FABRICATION**

Many different compositions were tested in order to optimize the media for this particular application. Following this evaluation, we optimized a composition that provided the necessary magnetic properties for the logic gates to function properly. Co/Pt and Co/Pd multilayers were chosen for the magnetic layers. This is because it is possible to fine tune the values of coercivity and magnetic moment of these materials. It has been shown that these properties can be controlled by the deposition parameters, thickness of each layer, and the number of bi-layers that make up each magnetic layer.<sup>28</sup> The following is the selected composition:

$\begin{aligned} & \text{Substrate/Ti}(1.5 \text{ nm})/\text{Pt}(5 \text{ nm})/[\text{Co}(0.4 \text{ nm})/\text{Pt}(0.55 \text{ nm})] \\ & \times 14/\text{Pt}(1.5 \text{ nm})/\text{Ti}(1.5 \text{ nm})/\text{Pd}(1.5 \text{ nm})/ \quad [\text{Co}(0.25 \text{ nm})/\text{Pd}(0.55 \text{ nm})] \\ & \text{Pd}(0.55 \text{ nm})] \times 7/ \quad \text{Pd}(4.5 \text{ nm})/[\text{Co}(0.25 \text{ nm})/\text{Pd}(0.55 \text{ nm})] \\ & \times 3/\text{Pd}(3 \text{ nm})/\text{Ti}(4 \text{ nm}). \end{aligned}$

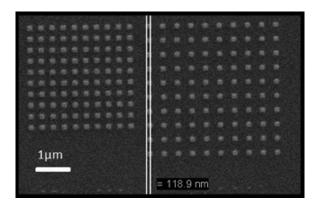

A number of processes were used to fabricate the media for this experiment: (1) The magnetic media was sputter deposited onto a Si substrate, (2) Hydrogen silsesquioxane (HSQ) was spin coated and then baked onto the top of the media, (3) E-Beam lithography to generate the patterns onto the HSQ, (4) development of the patterns, (5) inductively coupled plasma (ICP) etching of the oxidized Ti layer, (6) Ar-Ion milling of the media to transfer the patterns into the continuous media. A SEM image of the 120 nm diameter patterns can be seen in Figure 2. A more in-depth description of each of these processes is published elsewhere.<sup>29</sup> For this work, the coercivity of each patterned magnetic layer was estimated through MFM analysis. This is done by applying a range of magnetic fields to the media and then testing it after each exposure with MFM. Using this method, we were able to determine that the "Input 2" layer has a coercivity value 2.5 kOe, the "Input 1" layer is  $\sim$ 5.0 kOe, and the "Reset" layer is  $\sim$ 6.0 kOe.

#### IV. MAGNETIC FORCE MICROSCOPY (MFM) STUDY

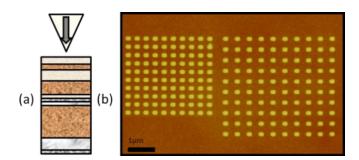

Since the focus of this paper is only the logic gate itself and not the input/output channels we will analyze the gates using MFM imaging. Although this is not how the gates will work in a device, the MFM study will give us insight on how the gates will perform once they are implemented at the device-level. The two properties that need to be taken into account for the MFM probe are the magnetic field strength and coercivity of the magnetic tip. The magnetic field strength of the tip should be high enough to differentiate the signals from the 3-layers logic cell, but not too high to switch their magnetization. The magnetic tip coercivity should be high enough such that the magnetic field emanating from the nanomagnetic cells would not switch the magnetization of the probe and cause difficulties in data interpretation. For this study, we used a PSENS<sup>TM</sup>MFM-UHC probe with tip coercivity of  $\sim 1$  T. The probe was magnetized by the manufacturer with  $\sim 3$  T along the tip central axis. For all the images that were taken, the magnetization direction of the probe was out of the apex of the tip (Figure 3(a)). Both atomic force microscopy (AFM) (Figure 3(b)) and MFM images were taken of the media. To make the analysis easier, we will only focus on the pattern on the left, in the SEM image in Figure 2.

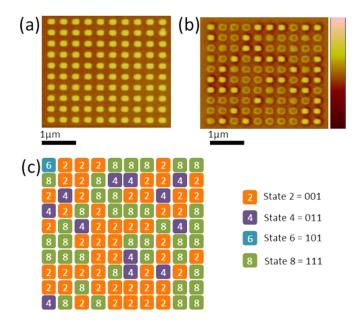

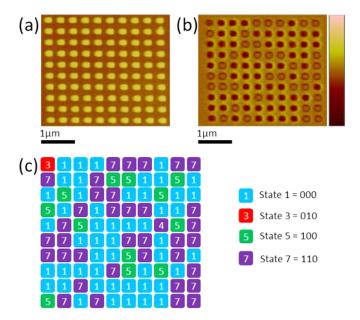

In order to view all eight of the possible states of this media with MFM, the two input layers needed to be randomized. To do this, the media was exposed to an oscillating and decaying magnetic field that started at 0.75 T and ended at 0.3 T. In order for the media to manifest the 8 possible input/reset combinations, the "Input 2" layer was polarized in the "Up" or "1" direction by exposing the media to a field of 0.3 T in the out-of-plane direction. The resulting MFM image can be seen in Figure 4(b). In Figure 4(c), each of the four possible states are highlighted in a different color and numbered, so they can easily be differentiated from each other.

FIG. 2. A SEM image of 120 nm diameter patterns.

FIG. 3. (a) Illustration of the direction of the magnetization of the probe with respect to the media. (b) An AFM image of the patterns that were used for the MFM study. The bits are 120 nm in diameter with different areal densities.

FIG. 4. (a) AFM image (b) MFM image of the 4 of the 8 possible input combinations. (c) An image created to highlight each of the individual four combinations with a different color and number, so that each one is easily distinguishable.

After this, the "Input 2" layer was magnetized in the "Down" or "0" direction by exposing the media to a field of  $\sim 0.3$  T into the plane of the media. The resulting MFM image can be seen in Figure 5(b). As before, in Figure 5(c), a color coded and numbered image of the each of the 4 input combinations can be seen. Both images were taken in the same location, over 120 nm diameter patterns, with the same probe, with the height and phase scales the same. So, from these results, we can see that it is possible to fabricate a reconfigurable logic gate that has two inputs and one RESET, which allows the gate to work as an AND gate or an

FIG. 5. (a) AFM image (b) MFM image of the other 4 possible input/reset combinations. (c) An image created to highlight each of the individual four combinations with a different color and number, so that each one is easily distinguishable.

or gate. From these two images, we are able to observe all 8 of the possible magnetic states from this media. We were able to verify that states 3 and 6 were distinct states by cross sectional analysis. The reason there is only one instance of each state is attributed to the complexity of achieving such states with our method of magnetizing the sample.

#### **V. CONCLUSION**

In conclusion, we were able to fabricate and test a vertical magnetic logic gate that can be reconfigured to act as either an AND or and OR gate. The output of these gates depends on the states of the two input layers and the one RESET layer. In order to build the gates with a gradient of coercivity values and magnetization, Co/Pd and Co/Pt multilayers were used. By varying the thickness and number of Co/Pd and Co/Pt pairs in each layer, we were able to precisely control the coercivity values and magnetic moment. We then used MFM to analyze the logic operations of the patterned media and to determine that all 8 magnetic states were observable in this media.

#### ACKNOWLEDGMENTS

We extend our gratitude to the National Science Foundation (NSF) under Contract Nos. 005084-002 and 0824019 and DARPA/Defense Microelectronics Activity (DMEA) under Agreement No. H94003-09-2-0904. We would also like to thank Dexter Humphrey and Dong Yan for their support.

- <sup>1</sup>P. S. Peercy, Nature **406**, 1023 (2000).

- <sup>2</sup>R. P. Cowburn, Science **311**, 183 (2006).

- <sup>3</sup>B. Lee, J. Hong, N. Amos, I. Dumer, D. Litvinov, and S. Khizroev, J. Nanopart. Res. **15**, 1665 (2013).

- <sup>4</sup>U. F. Gianola, J. Appl. Phys. **32**, 27S (1961).

- <sup>5</sup>D. R. Bennion, H. D. Crane, and D. Nitzan, *Digital Magnetic Logic* (McGraw-Hill, New York, 1969).

- <sup>6</sup>R. J. Spain, J. Appl. Phys. **37**, 2572 (1966).

- <sup>7</sup>R. J. Spain, J. Appl. Phys. **37**, 2584 (1966).

- <sup>8</sup>R. J. Spain, H. I. Jauvtis, and F. T. Duben, in *National Computer Conference and Exposition, New York, USA, 6–10 May* (ACM, 1974), pp. 841–846.

- <sup>9</sup>D. A. Allwood, G. Xiong, C. C. Faulkner, D. Atkinson, D. Petit, and R. P. Cowburn, Science **309**, 1688 (2005).

- <sup>10</sup>S. Joo, T. Kim, S. H. Shin, J. Y. Lim, J. Hong, J. D. Song, J. Chang, H.-W. Lee, K. Rhie, S. H. Han, K.-H. Shin, and M. Johnson, *Nature* **494**, 72 (2013).

- <sup>11</sup>A. Imre, G. Csaba, L. Ji, A. Orlov, G. H. Bernstein, and W. Porod, Science **311**, 205 (2006).

- <sup>12</sup>M. T. Niemier, X. S. Hu, M. Alam, G. Bernstein, W. Porod, M. Putney, and J. DeAngelis, in ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), Portland, Oregon, USA, 27–29 August 2007 (ACM, 2007), pp. 26–31.

- <sup>13</sup>T. Windbacher, O. Triebl, D. Osintsev, A. Makarov, V. Sverdlov, and S. Selberherr, Microelectron. Eng. **112**, 188 (2013).

- <sup>14</sup>I. Eichwald, J. Kiermaier, S. Breitkreutz, J. Wu, G. Csaba, D. Schmitt-Landsiedel, and M. Becherer, IEEE Trans. Magn. 49, 4468 (2013).

- <sup>15</sup>S. Breitkreutz, J. Kiermaier, I. Eichwald, C. Hildbrand, G. Csaba, D. Schmitt-Landsiedel, and M. Becherer, IEEE Trans. Magn. **49**, 4464 (2013).

- <sup>16</sup>R. Lavrijsen, J. Lee, A. Fernandez-Pacheco, D. C. M. C. Petit, R. Mansell, and R. P. Cowburn, Nature **493**, 647 (2013).

- <sup>17</sup>J. Gregg, Ones And Zeros: Understanding Boolean Algebra, Digital Circuits, and the Logic of Sets (John Wiley & Sons, Hoboken, NJ, 1998).

- <sup>18</sup>E. D. Daniel and C. D. Mee, *Magnetic Recording* (McGraw-Hill Professional, New York, 1996).

- <sup>19</sup>D. A. Allwood, G. Xiong, M. D. Cooke, C. C. Faulkner, D. Atkinson, N. Vernier, and R. P. Cowburn, Science 296, 2003 (2002).

- <sup>20</sup>J. C. Slonczewski, J. Magn. Magn. Mater. **159**, L1 (1996).

- <sup>21</sup>M. N. Baibich, J. M. Broto, A. Fert, F. N. Van Dau, F. Petroff, P. Etienne, G. Creuzet, A. Friederich, and J. Chazelas, Phys. Rev. Lett. **61**, 2472 (1988).

- <sup>22</sup>Chunsheng E, J. Rantschler, S. Khizroev, and D. Litvinov, J. Appl. Phys. 104, 054311 (2008).

- <sup>23</sup>A. Orlov, A. Imre, G. Csaba, L. Ji, W. Porod, and G. H. Bernstein, J. Nanoelectron. Optoelectron. 3, 55 (2008).

- <sup>24</sup>D. C. Ralph and M. D. Stiles, J. Magn. Magn. Mater. **320**, 1190 (2008).

- <sup>25</sup>S. Liu, X. S. Hu, M. T. Niemier, J. J. Nahas, G. Csaba, G. H. Bernstein, and W. Porod, IEEE Trans. Nanotechnol. **12**, 203 (2013).

- <sup>26</sup>H. Mahmoudi, T. Windbacher, V. Sverdlov, and S. Selberherr, IEEE Trans. Magn. 49, 5620 (2013).

- <sup>27</sup>T. Tanaka, Y. Otsuka, Y. Furomoto, K. Matsuyama, and Y. Nozaki, J. Appl. Phys. **113**, 143908 (2013).

- <sup>28</sup>B. Hu, N. Amos, Y. Tian, J. Butler, D. Litvinov, and S. Khizroev, J. Appl. Phys. **109**, 034314 (2011).

- <sup>29</sup>N. Amos, J. Butler, B. Lee, M. H. Shachar, B. Hu, Y. Tian, J. Hong, D. Garcia, R. M. Ikkawi, R. C. Haddon, D. Litvinov, and S. Khizroev, PLoS One 7, e40134 (2012).